一种高温动态老化测试的信号驱动板设计与实现

陆晓峰★,陶知,林凡淼,刘鑫

(中国电子科技集团公司第五十八研究所,江苏 无锡 214072)

0 引言

老化测试是剔除早期故障集成电路的有效方法,一般集成电路的早期故障期从几天到几个月不等,老化测试通过升温、增加压力、提高电压或加载动态信号等方法模拟极端的工作条件,可以将早期故障期缩短到几天甚至几小时之内[1]。高温动态老化就是在高温环境下对器件输入各种信号来模拟其工作状态,同时在输出端检测输出信号的正确与否来达到筛选器件的目的[2]。文献[3]和[4]中采用的传统高温动态老化信号驱动板系统,一般包括嵌入式系统、图形发生与监测模块(FPGA)、信号驱动板(CPLD、电平转换等)与通信接口等,实现了系统软硬件的可配置,能够满足大多数用户对集成电路高温老化测试的要求[3-4]。但是整个驱动板系统的构成较为复杂,涉及多个子系统与分模块,软件系统联调联试较为复杂与繁琐,并且搭建多个这样的测试系统周期较长、成本较高,通用性也较差,尤其在小批量、高复杂度、多样化的测试需求下,这些问题将尤为突出。本文以FPGA为核心,简化整个高温动态老化测试信号驱动板系统,设计了一种信号驱动板,具备很好的通用性和扩展性,可满足多种类的集成电路芯片老化测试需求。

1 信号驱动板设计

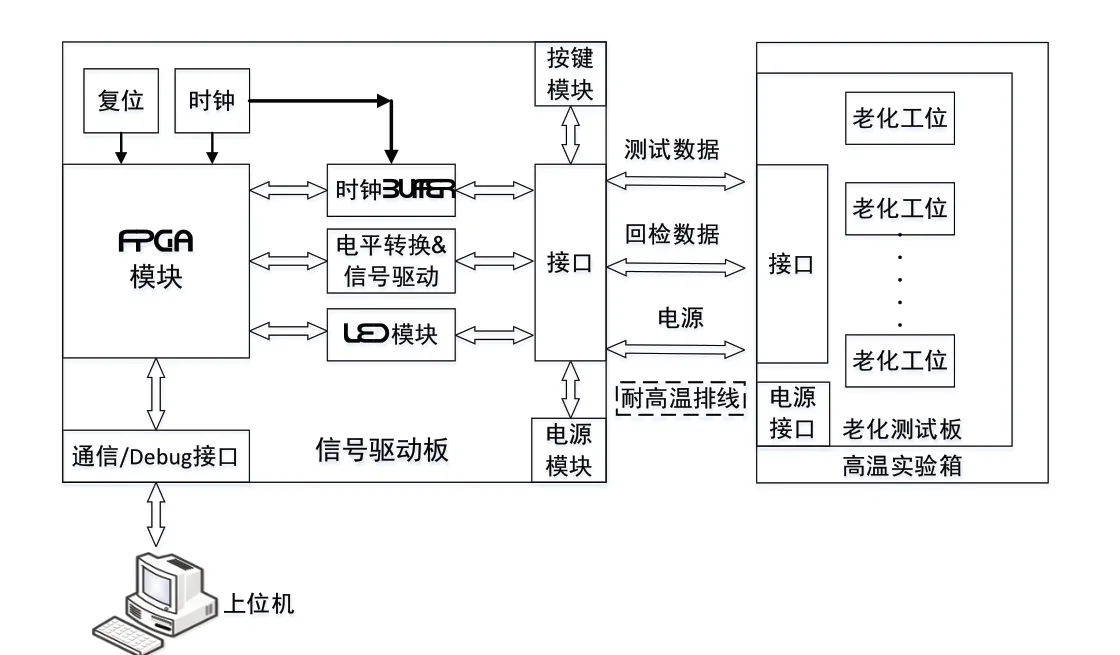

根据高温动态老化测试需求,本文设计的信号驱动板主要包括以下几个部分:FPGA模块、时钟Buffer模块、电平转换与信号驱动模块、LED模块、通信与Debug接口、电源模块以及按键模块等。信号驱动板通过耐高温排线与放置于高温实验箱内的老化测试板相连接,将测试信号加载到老化测试板上各待测器件管脚,同时在老化过程中对器件的反馈信号进行回检,通过配置LED模块中LED的闪烁、亮或不亮来表示老化测试的进程、正常或者异常等结果。整个老化测试系统架构图如图1所示。

图1 老化测试系统架构图

1.1 FPGA模块设计

经过大量调研之后本文采用一款基于XilinxArtix-7系列X C 7 A100 T-2 F G G 484I的高端核心板,其具有512M/1GByte DDR3,256Mbit NORFLASH,101440个逻辑单元数和8个GTP资源,采用高速防反插B2B连接器,尺寸仅70mmÍ50mm,由专业的PCB Layout可保证信号完整性。FPGA核心板对外有JTAG接口,可以用来下载或者Debug程序,也可使用UART串口与上位机进行通信。

采用FPGA核心板方案相比FPGA单芯片方案具备很大优势,首先FPGA对供电要求较高,需要搭建较多的外围电路,设计较为复杂且难度较高(信号一致性与完整性等),再结合BGA封装的贴装费用等,导致采用FPGA单芯片设计方案的成本、开发周期等远超采用FPGA核心板方案。

1.2 电平转换与信号驱动模块设计

为了适用于多种具有不同电平信号器件的高温动态老化需求,需要在信号驱动板上实现不同电平信号之间的转换匹配。同时由于老化测试时信号驱动板是通过长度约为120cm的耐高温排线与老化测试板进行连接,为了保证信号的长距离传输,还必须考虑信号的驱动能力。

本文采用TI公司的具有三态输出的8/16位2.5V至3.3V或3.3V至5V,同时又具备±24mA驱动输出的电平转换收发器SN74ALVC164245,默认为16位、同向设置,同时预留双8位、反向设计,由于FPGA核心板I/O电平已设定成3.3V,故预留3.3V至5V的电平转换。采用此具备了电流驱动能力的电平转换收发器可以简化驱动板系统设计、降低成本,同时又能满足使用需求。

1.3 时钟Buffer模块设计

为了增强信号驱动板的通用性与适用性,设计了时钟Buffer模块,使其能够适用于PCI-E接口功能器件的高温动态老化测试。时钟Buffer模块的参考时钟源可以选用差分晶振100M或者FPGA核心板的GTP差分时钟,根据实际需求通过选焊电阻进行切换,时钟Buffer模块的输出直接引至信号驱动板接口,通过耐高温排线即可为老化测试板提供差分时钟信号。

1.4 LED与按键模块设计

高温动态老化测试中老化测试系统要能够体现老化测试过程和结果以便测试人员进行及时地判断与干预。传统的监控方法有使用示波器或者逻辑分析仪对测试与反馈信号进行波形检测,又或者通过观测和记录系统运行电流来实现测试过程和结果的监管。这些传统的监控方法大大增加了老化测试的难度和操作的复杂度,测试效率低下,同时精度也无法保证。本文设计通过对信号驱动板输出信号与老化测试板反馈信号进行配置设定,使用LED通过其闪烁频率、亮、不亮等不同的显示方式来实现对老化测试过程和结果的监控。针对反馈信号本文设计了两种不同的连接方式:一种为反馈信号直接连接至LED的直连方式;另外一种为反馈信号先经FPGA信号处理后再映射连接至LED的间接方式。由于FPGA的I/O资源有限且需要优化利用,后者连接方式仅用于待测器件中某些需要FPGA做相应处理的关键信号,比如复位状态指示信号、系统时钟反馈信号等。

老化测试过程中还需要对待测器件的某些信号进行单独手动干预,比如复位信号等,因此信号驱动板上设计了个按键模块,其控制的信号均连接至接口上,届时可以用来给老化测试板提供单独干预信号。

1.5 电源模块设计

由于采用的FPGA核心板已经集成了电源转换等外围器件,无需再提供多路不同的电压给FPGA供电,所以信号驱动板的整个电源系统设计可以大为简化。由于FPGA核心板只需DC 12V即可,因此信号驱动板采用DC 12V作为输入电压,采用两个DC-DC模块将12V输入分别转换成其他模块工作所需的3.3V和5V两种电压。DC-DC采用TI公司的PTH12050W,输出电流最大可达6A,转换效率高达93%,输出电压值在1.2V-5.5V之间通过电阻可配置。同时还预留了一片型号为TPS75501的LDO,其最大输出电流为5A,转换效率90%以上,通过此LDO将5V电压转换成1.2V。

同时,以上12V输入经降压生成的5V、3.3V和1.2V三种电压均接至信号驱动板的接口上,当老化测试板运行功耗不高的情况下,可由信号驱动板直接供电,可大大减少测试所需线缆,简化测试系统以及降低成本[5]。

1.6 PCB设计

以上所述各个模块以及相应外围电路,经过合理设计与布局在一个PCB板上,为避免众多耐高温排线干涉或者遮挡PCB表面的按键和LED指示灯,更为了方便与老化测试板相连,信号驱动板所用的DB37接口全部布局在PCB板四周。

2 信号驱动板验证

本文采用某型桥片来进行信号驱动板的功能验证,参照如图1所示老化测试系统,搭建了如图2所示的功能验证系统。该型桥片只需在老化测试过程中由外部输入一组时钟与数据信号,其余信号可以通过设计老化测试板实现芯片与芯片间对应功能的引脚互联对接即可实现动态老化测试,可简化验证过程。同时该桥片的GPIO还可以定义成回检信号反馈给信号驱动板,通过配置LED模块的不同显示效果来实现老化过程的监控以及结果的判定。

图2 功能验证系统

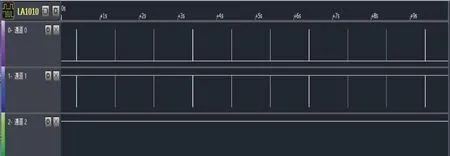

为进一步确认验证过程,本文还利用了逻辑分析仪分别去捕捉老化测试板上接收的测试数据和信号驱动板上接收回检数据的I/O口波形数据,如图3所示。从图3可知,信号驱动板可以正常输出测试信号和接收回检信号,表明该芯片老化测试过程正常且未失效,也说明该信号驱动板达到了预期功能,符合设计要求。

图3 老化测试信号图

3 结语

本文选用FPGA核心板作为信号驱动板的主控制芯片,设计了LED显示模块实现了对测试数据和回检数据的实时监控,以便测试人员及时地判断与干预;通过灵活设计,简化了外围子各系统,极大降低了测试系统的复杂度与成本,缩短了软硬件的开发和调试周期;同时利用FPGA核心板丰富的逻辑资源和灵活的可配置性,即可满足某一型号器件多工位同时进行老化的需求,又能通过修改配置适用不同器件的老化测试需求,可重复使用,通用性好,显著降低了测试成本和测试周期,即可以轻松实现“一板多用”,真正达到降本增效的目的。通过软硬件验证表明,该信号驱动板设计符合需求、达到预期功能,并且已成功运用于某型芯片的动态老化测试。