基于FPGA技术的交通灯的设计与实现

刘静

(云南机电职业技术学院,云南 昆明 650203)

0 引言

交通灯是现代交通控制中不可或缺的重要工具,目前实现交通灯控制的技术较为成熟,设计研究方案有多种[2]。本文将采用FPGA技术实现交通灯的控制。FPGA全称为现场可编程门阵列(Field Programmable Gate Arrays)。它可以根据用户自身的需求改变配置信息,从而定义其功能[1]。FPGA技术与传统的数字电子设计技术相比有明显的优势,主要表现在设计灵活,可靠性高,工作速度快等方面。本次利用verilog硬件描述语言对项目中的每个模块进行代码编写,并在Quartus II中进行编译,利用modelsim软件进行仿真。

1 设计原理

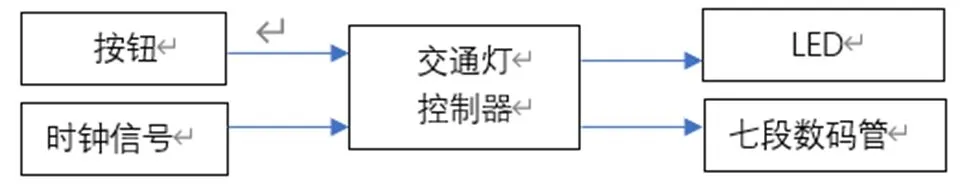

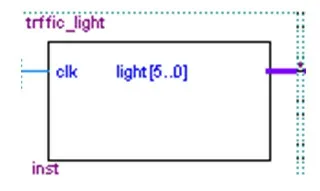

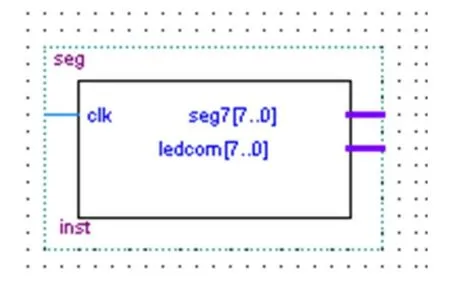

通过前期对交通灯的功能进行分析,结合FPGA的特点,交通灯控制系统的输入信号设为一个复位按钮和一个时钟信号,输出信号在LED和七段数码管上显示,其中6个LED分别用来表示南北和东西道路上的红、黄、绿灯,七段数码管用来显示变灯前的倒计时。结构框图和模块符号分别如图1、图2所示。

图1 结构框图

图2 模块符号1

交通灯控制器由分频器、计数器、控制器和译码器组成。本系统的时钟信号由试验箱中的晶振产生,晶振频率为50MHz。交通灯的所需的时钟频率为1MHz,所以首先要对外部时钟信号进行分频。由计时器对交通灯的时间(秒)进行计时。计时模块采用倒计时方式,当绿灯亮时(以南北方向为例)计时器从30开始倒计时,每来一个时钟信号就减1。当计时减到5时,发出熄灭绿灯、点亮黄灯的信号。七段数码管用于显示计时器的输出信号。

2 设计方法及实现

本系统由分频器模块、计时器模块、控制器模块和译码器模块组成[3]。

2.1 分频器模块的设计与实现

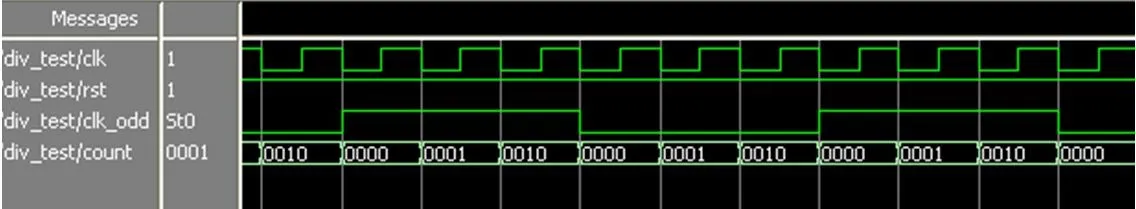

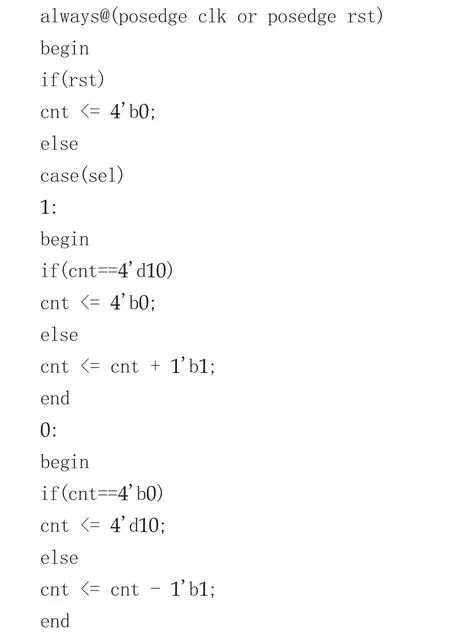

分频器是FPGA设计中使用频率非常高的基本单元之一。分频一般分为奇数倍分频和偶数倍分频器,本次使用的是偶数倍分频。偶数倍分频的实现非常简单,通过计数器就可以实现。例如进行N倍偶数分频,可以通过对时钟信号进行计数,当计数器计到N/2-1时,对输出信号进行翻转、计数器复位。如此循环,就可以实现分频[4]。为了便于观察,以6分频为例,部分程序和功能仿真波形图如下。

图3 功能仿真波形图1

2.2 计时器模块的设计与实现

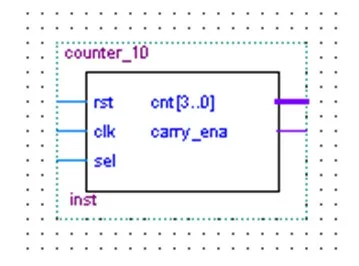

计时器通过计数来实现。计数是一种基本的运算,计数器就是实现这种运算的逻辑电路,计数器在数字系统中主要是对脉冲的个数进行计数,以实现测量和计数的功能。本设计首先对计数输出信号置为30,每来一个时钟脉冲就减1,当减到5时,发出熄灭绿灯、点亮黄灯的信号。当减到0时,重新从30开始倒计时。以十进制加减计数器为例,模块符号如图4所示。

图4 模块符号2

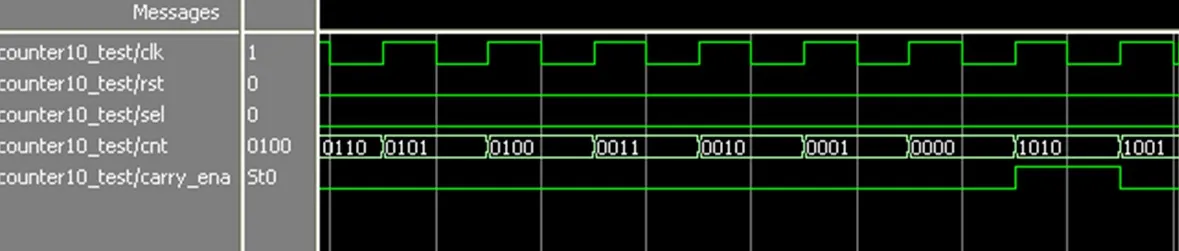

当sel为1时,可实现加法计数器功能;当sel为0时,可实现减法计数器功能,carry_ena为向高位的进位。部分程序和功能仿真波形图如下。

图5 功能仿真波形图2

2.3 控制器模块的设计与实现

控制器模块采用状态机实现。通过分析交通灯的工作过程,可以将其分为5个状态。S1:南北方向绿灯亮,东西方向红灯亮,持续时间25s;S2:南北方向黄灯亮,东西方向红灯亮,持续时间5s;S3:南北方向红灯亮,东西方向绿灯亮,持续时间25s;S4:南北方向红灯亮,东西方向黄灯亮,持续时间5s;S5:特殊情况[5]。

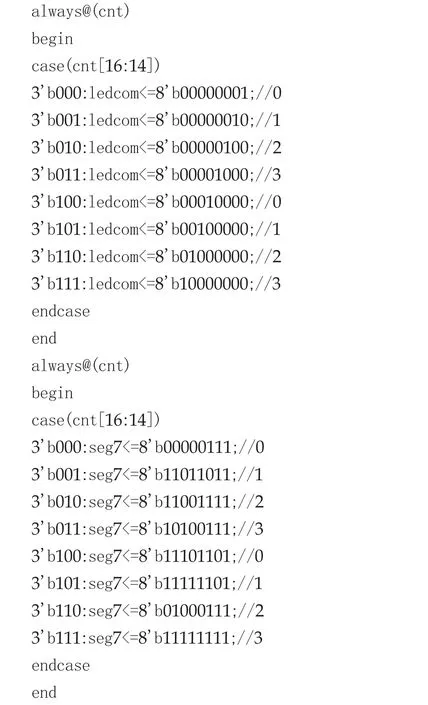

2.4 译码器模块的设计与实现

使用七段数码管来显示倒计时,其中,Ledcom是位选,用来选择让哪个数码管亮,seg7是段选(共阴极,高电平点亮),通过送字形码来决定显示什么数字。部分程序和模块符号如下。

图6 模块符号3

3 结语

本设计以FPGA实验箱中EP2C35F672C8芯片为开发平台,通过模块化编程完成对交通灯系统的设计,应用Quartus II软件和modelsim软件完成程序的设计和仿真,最终系统的仿真结果和实验结果满足系统要求,达到预期效果。同时,运用FPGA技术缩短了开发周期,提高了设计效率。