基于复用的数字集成电路设计关键技术研究

陆俊峰

(安徽芯纪元科技有限公司 安徽省合肥市 230088)

按照摩尔定理预测,集成电路制造技术飞快发展促发集成电路设计进一步发展,设计自动化的研究越来越受关注。在电路设计过程中出现的低成品率、低可循环利用率低以及高设计成本等问题日渐凸显。更进一步讲在正向和逆向分析的应用中,集成电路规律性的意义和作用越来越大。规律性提取是人类在认识、改造自然环境的实践活动中形成的提炼性和总结性的经验。设计自动化实现的研究和探索中,将规律性提取作为其基本研究手段被逐步采纳和推广,并作为关键核心技术应用到下一代工具的研发中去。规律性思维在当前并未在芯片设计研发中得以广泛普遍应用,但是在成品率提升上有很大的促进作用。尤其在涉及门级电路自动化分析有效性等的实现,已获得各方广泛认可。在集成电路的设计中,规律性思维的引用势必会引起新的思想、方法和工具的革新。

1 数字集成电路中的复用技术

复用技术基于综合多路信道,在传输路径上通过恢复原机制或解除终端各信道。复用技术在数据传输过程中使得信道传输效率不断提高,且应用广泛。数字集成电路诞生之日起,复用技术就与之有着千丝万缕的紧密关联。集成电路规模的的变革都受到复用技术的深刻影响。在数字继承电路设计过程中,复用技术推进从全定制向半定制化转变。与此同时,重复使用各种存储模块RAM、ROM 等存储单元,最大限度满足不同规模的存储模块。在数字集成电路开发过程中,门电路、FPGA 等重复使用各种等LE(logic Elements),价格昂贵的流片且漫长的周期都可以避免,而且能够准确地验证设计思想是否可行。总而言之,在数字集成电路的研发过程中,复用技术的应用将推进集成电路设计实现根本性的革新。随着SOC、SOPC、ASIP 技术推陈出新,给数字继承电路的设计思想带来全新活力。技术变革的同时,复用技术也得以更加彻底应用。技术革新满足不同领域对的MCU 差异性与多样化需求。当数据汇总中发现,某几条特定的指令被重复使用的频率高,则可实现对相应的指令进行融合,化为一条,并确保硬件相匹配。与此同时对未使用的指令进行裁剪,使得形成专用指令集处理器(ASIP)来满足数字继承电路设计与开发。

作为数字集成电路设计中的重要趋势之一,SOC 融合软硬件协同设计、IP 核复用和超深亚微米为技术等,。在数字继承电路设计中以采用不同的设计方法学来解决研发过程遇到设计的瓶颈和难题。复用技术在数字集成电路设计中,软硬件协同设计、IP 核复用和超深亚微米设计等也为其带来新的难题和挑战,而复用技术成为解决这些难题的重要手段和方法。复用技术能够在数字集成电路规律性提取中各个环节发挥重要作用,比如在涉及的逻辑综合、布图、制造、测试及集成电路分析阶段等各个环节。需要注意的是数字集成电路规律性提取工具在当前发展中相对缺乏,成为制约整个集成电路产业的瓶颈。集成电路规律性提取工具的需求是巨大的。

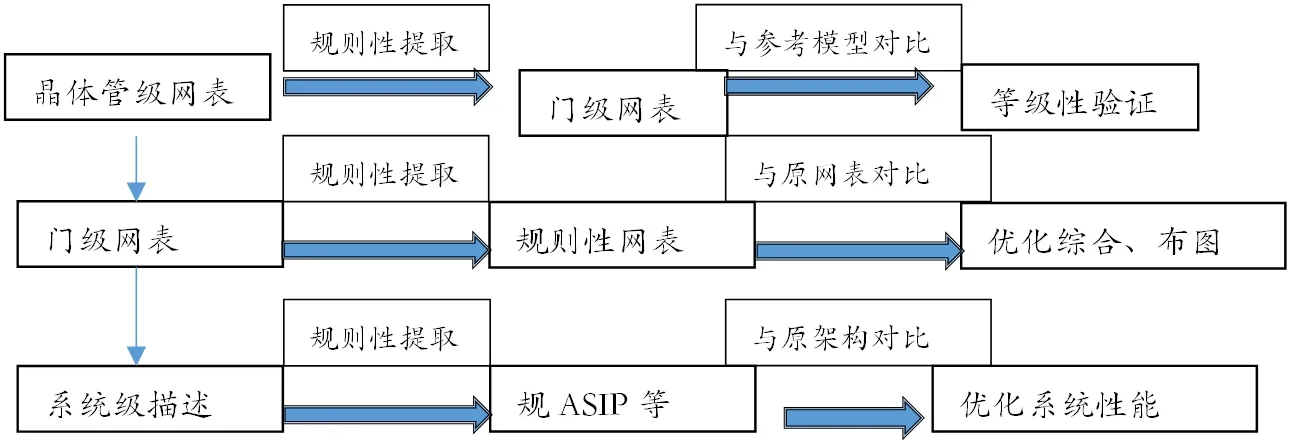

图1:复用计数在芯片设计不同阶段的作用

2 复用的数字集成电路设计关键技术

按照集成电路设计的不同阶段划分,通过晶体管级、门级及系统级等三个不同的设计层次,可对集成电路的复用技术进行分析。

2.1 基于复用技术SOC设计

SOC 具有高集成度和复杂度的特点,使其在时代发展中遇到的问题增多。传统的电路设计思想和方法已难满足实际发展需要。复用技术在SOC 设计中的应用本质上是提取设计中经常重复使用的功能、结构甚至方法,并最后创新性地转化为不同形式,来推进SOC 设计的不断优化和实现其效果最大化。在SOC 设计的各个阶段复用技术所发挥的重要作用是显而易见的。比如,在对晶体管级的电路网表实行重复性结构提取,能够掌握对门级的电路有系统描述。

如图1所示,复用技术在芯片设计的不同环节和阶段所呈现的作用显著。

2.2 晶体管级复用

随着数字集成电路技术突飞猛进,从面积上看,芯片面积飞速扩大,但是并不意味着单位面积上的晶体管数量会降低,反而呈现激增趋势。这就客观导致芯片的制造和测试成本成提升,经济性问题成为芯片开发过程中不得不面对的问题。为此,在芯片的物理设计环节上,版图自动化分析变得尤为关键。传统的版图主要涉及DRC、LVS 以及参数提取工具等三大类工具。LVS 作为晶体管级的子电路提取问题的关键,而集成电路提取问题需要综合考虑该标电路中是否含有指定功能或结构模块,并对相应的模块的数量和位置予以明确。

2.3 门级复用

集成电路的构成是由若干个错综复杂的抽象层次构成,因此摆在从晶体管级到门级的提取和从门级到功能模块级的提取成为制约电路提取的核心问题之一。按照当前数字集成电路研究现状,从晶体管级到门级的子电路提取算法研究较为成熟,有系统成熟的模型可供借鉴利用,目前市面上很多商用的软件都能应用到工程日常工作中来。然而,从门级到功能模块级的子电路提取问题成为芯片开发过程中的“老大难”问题。门级到功能模块级的子电路提取算法又被看成是集成电路规律性提取算法。在当前数字集成电路涉及中,它将整体性、布局性、综合性等不同阶段把规律性设计的思想引入。通过门级复用技术的引入,能够对于电路性能的提升、芯片设计复杂性降低以及芯片的成品率提高等都能带来积极的作用。

2.4 系统级复用

按照常规情况来看,按照流程来划分,数字集成电路的的设计优化需要从较高层次的优化开始,其优化效果会越发明显。以低功耗优化案例来论证这一结论。在系统级模块中,IP 复用技术是相对成熟的,其在SOC 设计中发挥的作用显著。抛开其优势,需要辩证地分析IP 复用自身存在的的局限性。IP 复用技术只能够在原有的成熟的IP 上进行修改、扩展,并不能根据实际需要展开随意的剪裁、配置甚至扩展,其所耗费的时间和精力成本与开发一套新的程序成本相近。这就极大地限制了IP复用在实际应用中的普及推广。

2.5 频繁模式复用与集成电路分析

数字集成电路的复用技术除了在传统的SOC 设计中进行广泛应用,其集成电路的反向分析的作用意义也非常重大。集成电路反向分析目前仅能靠人工分析来完成,自动化程度与数字化程度普遍较低,人工进行反向分析效率低且误差较大,进而对集成电路行业发展产生不同程度的负面影响。随着从门级到功能模块级的分析整理成为整个反向分析需求不断增加,与此同时,芯片规模不断扩大,其成本不断加大的不利背景下,自动化工具的引入和应用在数字进程电路设计的需求日渐迫切,也成为制约集成电路快速发展的重要症结。为了从拓扑结构上更好地理解和掌握对门级数字集成电路,需要重点聚焦电路中等效结构和等效功能提取算法,最终可以顺利完成自动的提取候选子电路工作。

3 复用技术在数字集成电路设计中的创新应用

在复用技术引入数字集成电路设计中来,需要将数据挖掘的思想引入集成电路规律性提取中来,解决传统规律性提取中存在的瓶颈和问题。

3.1 构建接口电路的可定制可复用架构

按照接口控制电路通用结构特性,接口控制部分、数据通路部分及传输控制部分的接口电路,可以按照一定的设计原理,将其设置成可复用架构。该构架一旦搭建完成,便可在CF 卡及MMC 卡等接口控制器核的设计进行广泛应用,可最大限度对构架进行复用。在设计中进行可配置性与参数化优化,解决用户所面临的需求问题,并从设计优化的方案中,提升用户使用体验和满意度。与此同时,在构建接口电路的可定制可复用架构过程中,可根据用户自身实际需要选择适配的配置,剪裁、定制IP 核的功能可以灵活应用。

3.2 构建二同构电路提取模型

二同构模型能够很好地解决传统大规模集成电路中根节点存在的空间过大的瓶颈。在优化设计中按照模板自动生成与同构子电路提取相分离的特性,提供统一的数字化表征方法来解决门级集成电路规律性提取中出现的多种结构的模板问题。对比原有的算法,采用二同构电路提取模型,不同形状模板的表征能力可以获得不同程度的拓展,并将频繁边作为模板的基本元素,从而使得规律性提取时一些不必要的操作可以避免出现,最大限度增强设计的可重用性和灵活性。

3.3 构建数字集成电路频繁模式的预提取方法

在集成电路频繁模式的提取中将数据挖掘的思想系统引入,建立起可通过控制最小支持度阈值来改变频繁子电路提取结果的规律性提取流程。该设计方法充分充分考虑到,当与频繁子电路规模增大,但是所有根节点集合迅速减小的特性,利用二同构模型对小规模电路结构进行数字化表征,使得算法运行效率有很大提高。与此同时,该方法在在提高频繁子电路的提取效率上有很大作用。

复用技术在数字集成电路中普遍应用,尤其是功能规则性的自动化提取引发的高关注,使得其成为数字集成电路设计核心技术之一。尤其是复用技术在SOC 设计中的应用,系统级和基本电路结构的深入研究,集成电路逆向分析自动化等问题已经被广泛关注。数字集成电路规律性提取算法必须坚持从其固有的复杂性实际出发,以SOC 设计环节中可优化的实际性问题入手,进行不断的创新与拓展。在新的技术更新背景下,要实现集成电路规律性提取的自动化,就需要有效降低搜索空间和提高算法的搜索效率。今后,要努力在搜索速度提升与结果质量之间达成一种平衡,推进复用技术在数字集成电路设计中有突破性进展。