用于电源SiP的半桥MOSFET集成方案研究

唐光庆 曾鑫 冯志斌 康丙寅

摘要:系统级封装(SysteminPackage,SiP)设计理念是实现电源小型化的有效方法之一。然而,SiP空间有限,功率开关MOSFET的集成封装方案对电源性能影响大。本文讨论同步开关电源拓扑中的半桥MOSFET的不同布局方法,包括基板表面平铺、腔体设计、3D堆叠等;以及不同的电源互连方式,包括键合、铜片夹扣等。从封装尺寸、载流能力、热阻、工艺复杂度、组装维修等方面,对比了不同方案的优缺点,为电源SiP的设计提供参考。

关键词:系统级封装;腔体;3D堆叠;键合;铜片夹扣

0引言

随着电子技术的快速发展和终端应用场景更加苛刻,小型化电源的需求越来越迫切。实现小型化的有效方法之一是采用系统级封装(System in Package,SiP)设计。其理念是采用裸芯片,通过多芯片组装,最终形成具有完整电源功能的封装产品。相较基于分立封装器件的电源产品,电源SiP的基板面积降至10%~20%,在性能、成本等方面也具有优势[1]。

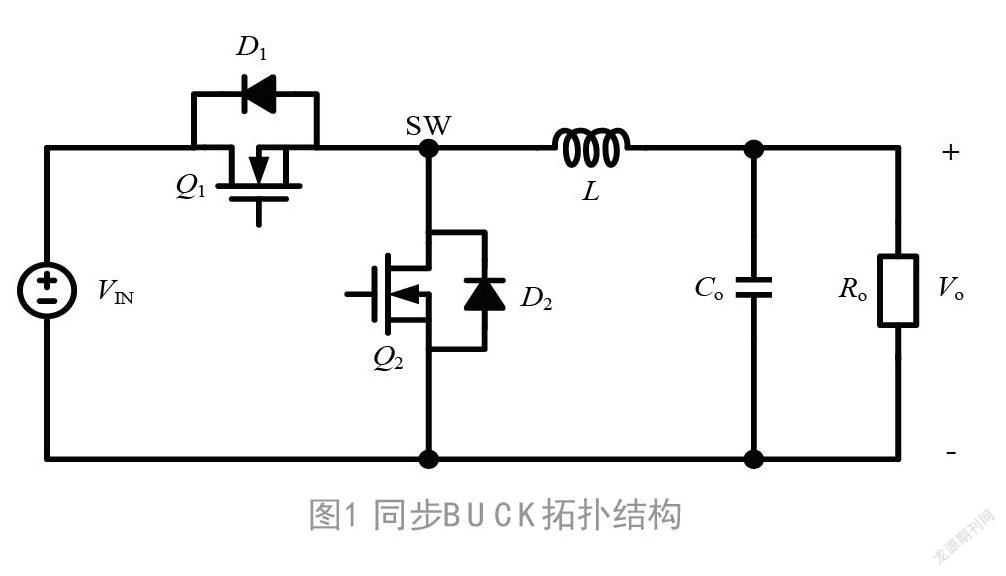

为提高大功率电源SiP效率,一般将传统开关电源拓扑中的续流二极管同步MOSFET取代形成如图1所示的同步开关电源拓扑,2个MOSFETQ1和Q2形成半桥结构。MOSFET是影响电源效率、热环境等性能的关键器件[2]。因此,半桥MOSFET的集成方案需要全面论证,以满足SiP封装尺寸、载流能力、热阻、工艺、组装维修等方面的需求。

本文讨论了同步开关电源拓扑中的半桥MOSFET的基板表面平铺、腔体设计、3D堆叠等布局方法,以及键合丝、铜片夹扣等互连方式,通过对比不同方案的优缺点,为电源SiP方案设计提供参考。

1MOSFET裸芯片结构

功率开关MOSFET有3个端口,即漏极、源极和栅极。一般裸芯片的背面设计为漏极,正面是源极和栅极。源极和漏极的面积大,为大电流路径。正反两面根据实际应用溅射不同金属层。如图1所示的半桥MOSFET结构中,上管Q1的源极与低边的MOSFETQ2的漏极互连在一起。

2半桥MOSFET布局方法

2.1基板表面平铺

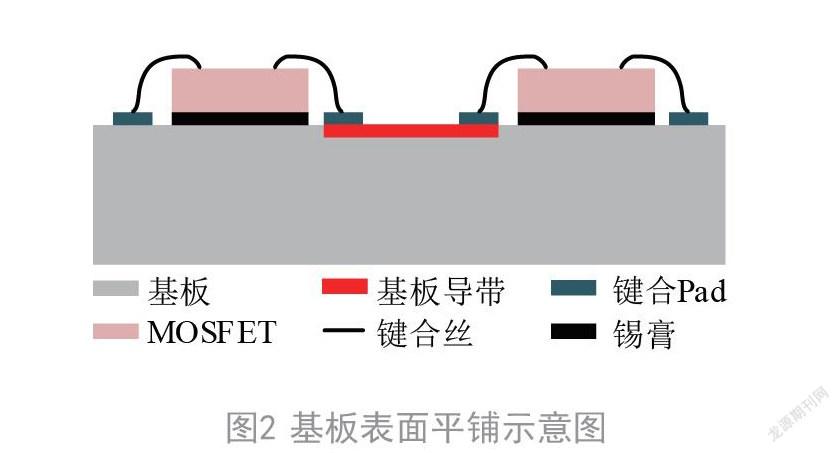

半桥MOSFET的平铺布局如图2所示。为提高电源SiP的散热性能,降低大电流路径的互连电阻,裸芯片背面的漏极通过锡膏烧焊到基板表面。正面的源极和栅极可通过键合丝或铜片夹扣连接到基板的焊盘上[3]。两芯片的源漏通过基板的铜导带实现互连。由于在基板表面,芯片的组装维修都十分便利。

2.2腔体设计

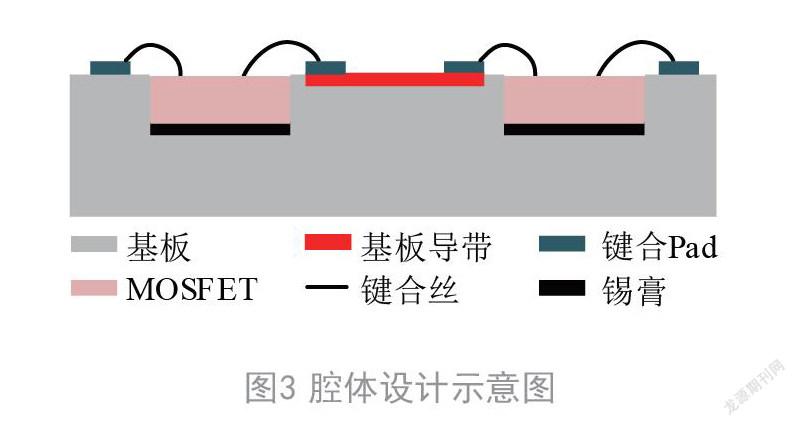

平铺布局要求基板表面和芯片间有安全距离。为减小封装面积,可以采取如图3所示的腔体设计,即将基板的外层开放式开窗,将MOSFET芯片烧焊在内层,基板键合焊盘仍在表面[4]。受电源SiP空间限制,腔体开窗面积对芯片的组装修改产生一定的影响。腔体设计节省了基板焊盘和芯片间的距离,有利于电源SiP整体尺寸的减小。

2.33D堆叠

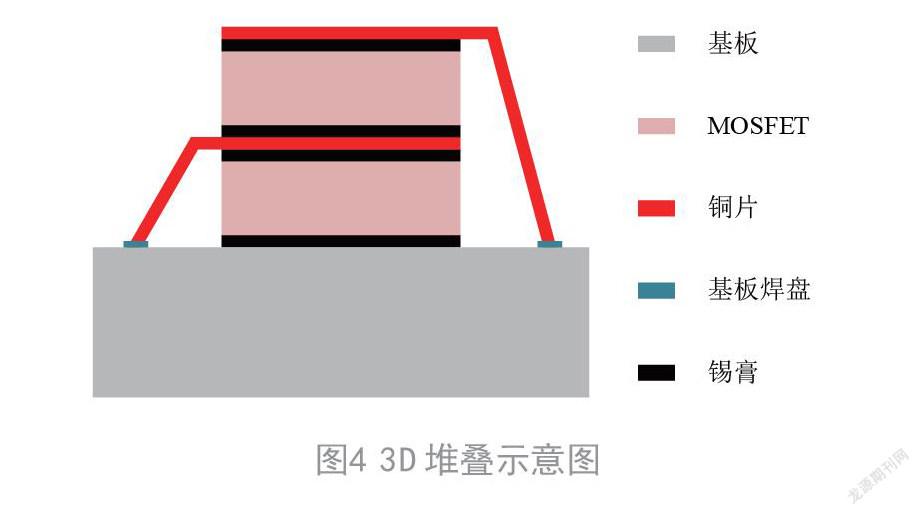

如图4所示,半桥MOSFET可采用纵向3D堆叠减小封装面积。两芯片的源极、漏极及与基板导带的互连一般采用铜片夹扣[5]。芯片与铜片间仍通过锡膏烧焊互连。3D堆叠对组装要求高,芯片焊接偏移需控制严格,避免与栅极键合丝短路;并且芯片维修的便利性差。

3互连工艺

3.1引线键合工艺

引线键合以技术成熟、工艺简单、成本低廉、适用性强等特点而在电子工程互连中占据重要地位[5]。由于铝丝/硅铝丝的导电能力强,价格低廉、延展性好,所以常用作MOSFET的键合引线。

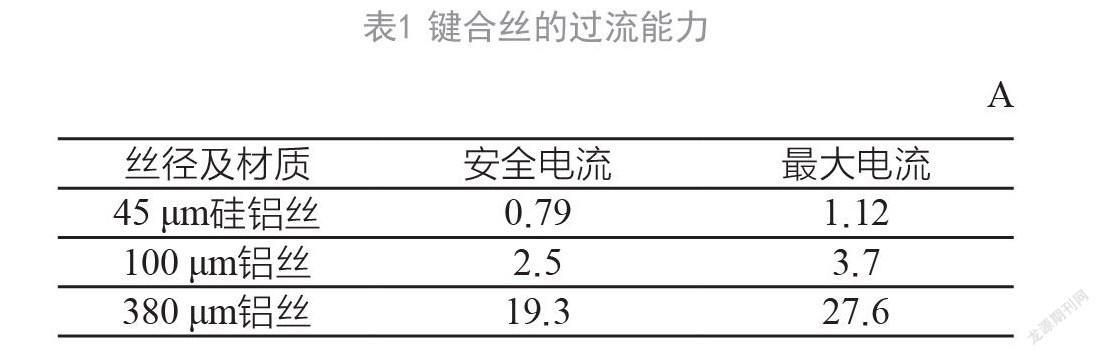

键合丝的材料和丝径影响MOSFET的过流能力,表1是常见的键合丝径及其过流能力。

3.2铜片夹扣工艺

铜片夹扣键合是通过回流焊接的方式,将有特殊形状的铜片焊接于芯片上,实现2个MOSFET的源漏极和基板导带的互连。铜片的形状与芯片开窗尺寸和版图设计相关,避免与芯片栅极走线和键合丝短路。MOSFET芯片表面需要溅射焊锡可浸润的金属材料,如钛镍金等,工艺比较复杂。

*25A为32根45μm丝径的硅铝丝并联键合,20A为8根100μm丝径的铝丝并联键合

4半桥MOSFET集成方案

在本节讨论中,功率SiP设计要求输出电流达30A;尺寸小于15mm×15mm,以满足整機对电源小型化的需求。因此,选用的某型号MOSFET裸芯片,其常温下最大持续漏极电流为95A,尺寸为4mm×4mm。通过讨论不同布局和互连方式的优缺点,确定满足电源SiP要求的方案。

4.1基板表面平铺键合方案

基板键合焊盘尺寸设计为4mm×0.5mm,满足源极多键合丝并联要求。键合焊盘和芯片烧焊焊盘的安全距离定为0.25mm。则2个MOSFET的总封装面积约为38mm2。键合丝有两种选择。选择1是MOSFET的源极和栅极采用相同的45μm丝径的硅铝丝。源极最多能键合32根硅铝丝并联,由表1知MOSFET的安全电流达25A。选择2是MOSFET的栅极和源极分别采用45μm丝径的硅铝丝和100μm丝径的铝丝。源极最多能键合8根铝丝并联,安全电流达到20A。

在基板表面平铺方案中,MOSFET热量主要是通过漏极单面向基板传导。

4.2基板表面平铺铜片夹扣方案

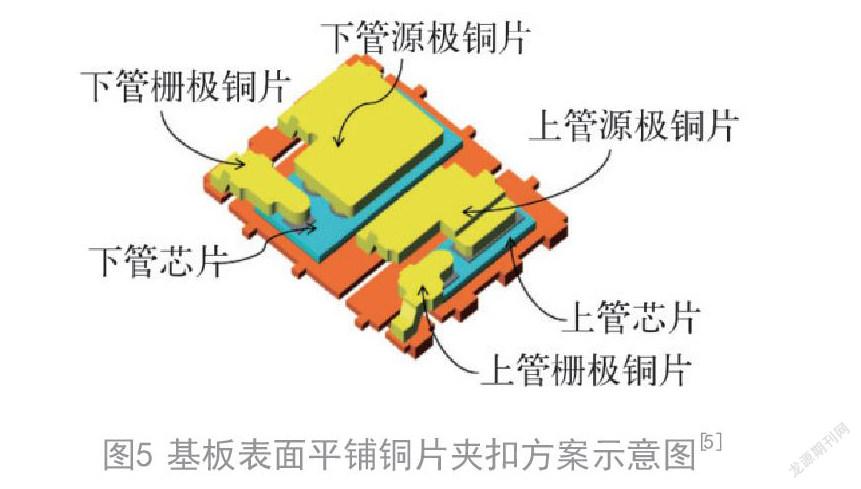

基板表面平铺铜片夹扣方案如图5所示。MOSFET源极互连改为0.2mm厚度的铜扣,可承受164A电流。受MOSFET的持续漏极电流限制,该方案的半桥MOSFET的载流能力为95A。铜扣在基板上的焊盘尺寸设计为4mm×1.5mm,则封装面积约为46mm2。大面积铜片帮助MOSFET的热量双面向基板传导,极大地降低了芯片的热阻。

4.3腔体设计键合方案

在腔体设计中,为了组装和维修,开窗面积设计为4mm×4.2mm。该方案的键合设计同方案4.1,则需要37.6mm2的封装面积,安全电流为25A(32根45μm丝径的硅铝丝并联)或20A(8根100μm丝径的铝丝并联)。

4.4腔体设计铜片夹扣方案

该方案的铜扣互连设计同方案4.2,开窗设计同方案4.3,需要45.6mm2的封装面积,载流能力为95A。

和方案4.1和4.2对比,腔体设计对半桥MOSFET封装面积改善不多。但是可减小MOSFET芯片与周围器件焊盘的距离,从而减小了电源SiP整体封装尺寸。

由于MOSFET烧焊在基板内层,相对于基板表面平铺方案,散热性略差,可通过适当增加散热铺铜面积改善热阻。

4.53D堆叠铜片夹扣方案

3D堆叠通过利用纵向空间提高封装效率。若铜扣在基板上的焊盘尺寸同方案4.2,该方案可将半桥MOSFET的封装面积减小至30mm2。两片铜扣使芯片双面散热,极大地降低了热阻。

4.6方案对比

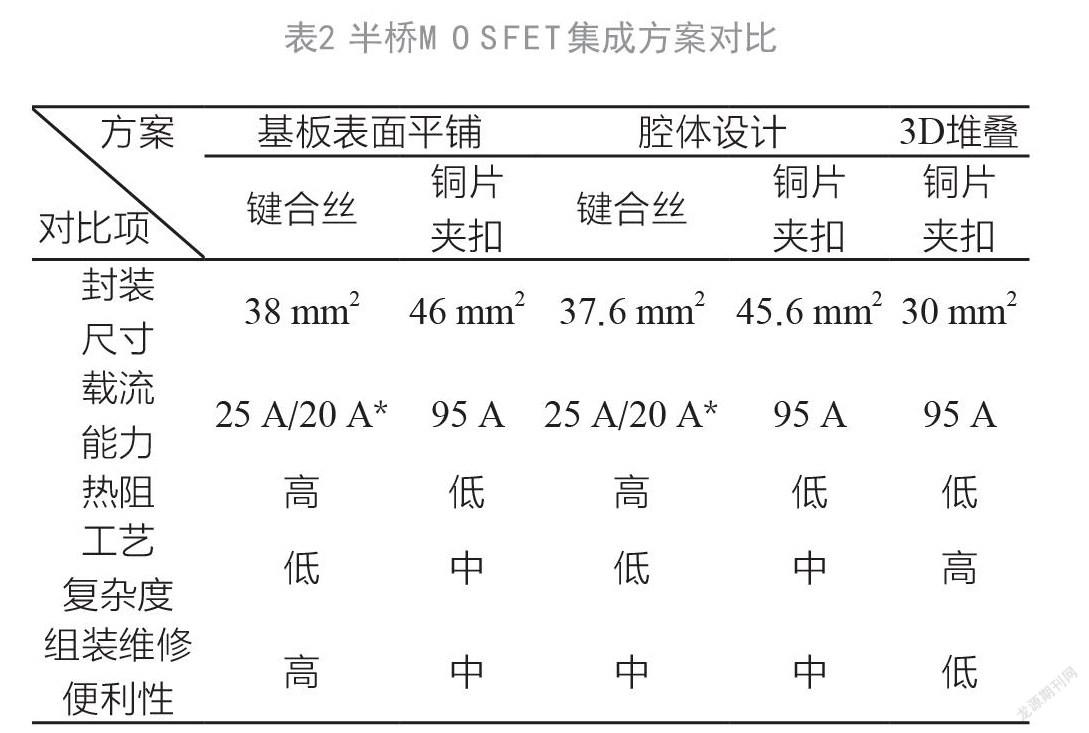

表2概述了半桥MOSFET不同集成方案的优缺点。基板表面平铺键合和腔体设计键合方案的工艺复杂度低,组装维修便利性好,但是无法满足电源SiP输出电流的要求。基板表面铜片夹扣方案在热阻、工艺复杂度和组装维修便利性之间取得了较好的平衡,但是封装尺寸不利于电源SiP的小型化设计。3D堆叠铜片夹扣方案具有最小的封装面积和很好的导热性能,但是工艺复杂度高,组装维修便利性低。腔体设计铜片夹扣是相对折中的方案,可以满足电源SiP设计要求。

5结束语

本文讨论了半桥MOSFET不同集成方案。为满足电源SiP输出电流达30A,尺寸小于15mm×15mm的要求,相对折中的方案是采用腔体设计铜片夹扣方案。该方案的载流能力达到了MOSFET的最大持续漏极电流95A;热阻低;因为节省了MOSFET裸芯片与周围焊盘的距离,有利于电源SiP的小型化。

参考文献:

[1]李扬.SiP系统级封装设计仿真技术[J].电子技术应用,2017,43(7):47-50,54.

[2]陳帅,郗小鹏,张勇.同步BUCK变换器中MOSFET选型应用研究[J].单片机与嵌入式系统应用,2019(11):75-77,81.

[3]王其超,季睿,姚佳.一种应用于GaN功放的高压电源调制器设计[J].工业控制计算机,2021,34(6):134-135.

[4]李扬.3D设计技术在SiP中的应用[J].电子技术应用,2018,44(9):39-43.

[5]霍炎,吴建忠.铜片夹扣键合QFN功率器件封装技术[J].电子与封装,2018,18(7):1-6.

[6]陈宏仕.MOSFET器件引线键合技术[J].电子与封装,2010,10(7):1-3.