基于双FIFO乒乓操作的应用数据缓冲电路研究

◆赵航 钱博

(沈阳理工大学信息科学与工程学院辽宁 110159)

FPGA设计灵活,接口众多,可以实现多种接口的功能。串口是一种最常见的接口,其设计简单,应用广泛。由于串口输入数据率可能存在与后继处理电路数据率不匹配的问题,确保不同处理过程间数据完整性变得尤为重要。乒乓操作是数字电路设计中一种常用的技巧,通过切换缓冲模块可有效地实现高速数据流的缓存[1,2]。

为了解决串口输入数据率与后继 FPGA处理模块处理数据率不匹配的问题,本文基于FPGA平台,选用双FIFO模块作为缓冲模块,利用乒乓操作作为数据流的处理技术,设计了基于双FIFO乒乓操作的数据缓冲电路。

1 乒乓操作原理

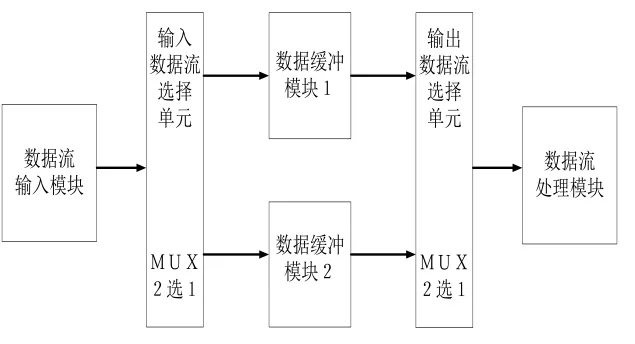

如图1所示,乒乓操作的数据处理过程为:首先,数据流的输入模块将输入的数据流发送到选择模块。选择模块将输入数据等数据量的分配到两个FIFO模块中,将整个数据处理流程分为3个分配区间。在第一个分配区间,输入数据被选择模块分配到FIFO模块1中。在第二个分配区间,将FIFO模块1切换至FIFO模块2,输入数据被选择模块分配至FIFO模块2中,并且选择模块将分配到FIFO模块1中的数据送到后续数据流处理模块。在第三个分配区间,将 FIFO模块2切换至FIFO模块1,输入数据被选择模块分配至FIFO模块1中,并且将选择模块分配到FIFO模块2中的数据经过输出选择模块后,送到运算处理模块进行运算处理。经过以上三个分配区间的不间断循环,就可以实现对数据流的高速无缝传输与缓冲。

图1 乒乓操作原理图

在整个乒乓操作过程中,输入数据流连续不断通过输入数据模块,输出数据流连续不断的被送到数据处理模块,达到了没有间隔处理数据的效果,同时节省时间,提高了数据处理速率[3]。

2 基于双FIFO的数据缓冲电路设计

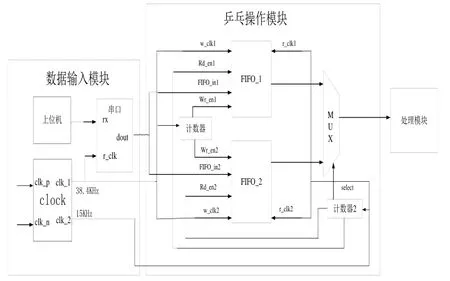

如图 2所示,该设计主要由数据输入模块、乒乓操作模块以及FPGA处理模块三部分构成。

图2 总体设计框图

首先,在数据输入模块中,通过上位机利用串口助手工具输入一串数据,串口rx接收到数据后将其发送至乒乓操作模块,用作乒乓操作模块的输入数据。其次,在乒乓操作模块中,两个FIFO模块作为数据缓存模块,将输入的数据缓存到两个FIFO模块中,通过两个计数器不断对FIFO的输入输出进行控制,将缓存到两个FIFO模块中的缓存数据不间断的送至FPGA处理模块。

3.1 数据输入模块

在数据输入模块中,包括上位机、串口以及时钟管理三部分。在该设计中,将串口的波特率设置为38400Bd,有1位起始位,8位信息位以及1位停止位,因此可得到串口数据率为38400bps,由于串口有8位信息位,所以将8bit数据视为一帧数据,一次发送144bit数据,即18帧数据。

在上位机上,利用串口助手发送数据,通过串口的rx接收上位机发来的数据。在串口部分,由于串口的数据率为38400bps,因此rx的时钟为 38.4KHz。rx将从上位机上接收到的数据发送至乒乓操作模块。在时钟管理部分,通过选用差分时钟IP核产生各模块所需要的时钟。由于串口时钟和FPGA处理模块的时钟分别为38.4KHz和15KHz,因此通过输入200MHz的差分时钟产生38.4KHz和15KHz两种时钟,38.4KHz的时钟用于串口模块,FIFO模块以及计数器1模块,15KHz的时钟用于FPGA处理模块,FIFO模块以及计数器2模块。

3.2 乒乓操作模块

在乒乓操作模块中,主要包括两个FIFO模块,两个计数器模块以及一个二选一模块。由于串口模块的时钟和 FPGA处理模块的时钟分别为为 38.4KHz和15KHz,所以两个FIFO的写时钟和读时钟分别为38.4KHz和15KHz,由于读写时钟不同,所以为异步FIFO。首先,第一个计数器在 38.4KHz的写时钟驱动下通过计数控制两个FIFO的写使能,通过控制写使能有效将串口发来的数据写入FIFO。然后,第二个计数器在 15KHz的读时钟驱动下通过计数控制两个FIFO的读使能,通过控制读使能有效,将写入FIFO中的数据读出。最后,通过二选一模块将两个FIFO模块中缓存的数据发送至FPGA处理模块。

3.3 电路具体参数设计

设计的具体参数如下:两个FIFO模块的深度设计为256位,进行一次读写的数据为144位,所以完全满足其深度要求。由于串口和FPGA处理模块的数据率分别为38.4KHz和15KHz,所以通过差分时钟模块产生的写时钟和读时钟分别为38.4KHz和15KHz。因此一次写入144bit数据由于读写时钟不同,且写时钟大于读时钟,则写入144bit数据所用的时间小于读出144bit数据所用的时间。为了保证数据在写入和读出过程不丢失,需要准确设计数据写入和读出的时间。

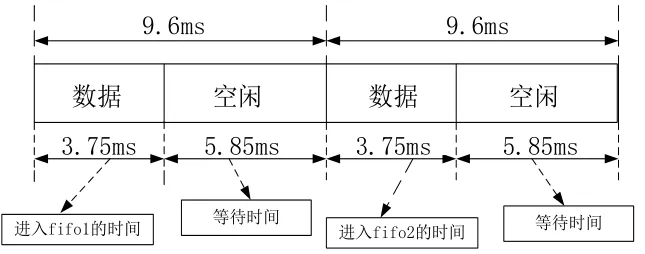

已知FIFO模块的读写时钟和一次读写的数据位数,可得数据写入和读出时间为t=N/B。

式中t为时间,N为数据位数,B为数据率。该设计中,写时钟为38.4Khz,则数据率为38.4Kbps,数据位数为144bit,则一次写入144位数据需要的时间为 3.75ms。读时钟为 15Khz,则数据率为15Kbps,数据位数为 144bit,则一次读出 144位数据需要的时间为9.6ms。由于写入数据的时间小于读取数据的时间,因此若同时不间断进行读取数据,则 FIFO中的数据未完全读取就被写入新的数据,会造成数据溢出。因此一次写入144bit数据后不能立马写入数据,需要等待一段时间,这段时间内数据是空闲状态,不写入FIFO。读出数据时间从等待时间开始直到第二次写入数据完成结束,由于数据写入时间和数据读取时间已知,因此等待时间可求得为5.85ms。

如图3所示,对数据时隙进行分析,首先通过计数器1控制写使能1有效向FIFO1模块中写入144bit数据,时间为3.75ms,然后开始等待5.85ms,在等待过程中不写入数据,而是通过计数器 2控制读使能1有效开始读取缓存在FIFO1模块中的数据。等待时间结束后,通过计数器1控制写使能2有效向FIFO2模块中写入144bit数据,时间为3.75ms,在写入数据期间继续读取FIFO1中的数据,写入完成后,FIFO1中的数据也读取完成。之后继续等待5.85ms,此时通过计数器2控制读使能2有效开始读取缓存在FIFO2模块中的数据,其过程和读取FIFO1模块中的数据相同。

图3 数据时隙图

3 仿真与测试结果分析

本次设计采用Virtex6系列XC6VLX240T芯片,利用ML605开发板进行硬件开发,开发板实物图如图4所示。

图4 开发板实物图

在设计系统模块的基础上,基于 Xilinx软件及其板上测试平台对数据流的写入与读出进行仿真与平台测试分析。在ISE Design Suite 14.7开发环境下,使用Verilog硬件描述语言,调用第三方仿真工具Modelsim,对整个数据缓冲系统行仿真综合分析。调用板上测试工具Chipscope,对整个数据存储系统行综合分析与测试。输入数据仿真图、测试图如图5、图6所示,FIFO模块读写使能仿真图如图7所示,乒乓操作输出仿真图、测试图如图8、图9所示。

图5 输入数据仿真图

图6 输入数据测试图

由图5输入数据仿真图可知,串口的rx在38.4KHz的时钟下,将上位机发送的一串数据位宽为1bit的数据流发送至乒乓操作模块,为乒乓操作模块提供数据,图 6测试图则验证了输入数据与仿真图中的数据一致。

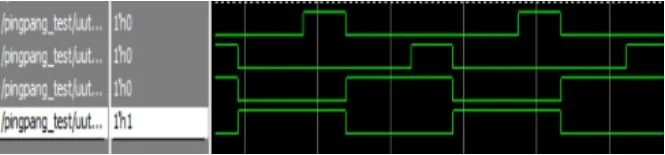

图7 FIFO模块读写使能仿真图

由图7读写使能仿真图可知,乒乓操作模块在写时钟38.4KHz,读时钟15KHz的驱动下,通过计数器对两个FIFO的读写使能进行控制。首先在FIFO1的写使能3.75ms有效后,开始进入5.85ms的等待时间,之后FIFO2的写使能持续3.75ms有效,然后进入5.85ms的等待时间,依次循环。而FIFO2的读使能在FIFO1写使能有效结束,开始等待时间后有效,持续9.6ms,直到FIFO2的写使能有效结束,FIFO2的读使能依此类推。

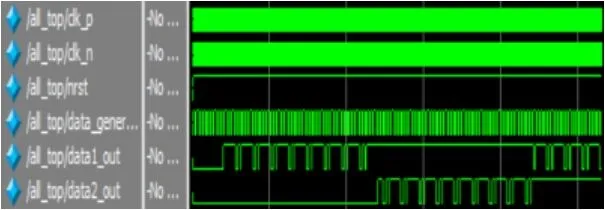

图8 乒乓操作输出仿真图

图9 乒乓操作输出测试图

由图8仿真图可知,两个FIFO模块的输出数据与输入数据一致,并且两个FIFO模块之间的输出连续,实现了数据的无缝传输,图9测试图则证明了仿真图的正确性。

5 结论

本文基于FPGA,利用其灵活设计、处理速度快的优点,设计了双FIFO乒乓操作的数据缓冲电路,Modeslim仿真和Chipscope板上测试结果表明,所设计的模块存储速度快、可靠性较高,在串口输入数据率为38.4KHz和处理模块处理数据率15KHz条件下,实现了数据的连续无缝传输,确保了数据传输的正确性。