高采样频率位移测量系统硬件架构设计

周航汛 熊显名 张文涛 谢仁飚

摘 要: 在高端光刻机中,光栅尺掩模台位移测量系统拥有较复杂的运算模型,而且要求测量系统硬件架构能满足20 kHz高采样频率的需求。通过对国内运动台位移测量系统硬件架构进行对比研究,提出一种兼容以往软件架构的基于多核DSP运算板卡的光栅尺掩模台位移测量系统硬件架构,使用多核DSP内核间共享内存通信的机制,取代运算板卡间数据总线通信的机制,同时由板内PCIe总线互联片上多核DSP与FPGA。搭建硬件在环仿真平台进行实验,实验结果表明,系统获取原始数据、进行模型运算以及发送位置数据的总体性能提升百分比约为136%,保证模型运算精度的同时,满足20 kHz采样频率的要求。

关键词: 位移测量; 硬件架构设计; 采样频率; 多核DSP; 光栅尺掩模台; 仿真平台搭建

中图分类号: TN874+.3?34 文献标识码: A 文章编号: 1004?373X(2020)22?0010?05

Abstract: In the high?end lithography machine, the displacement measurement system of the grating scale reticle stage has complex operation model, and the hardware architecture of the measurement system is required to meet the requirement of high sampling frequency of 20 kHz. With the comparison study of the hardware architecture of the displacement measurement system of the motion platform in China, a hardware architecture of the grating scale reticle stage displacement measurement system based on the multi?core DSP operation board card is proposed, which is compatible with the previous software architecture. The mechanism of shared memory communication among multi?core DSP cores is used to replace the mechanism of data bus communication among operation board cards, and the interconnection of on?chip multi?core DSP and FPGA is performed through on?board PCI bus. A hardware?in?loop simulation platform was built to carry out the experiment. The experimental results show that the overall performance improvement percentage of the system in the aspects of raw data acquisition, model operation and location data sending is about 136%, which ensures the accuracy of the model operation and meets the requirement of sampling frequency of 20 kHz.

Keywords: displacement measurement; hardware architecture design; sampling frequency; multi?core DSP; grating scale reticle stage; simulation platform setup

0 引 言

在半导体领域中,集成芯片的制造是新一代信息技术产业的核心,光刻机作为集成芯片生产制造工序中重要的环节,更是国之重器。随着光刻节点的不断延伸,光栅尺掩模台位移测量系统的硬件架构需满足20 kHz高采样频率的要求。

荷兰的埃因霍芬理工大学采用ATCA总线架构对系统硬件架构进行了升级,研究提出基于多核CPU的CARM模型[1],并分析任务执行时间[2],优化运动控制性能[3],利用FPGA作为协处理器加速模型[4?5]运算,减少数据传输延时。

国内部分公司和高校,如SMEE、清华大学、哈尔滨工业大学、华中科技大学、桂林电子科技大学等,也针对运动台位移测量系统的性能在做相关的研究,并提出了一些运动台位移测量系统硬件架构,但是其采样频率均未达到要求。目前国内关于光栅尺掩模台位移测量系统的采样频率研究并未成熟,本文基于数据流分析,对比以往的测量系统硬件架构,设计了支持高采样频率的硬件架构方案,并搭建测试平台对方案进行验证。

1 国内相关工作

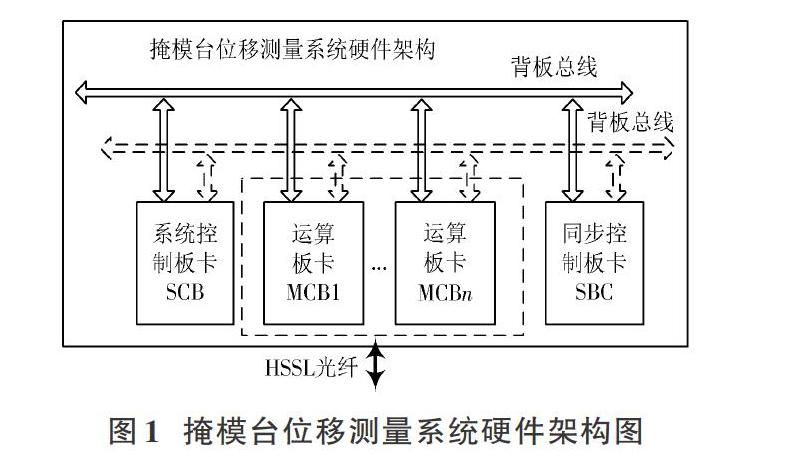

目前国内提出的掩模台位移测量系统中模型运算部分硬件架构如图1所示,主要由1块系统控制板卡(SCB)、n块运算板卡(MCB)、1块同步控制板卡(SBC)、背板总线和光纤构成。

背板总线为VME总线,技术十分成熟,以其为基础进行二次开发覆盖了工业控制、军用系统、航空航天、交通运输和医疗等领域[6],在运动台位移测量系统中也得到了广泛应用。基于VME总线技术,华中科技大学团队设计一种双硅片台超精密运动控制系统硬件平台,能够实现65 nm光刻机双硅片运动台位移的测量和运动的控制[7],并在双硅片台样机中成功试用。哈尔滨工业大学团队设计一种基于宏微驱动的光刻机掩模台控制系统,能够实现5 kHz采样频率下X,Y,RX,RZ四自由度的百纳米误差控制[8]。SMEE团队设计一种运动台位移测量系统,采样频率达到5 kHz,并在其90 nm光刻机中成功应用。桂林电子科技大学团队也设计基于二维光栅的运动台高精度位移测量系统硬件在环仿真实验,在20 kHz采样频率下,测量精度[9]优于0.79 nm。

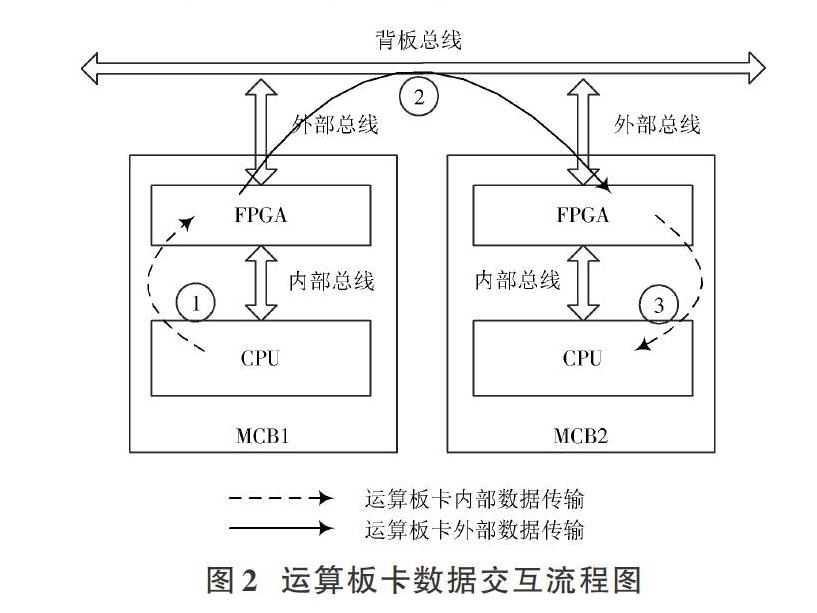

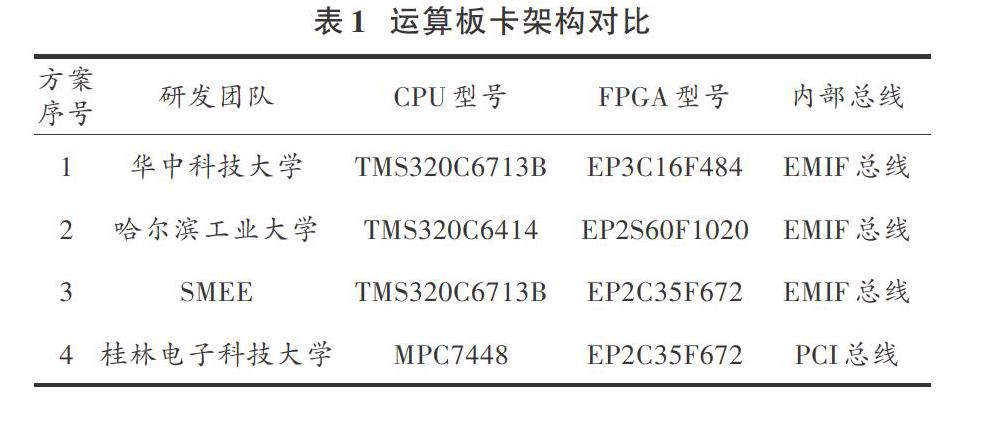

如表1所示,对比以上各团队设计的运动台位移测量系统运算板卡架构可知:前3种方案都采用单核DSP+FPGA架构的运算板卡,其中内部总线为EMIF总线,数据吞吐率最高可达1 200 MB/s。相较于SMEE,虽然华中科技大学和哈尔滨工业大学团队分别对FPGA[10]和DSP[11]性能进行了升级,但是并没有优化内部总线。方案4中,运算板卡采用PowerPC+FPGA架构,相较于前3种方案,虽然CPU的性能有了较大提升,但是内部PCI总线最高通信速率为66 MHz,数据传输的速率依然受限。

2 高采样频率位移测量系统硬件架构设计

图1中基于VME总线的通用硬件架构兼容性和可维护性较好,但是运算板卡间数据交互环节多,且内部总线的数据带宽低,以至于采样频率很难提升。针对以上两点问题,本文提出一种基于多核运算板卡的硬件架构,多核CPU+FPGA架构的运算板卡,将运算板卡间的数据交互变为多核CPU内核间的数据交互,同时升级内部总线的带宽,提升系统采样频率。

2.1 多核运算板卡的选择

目前工业上搭载多核CPU的运算板卡从CPU架构上进行分类,主要有四大类:X86,PowerPC,DSP和ARM,其性能对比如表2所示。

由表2可知,X86架构的多核运算板卡较为成熟,浮点运算能力强,但是软件架构兼容性差,且成本高。PowerPC架构的多核运算板卡浮点运算能力和实时性都很好,但是成本较高,且存在国外技术封锁问题。RAM架构的多核运算板卡性能较差,主要用于低功耗移动嵌入式设备中。综合分析,DSP架构的多核运算板卡在各方面的性能都很好,且软件架构兼容性高,是最合适的选择。

目前很多DSP芯片厂商都推出了多核DSP,其中,TI的TMS320C6678凭借优异的性能在工业领域得到广泛应用。TMS320C6678内部集成8个内核,单内核最高主频1.4 GHz,能提供每秒高达40 GB MAC定点运算和20 GB FLOP浮点运算[12]。此外芯片采用高效的KeyStone多核片内架构设计,拥有高速的片内总线和L1,L2和MSM多级存储模式,同时支持RapidIO,PCIe等高速外部通信总线以及SYS/BIOS轻量级实时操作系统。因此本文选择搭载TMS320C6678的多核运算板卡,其中,TMS320C6678和FPGA通过PCIe总线互联,支持高达5 GB/s的数据交互速率。

2.2 基于多核运算板卡的硬件架构设计

本文提出的基于多核运算板卡的光栅尺掩模台位移测量系统硬件架构如图3所示,在兼容以往背板总线架构和软件架构的基础上,由1块多核运算板卡替代图1中的多块单核运算板卡,将单核运算板卡间的数据交互变为多核DSP中内核间的数据交互。TMS320C6678核间数据交互的方式主要有3种:共享内存(MSMC)、QMSS/CPPI和EDMA数据搬移。4 MB大容量的MSMC可以供所有内核访问,且自带仲载机制,读写简便,方便定义传输协议。QMSS/CPPI能够满足多样化的数据交互需求,但是需要遵循固有的通信机制,实现复杂,且数据传输的时间开销不可控。EDMA数据搬移适合大批量数据交互,小批量数据交互的时间开销并不理想。模型运算时,核间数据交互量不大,为了减少时间开销,选择MSMC实现核间数据交互最为合适。

3 实验及结果分析

3.1 硬件在环仿真平台

为了验证本文提出的硬件架构的性能,搭建如图6所示的硬件在环仿真实验平台。MCB1和MCB2都为搭载TMS320C6678的多核运算板卡,其中,MCB1为仿真端,用于模拟光栅数据采集板卡通过背板数据总线发送光栅尺原始测量数据至控制端,同时接收控制端通过光纤发送的模型运算结果;MCB2为控制端,主要用于获取光栅尺原始测量数据、进行位移模型运算和通过光纤发送运算结果,是系统实际应用中的多核运算板卡。

3.2 数据交互实验

为了验证共享内存数据交互的伺服性能,利用搭建的硬件在环仿真平台进行实验,具体流程如图7所示。Core0发送数据至共享内存,并回写,然后Core1失效LD1 Cache中的对应数据,并从共享内存中读取对应数据,完成一次共享内存数据交互。通过采集计算各个环节的时间开销,验证共享内存数据交互的传输性能。模型运算过程中,核间交互数据量在10~30个int之间,为了更好地测试共享内存数据交互的传输性能,将传输的最大数据量设为200个int。

3.3 硬件在環仿真实验

为了验证提出的硬件架构是否满足光栅尺掩模台位移测量系统对采样频率的要求,将光栅尺掩模台位移测量系统的软件移植至提出的硬件架构,并进行硬件在环仿真实验。对比以往的硬件架构模型运算结果,误差在同一数量级,满足系统对模型运算误差的要求。从时间开销角度对比分析,系统获取原始数据、进行模型运算以及发送位置数据的性能提升,结果如表3所示,采用提出的硬件架构,三个环节性能都有显著提升,总体性能提升百分比约为136%,满足20 kHz采样频率的要求。

4 结 语

本文以光栅尺掩模台位移测量系统硬件架构为研究对象,通过对比国内提出的运动台位移测量系统硬件架构,分析运算板卡间数据交互的流程,提出一种基于多核运算板卡的高采样频率位移测量系统硬件架构,并从运算性能、实时性、软件兼容性以及成本等方面考虑,选择搭载TMS320C6678多核DSP的板卡作为运算板卡。搭建硬件在环仿真平台,实验对比PCI+VME,EMIF+VME和MSMC三种数据交互方案的时间开销可知,相较于其他两种方案,本文提出的MSMC方案的数据传输性能提升百分比可达2 000%。进行光栅尺掩模台位移测量系统硬件在环仿真实验,结果表明,在保证模型运算误差要求的同时,系统获取原始数据、进行模型运算和发送位置数据的时间开销都显著降低,总体性能提升了约136%。本文提出的基于多核运算板卡的硬件架构能够很好地满足光栅尺掩模台位移测量系统对20 kHz采样频率的要求,可在高端光刻机上应用。

参考文献

[1] CAMELO V D. Multi?core CPU exploration for CARM host in ASML technology [D]. Eindhoven: Eindhoven University of Technology, 2012.

[2] GOZEK A E. Task execution time prediction for motion control applications [D]. Eindhoven: Eindhoven University of Technology, 2013.

[3] HERNANDEZ D S P. Design?space exploration for high?performance motion control [D]. Eindhoven: Eindhoven University of Technology, 2013.

[4] JAMBEKAR S W. Performance improvement of motion?control applications using multi?ASIP in FPGA [D]. Delft: Delft University of Technology, 2014.

[5] VAN BROEKHOVEN M. Motion controller acceleration by FPGA co?processing [D]. Eindhoven: Eindhoven University of Technology, 2014.

[6] 刘贵行,魏国,赵世伟.机载测距机测试平台设计与开发[J].现代电子技术,2019,42(11):165?168.

[7] 胡永兵.双硅片台超精密运动控制系统的硬件平台研究[D].武汉:华中科技大学,2014.

[8] 饶裕,刘杨,齐彪,等.基于宏微驱动的光刻机掩模台控制系统设计[J].自动化技术与应用,2017,36(10):61?64.

[9] 张文涛,杜浩,熊显名,等.高精度位移测量系统硬件在环仿真[J].中国激光,2019,46(2):86?92.

[10] 王耀.基于VME总线的多处理器运动控制卡[D].武汉:华中科技大学,2012.

[11] 张常江,宋法質,宋跃,等.基于VME总线的光刻机多板卡通信接口设计[J].自动化技术与应用,2016,35(5):100?104.

[12] 谢俊,梁光明,王职军,等.基于TMS320C6678的细胞图像识别系统并行实现方法[J].现代电子技术,2014,37(2):110?113.