基于PowerPC架构双总线通信机制设计与实现

李春华 何菲玲 康壮

摘要:为满足系统数据通信的高带宽、高可靠性和低时延的需求,实现系统内各功能模块高速互联通信机制,本文提出一种基于PowerPC架构双总线通信机制,该通信机制以PowerPC架构为基础,实现SRIO交换和以太网交换两种总线通信功能,在应用中,以太网通信用于控制信号传输,SRIO通信用于数据传输,SRIO数据传输速率达到6.25Gbaud,极大的提高数据传输带宽,同时,也避免控制信号和数据信号占用同一线路产生的不利影响,实现双总线通信机制。另外,基于PowerPC架构的处理器也可对数据进行管理和分配,实现可配置管理数据的功能。

关键词:PowerPC;SRIO(Serial RapidIO);以太网;双总线通信

中图分类号:TP336;TN915.06 文献标识码:A 文章编号:1672-9129(2020)12-0022-01

1 引言

SRIO传输协议简单、支持多种拓扑结构,高性能、基于数据包交换的互联体系结构,主要用于嵌入式系统内部互连,板与板之间的通信。SRIO协议只通过物理层,传输层即可完成数据的交换转发,在SRIO互联系统内,每个互联器件具有唯一一个设备ID,通过数据包中ID可访问相应的物理端口,进行数据传输。

Gigabit Etherent(千兆以太网)是一种高速以太网技术,不仅兼容传统以太网,又显著提高传输速率,千兆以太网采用与传统以太网相同的结构、帧格式、网络协议、数据流控制模式和全/半双工工作方式,逐渐成为一种通用的数据传输方式,在高速通信设计中,通过网络交换实现互联互通机制已经常态化。

随着电子技术的不断发展,芯片的集成度越来越高,其性能越来越强大,数据传输速率越来越快,设备性能越来越完善,传统的通信方式数据带宽受到限制,单总线通信方式逐渐被取代。在传统的通信方式中,极易出现控制信号和通信数据“争夺”总线的控制权,导致控制命令不能及时响应,数据传输出现丢包现象,极大降低互连系统的可靠性,基于双总线通信机制可有效解决上述问题,SRIO通信用于数据传输, 以太网通信用于控制信号传输,提高系统通信可靠性。

2 硬件架构

本文采用PowerPC架构实现双总线通信机制,硬件架构框图如图1所示,处理器P2020通过2路Serdes接口分别与以太网交换芯片88E6185和SRIO交换芯片CPS1432连接,建立数据通信通道;通过2路IIC接口分别与以太网、SRIO交换芯片连接,实现处理器对以太网、SRIO交换芯片初始化功能。在系统中,6185和1432与其他模块建立连接关系,实现双总线通信机制,系统下发命令等控制信号通过6185交换芯片传输,大量的数据通过1432交换芯片传输,充分发挥双总线通信的特点。

3 各模块功能设计

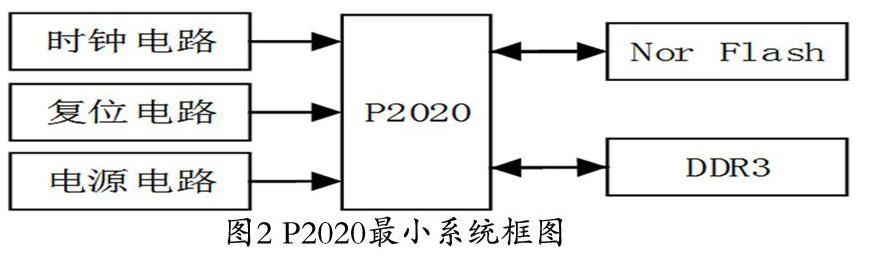

3.1 PowerPC架构处理器。本文采用Freescale公司的P2020,该芯片基于PowerPC架构,具有2个Power Architecture e500内核,支持36位物理地址,支持双精度浮点数计算,主频时钟高达1.33GHz,内部有3个独立的以太网控制器支持10/100/1000Mbps,支持2个RapidIO,3个PCIe控制器,具有高性能、功耗低的特点,图2为P2020最小系统框图。

在设计中,首先建立以P2020处理器为核心的最小系统,如图2所示,时钟电路提供100MHz系统时钟,复位电路实现P2020系统复位功能,电源电路为P2020提供内核电压VDD和各接口电压,Nor Flash提供程序的存储空间,DDR3提供双倍速率动态存储空间。

3.2 以太网交换功能。本文采用Marvell公司以太网交换芯片88E6185实现网络交换功能,该芯片可提供10路千兆以太网端口,每个端口均可配置成10Mbps/100Mbps/1000Mbps工作模式,且集成了10个独立的3倍速Serdes收发器,每个端口可配置为光纤端口,10个独立的媒体访问控制器完全符合IEEE802.3协議,支持25MHz时钟源输入。

以太网交换功能配置分为硬件配置和软件配置,软件配置是P2020通过IIC接口完成对交换芯片的初始化,完成每个网络端口配置,配置传输速率、工作方式等,最终通过交换芯片实现与其他模块通信功能。

3.3 SRIO交换功能。本文采用IDT公司CPS1432交换芯片实现模块SRIO通信,该芯片共有32路RapidIO端口,单片峰值吞吐量可达160Gbps,支持1x/2x/4x模式,数据传输速率可设置1.25/2.5/3.125/5.0/6.25Gbaud,芯片设计符合RapidIO2.1标准,支持多种位宽模式、全端口无阻塞交换,传输延时达到几百纳秒。

SRIO交换芯片硬件配置中,差分对接收端口电源电压VDDS需要先于差分对发送端口电源电压VDDT供电,P2020与CPS1432之间使用2x模式连接,通过IIC完成对CPS1432协议、速率和路由配置,完成初始化工作,建立SRIO总线通信机制。

4 总结

本文介绍了基于P2020处理器的88E6185网络交换和CPS1432 SRIO交换的设计原理和实现方式,以太网传输控制信号,SRIO传输数据流,实现双总线通信机制的功能,随着电子技术的不断发展,双总线通信将会在嵌入式系统中达到广泛的应用。

参考文献:

[1]朱新忠,王冠雄,韦杰.一种基于Serial RapidIO标准协议的高速交换技术[J].航天标准化.2020(02):8-11.

[2]张剑锋,周伟,吴军.基于综合一体化数字平台的VPX总线网络交换设计[J].数字通信世界,2020(06):71-72.

[3]郭静.FPGA+SRIO+VPX架构的多路高速互连信息处理系统实现[J].重庆工商大学学报(自然科学版),2020,37(04):46-51.

作者简介:李春华(1992-),男,汉族,河南周口,助理工程师,硕士研究生,研究方向为高速信号处理与数据通信技术。