基于multisim的倒计时电路的设计与改进

万 文,王 炜,吴 敏

(1.武汉软件工程职业学院,湖北 武汉 430205;2.武汉船舶通信研究所,湖北 武汉 430205)

1 改进前的电路图

1.1 计数器74LS192

集成芯片74LS192是同步计数器,双时钟输入,并具有清零和置数等功能[1-3]。D~A是并行数据输入端,D是最高位,A是最低位;QD~QA是数据输出端,QD是最高位,QA是最低位;UP是加法计数脉冲输入端;DOWN是减法计数脉冲输入端;CLR是置零端(高电平有效);置数端(低电平有效);BO是减法计数时的借位输出端,当输出端等于0000时,BO=0;CO是加法计数时的进位输出端,当输出端等于1001时,CO=0。74LS192功能表,如表1所示。

1.2 数码管显示器

图1 74LS192的引脚图和逻辑符号

表1 74LS192功能表

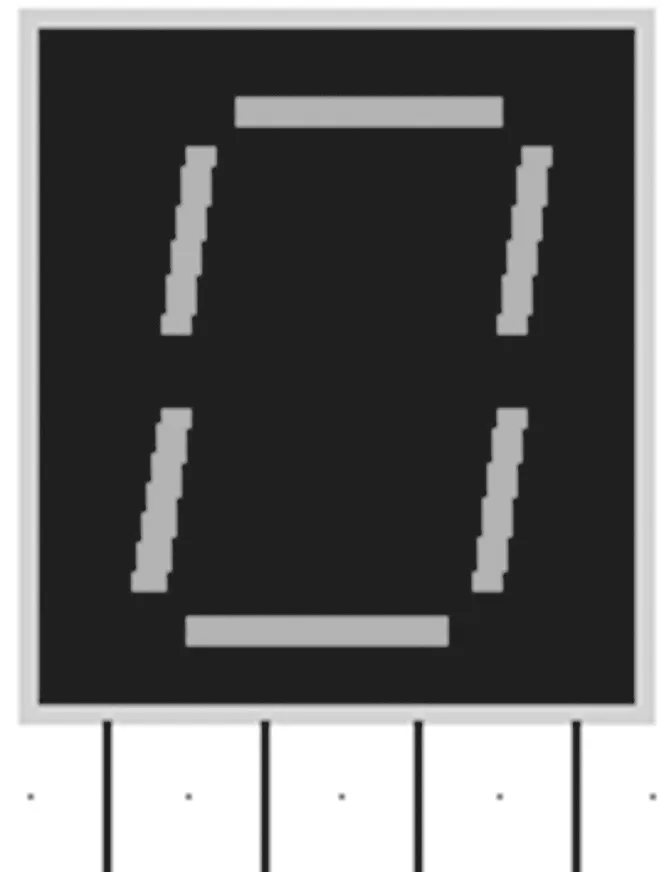

设计中用到的是七段数码管显示器。七段数码管显示器有共阳极和共阴极两种类型[4]。在multisim软件中,选用的是共阴极的数码管显示器。图2是multisim软件中七段数码管显示器的模型图。该模型是七段数码管和译码器的合成器件,默认是共阴极的。系统默认该显示器内部已连接电源和地,显露在外的输入端口有4个,从左到右依次是高位至低位[5]。读数遵循8421BCD码制,即输入的是什么值,该显示器就会显示什么数值。例如:若输入0101,则显示器将显示“5”。

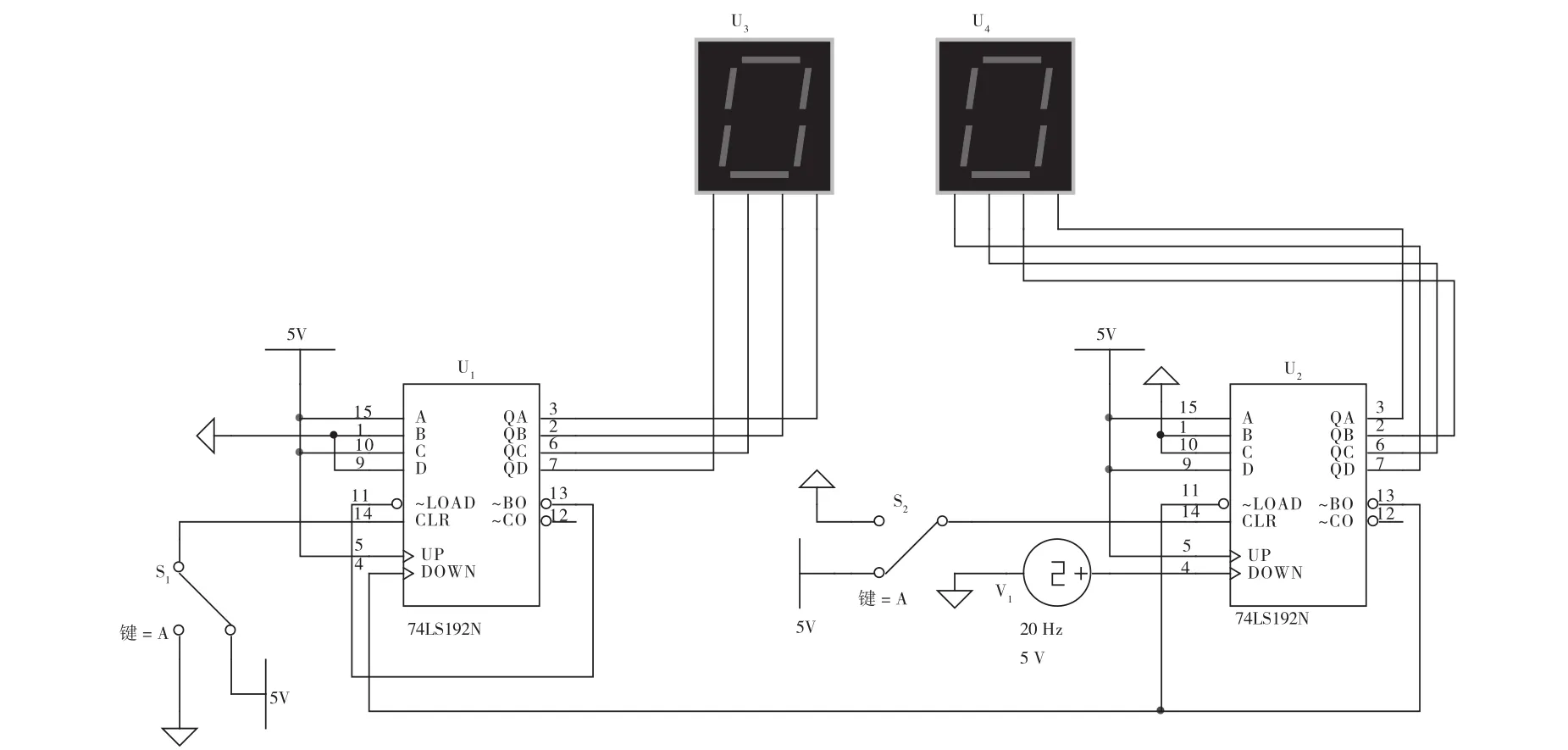

1.3 倒计时电路

图3是基于multisim软件设计的倒计时电路,电路功能是实现59~00的倒计时显示电路。图3用到了2片74LS192计数器芯片,分别用来计数十位和个位;U1、U2的输出端分别与U3、U4的输入端依次连接,即U1、U2的计数值将通过U3、U4显示。

图2 数码管显示器

图3 原倒计时电路

因为是倒计时电路,所以2片74LS192计数器芯片的计数脉冲都是通过引脚DOWN输入。参照表1,此时UP引脚不起作用,都接高电平;U2的时钟信号由multisim软件的时钟源提供,U1的时钟信号由低位计数器U2的借位输出端BO提供[6]。

2 原电路图出现的问题

2.1 理论结果

根据计数器芯片74LS192的工作原理,计数器在倒计时过程中,输出值为0001~0000~1001时,在输出为0000的整个时间段,BO=0保持不变,具体波形图如图4所示,即在理论情况下两片计数器的BO端口的输出波形。在此理论基础上,高位计数器芯片U1输出端口QD~QA的数值将由0101~0100~0011~0010~0001~0000~0101依次循环。

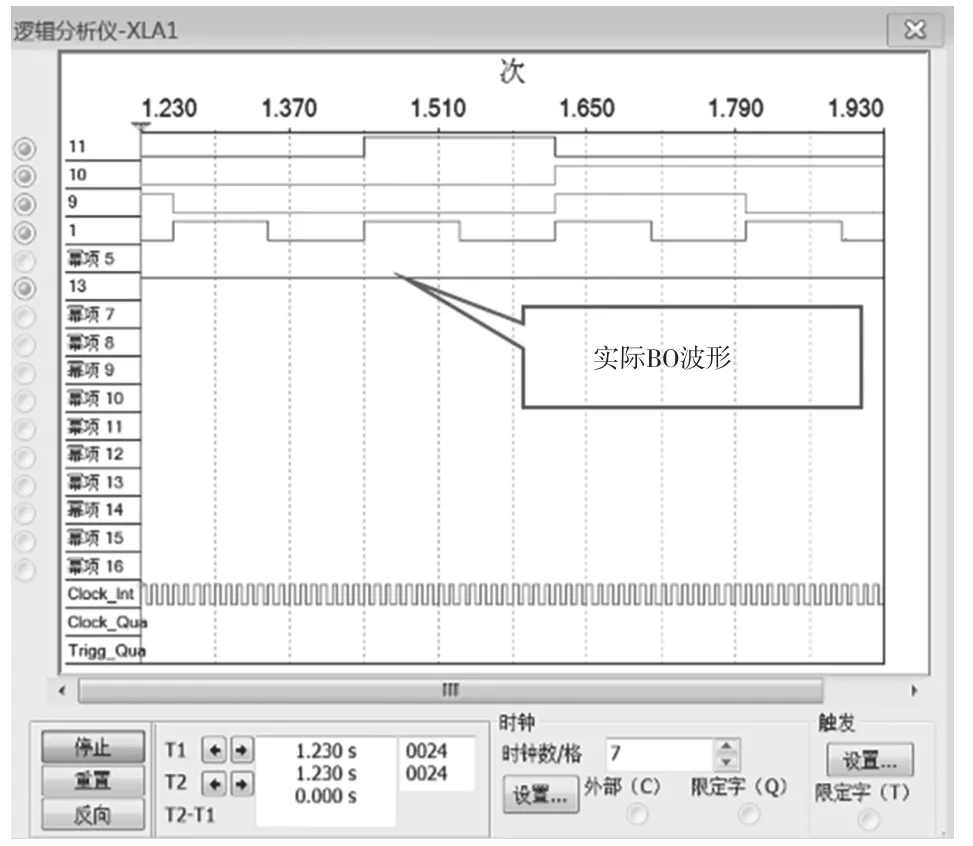

2.2 实际仿真结果

图5是计数器芯片U1输出引脚的实际的波形图。可以看出,借位端口BO输出的一直为高电平,与理论不符合。从图5还可以看出,计数器U1的输出值实现的是1010~0000~1010的倒计时,并未实现0101~0000~0101的倒计时功能,不能满足实验要求。

3 问题分析

对比图4和图5不难发现,实际波形与理论波形出现的不符合,主要原因是U1的借位端口BO没有等于低电平的阶段。BO不能等于0,将导致U1的置数端口不能等于0,置数永远无效,所以输出不可能从0000跳转到0101。

由于逻辑分析仪的主要功能是分析不同通道的逻辑关系,而这里要分析BO端口出现故障的原因,因此选用示波器更适合。

图4 计数器BO端口理论波形图

图5 计数器输出BO端口实际波形图

在原电路图中,将U1的倒计时时钟输入端口DOWN和借位端口BO接入示波器,可以观察到如图6所示的波形图。通过原倒计时电路图3易发现,十位DOWN和个位的BO连接在一起。那么,图6的波形图说明个位的BO端口只在极端的时间内等于0。由于这个时间太短暂,导致十位的借位输出端BO来不及反应变为低电平,所以十位的BO一直等于高电平。

4 改进措施

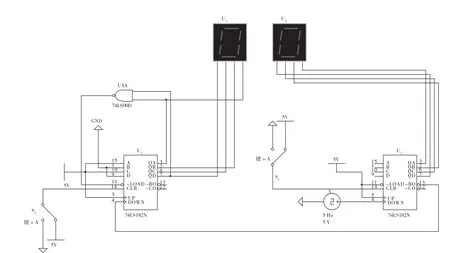

通过以上分析,不能实现59~00倒计时的主要原因是U1的BO端口不能出现低电平。所以,要解决这个问题,最好要避开使用U1的BO端口。原电路U1的置数端LOAD与自身的BO相连,改进后的电路如图7所示。其中,U1的置数端LOAD与自身的输出端口QD、QA连接,其逻辑关系满足即只有当QD=0且QA=0时,计数器U1同步置数。也就是只有输出端等于1001时,U1立即置数,输出立即等于置入的数值0101,由此十位计数器将实现倒计时0101~0000~0101的功能。

图6 计数器BO的波形图

图7 改进后的倒计时电路图

改进后的电路图和原图相比,个位计数部分也有所改动。原电路中个位倒计时采用的是同步置数法,改进后的电路利用计数芯片74LS192的DOWN端口接入时钟脉冲清零后能够自动倒计时的特点,没有用到置数端口也能实现设计目标,进一步简化了倒计时电路。

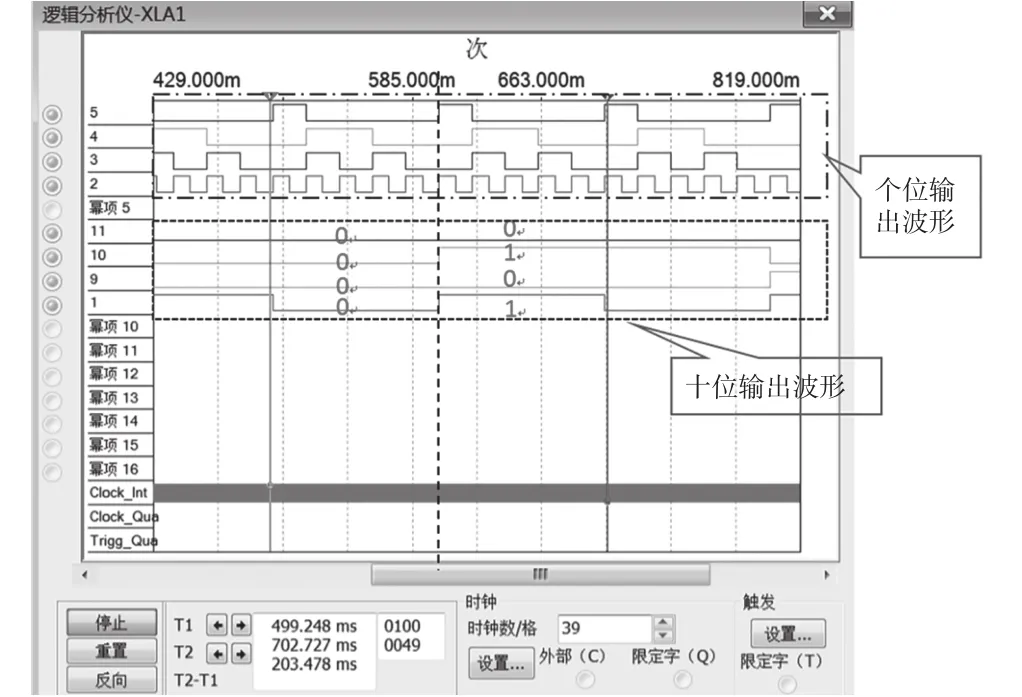

改进后电路图的计数器的输出端波形图如图8所示。可以看出,十位输出端能够实现倒计时0~5~0,并且在十位保持不变的时间段内,个位实现了从9~0的输出。

图8 改进后电路的输出波形图

5 结 论

本文利用multisim平台,发现并解决了以74LS192芯片为核心的倒计时电路的问题,在教学过程中对学生有极大帮助,有利于学生理解计数器74LS192,帮助学生提高数字电路设计能力。