基于FPGA和控制器MCP2517FD设计的CAN FD总线接口

张波涛

摘要:CAN(Control Area Network,控制器局部网)总线广泛应用于工业自动化监控网络中,传输速率的应用已经逐渐逼近CAN总线的带宽,急需更高速率带宽的总线通讯方式,CAN FD(CAN with Flexible Data-Rate,带灵活可变数据波特率的CAN总线)总线应运而生,可以实现更高速率和更长有效载荷。本文提出了一种CAN FD总线接口设计技术,通过灵活的FPGA(Field-Programmable Gate Array,即现场可编程门阵列)设计SP(Iserial peripheral inter-face,串行外围设备接口)接口控制CAN FD芯片MCP2517FD,实现CAN FD总线接口的设计,系统实现后,可以根据现场应用提出的新要求对FPGA进行升级,增加了使用的灵活性。

关键词:FPGA;CAN;FD;MCP2517FD;SPI

CAN总线属于现场总线的范畴是一种有效支持分布式控制和实时控制的串行通讯网络,最初是由德国BOSCH公司为汽车的监测和控制而设计的,后来逐渐发展到用于其它工业领域。CAN總线具有低成本、极高的总线利用率、长达10km的数据传输距离,高达1Mbps的数据传输速率、可根据报文ID进行选择,可靠的错误处理机制、自动重发被破坏的信息、节点在错误严重的情况下可自动退出总线等特点。

CAN FD总线兼具CAN总线的特点,在其基础上传输速率带宽由1Mbps提升至10Mbps,采用新的DLC(Data Length code)编码方式使数据场长度由8 个字节增加至64个字节,更大程度上满足了工业领域对于高速率传输的需求。

为了灵活的使用CAN FD总线,本文提出一种灵活的CAN FD总线接口设计技术,即使用FPGA和控制器MCP2517FD实现CAN FD接口设计的方案,不仅能够实现CAN总线接口通讯,同时对于后期使用过程中,可以根据不同的要求进行升级,增加使用的灵活性。

1总线控制器MCP2517FD简介

为了实现CAN FD总线的应用,Microchip公司在CAN总线控制器MCP2515的基础上推出了MCP2517FD,它既可以满足CAN总线的技术要求,又可以实现CAN FD总线的使用,带有符合工业标准的SPI串行接口,具有体积小,易使用及低成本等特点。

MCP2517FD主要功能参数如下:

1. 支持CAN2.0B和CAN FD协议;

2. 仲裁域速率可达1Mbps,数据域速率可达8Mbps;

3. 有标准帧和扩展帧两种可供选择,每帧包含的数据长度为0~8个字节(CAN2.0B协议)或0~64个字节(CAN FD协议);

4. 支持远程帧;

5. 内含31个FIFO,都可以通过配置作为发送或接收FIFO使用;内含1 个发送队列;内含具有32位时间戳的发送事件FIFO;

6. 有可编程的自动重传机制:分别为无限次数、3次或禁用;

7. 内含32个灵活的过滤器和掩盖对象,每个对象都可以配置为过滤:标准ID+前 18个数据位或扩展ID;

8. 有多达3 个中断引脚;

9. 支持高达20MHz的SPI时钟速率,支持SPI模式0,0和 1,1;

10. 带有CRC的SPI命令以检测SPI接口上的噪声,有受纠错编码保护的RAM

11. 40、20或 4MHz晶体、陶瓷谐振器或外部时钟输入,带预分频的时钟输出;

12.工作电压:2.7V~5.5V;

13.使用5.5V电压、40MHz时钟时工作电流最大为12mA,睡眠模式下电流为10μA。

2硬件电路设计

本文设计的是CAN FD总线接口,因此硬件电路设计采用Altera公司的EP1C20F324I7N芯片产生控制时序逻辑;采用Altera公司的EPCS4SI8芯片作为FPGA的配置芯片;采用Microchip公司的控制器MCP2517FD实现CAN FD总线协议;采用NXP公司TJA1044GT芯片作为总线的收发器,将总线控制器产生的数字信号转换为符合CANFD总线格式的信号;FPGA和MCP2517FD总线控制器使用的时钟为20MHz。

CAN FD总线硬件电路设计如图1 所示。

3 FPGA软件设计

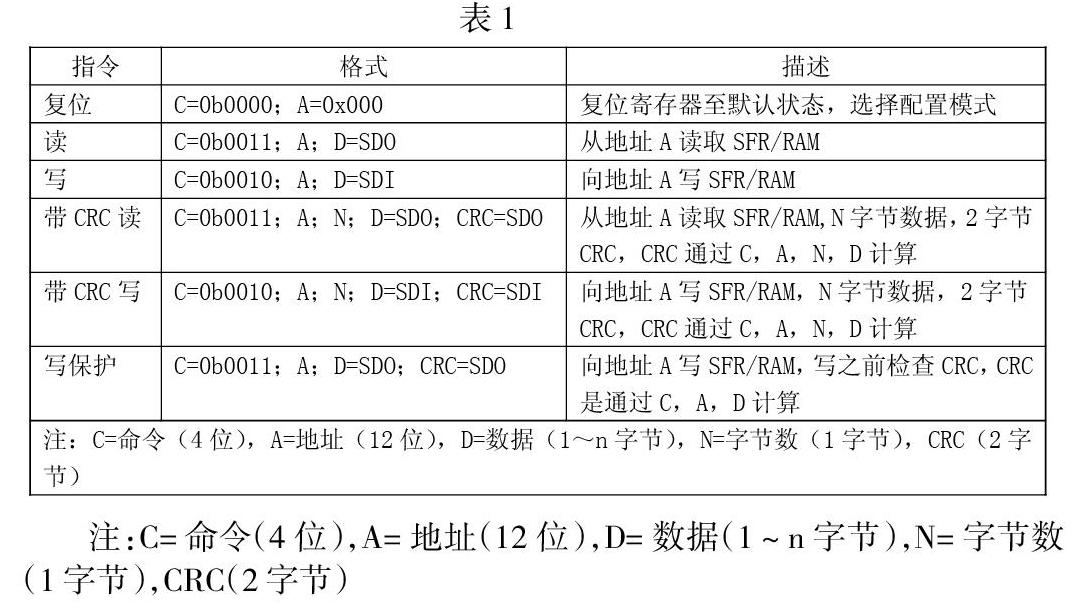

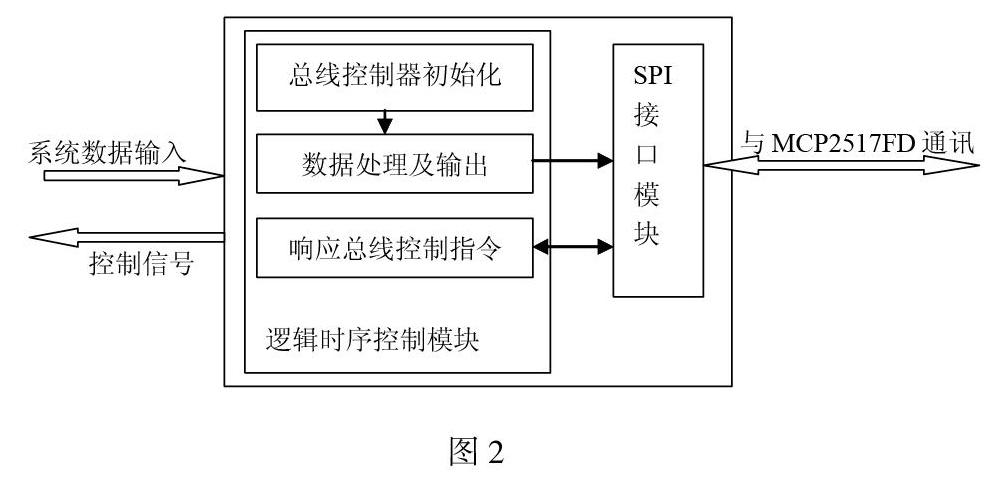

CAN FD总线接口的软件设计主要分为逻辑时序控制模块和SPI接口模块,其中逻辑时序控制模块主要实现MCP2517FD总线控制器的初始化、数据处理及输出和响应CAN FD总线控制指令等功能;SPI接口模块主要实现FPGA与MCP2517FD的通讯。SPI指令格式见表1,除复位采用16位指令,其余读写均采用48位指令(即4 位命令+12位地址+32位数据)。软件各功能模块如图2 所示。

3.1 逻辑时序控制模块

注:C= 命令(4 位),A= 地址(12 位),D= 数据(1~n 字节),N= 字节数(1 字节),CRC(2 字节)

3.1.1 总线控制器的初始化

总线控制器的初始化主要包括MCP2517FD特定寄存器的初始化和CAN FD控制器模块寄存器的初始化,分别是对控制器和总线通讯格式进行的初始化。具体内容见下:

a) 初始化MCP2517FD特定寄存器

1) 复位使芯片进入配置模块;

2) 初始化时钟、I/O口、校验及纠错码。

b) 初始化CAN FD控制器模块寄存器

1) 设置控制模式为配置模式;

2) 初始化仲裁域与数据域的传输速率及采样点;

3) 初始化發送请求、发送延迟补偿及中断等寄存器;

4) 初始化输出FIFO和输入FIFO及过滤器;

5) 设置控制模式为CAN FD模式。

3.1.2 数据处理及输出

数据处理主要是将输入的系统数据转换为符合对外通讯协议的数据格式,将符合通讯协议格式的数据写入控制器MCP2517FD的输出FIFO中,然后通过发送请求寄存器控制MCP2517FD将FIFO中的数据输出。流程图见图3。

3.1.3响应总线控制指令

从MCP2517FD的输入FIFO中读取接收到的指令进行判断,若指令符合接口协议,则依据协议执行指令,清除输入FIFO;若指令不符合接口协议,清除输入FIFO,不作任何处理。流程见图4。

3.2 SPI接口模块

FPGA和控制器MCP2517FD之间通过SPI接口进行通讯,FPGA为主控器,MCP2517FD为从控器,主要有四个信号:SCK-串行时钟;CS-片选;SDO-MCP2517FD送给FPGA的数据;SDI-FPGA送给MCP2517FD的数据。SPI接口选择0,0模式传输,传输时先传输数据最高位,在时钟信号的上升沿读取数据,传输的波特率由FPGA控制实现,满足不大于20MHz的要求,SPI数据传输时序见图5。

4结束语

本文提出了基于FPGA和控制器MCP2517FD的CAN FD总线接口的设计方案,并详细论述了硬件电路设计和软件设计实现方法,满足了系统对高速率通讯的需求,目前该设计方案已在某型高度表系统中得以成功应用。由于该设计方案采用模块化设计方法,同时控制器MCP2517FD兼容CANFD和CAN2.0B总线接口,因此通过简单的修改软件,就可以实现CAN总线接口。

参考文献:

[1] Microchip.ExternalCANFDControllerwith SPI Interface

[2] Microchip.CAN FD Module(MCP2517FD).2017.

[3] 张杰.CAN总线在汽车车身控制方面的设计和应用.中国知网.2007.

[4] 柯江民,孙淑霞,曹屹东.MCP2515及CAN通讯驱动设计.计算机应用.2008.