一种基于FPGA电路的扫频时间检测技术

牛红涛 黄建琼 张志峰 王巍 马轲瀛

摘 要: 时间频率技术已广泛应用于通信、仪表和自动控制系统等众多领域,为了改进低频方波信号的扫频时间检测技术,提出一种新的基于FPGA电路的扫频时间检测技术。详细介绍扫频时间检测装置的检测系统原理,并对扫频时间检测算法进行理论分析。设计基于FPGA控制芯片的扫频时间检测电路,实现低频扫频时间参数的自动检测功能。通过与高性能示波器测量方法得到的结果进行比较和分析,结果显示,该文提出的方法检测效率远远高于高性能示波器测量方法,且具有测量稳定及测量精度高的优点。在制动时间、转速、车速以及瞬时速度等参数的检测校准领域有重要的应用价值。

关键词: 扫频时间检测; 检测装置; 检测电路设计; 软件设计; 参数检测; 结果分析

中图分类号: TN98?34; TH71 文献标识码: A 文章编号: 1004?373X(2020)20?0014?04

A frequency sweep time detection technology based on FPGA circuit

NIU Hongtao, HUANG Jianqiong, ZHANG Zhifeng, WANG Wei, MA Keying

(National Institute of Measurement and Testing Technology, Chengdu 610021, China)

Abstract: The time frequency technology has been widely used in many fields such as communication, instrument, automatic control system, etc. A new frequency sweep time detection technology based on FPGA circuit is proposed to improve the frequency sweep time detection technology for low?frequency square signal. The principle of the detection system for frequency sweep time detection device is introduced in detail, and the frequency sweep time detection algorithm is analyzed theoretically. The frequency sweep time detection circuit based on the FPGA control chip is designed, so that the automatic detection function of the low?frequency sweep time parameter is realized. The results obtained by the measuring method of high?performance oscilloscope and the results obtained from the proposed method are compared and analyzed. The results show that the detection efficiency of the proposed method is much higher than that of the high?performance oscilloscope measurement method. It has the advantages of high measurement stability and high measurement accuracy, and has important application values in the detection and calibration fields of parameters such as braking time, rotational speed, vehicle speed and instantaneous speed.

Keywords: frequency sweep time detection; detection device; detection circuit design; software design; parameter detection; result analysis

0 引 言

随着国民经济的高速发展,时间频率相关技术已广泛应用于通信、仪表和自动控制系统等众多领域,与生产生活密切相关,在民用、工业、军事、航空航天等多个领域发挥着重要作用。在电子仪表及工业领域,变频信号的使用十分常见,如正弦波信号和方波信号等。这种周期信号可以作为基准信号广泛应用于转速测量、距离测量、通信系统或与时间频率相关的电路设计。用于产生变频信号的仪器有扫频信号发生器和函数信号发生器等装置,这些装置产生的信号幅度恒定,频率可在限定范围内做线性变化,对于研究转速、加速度、时基稳定度等参数的检测校准技术有重要意義。目前国内学者对扫频信号发生器开展了相关研究,已通过应用FPGA控制技术实现了扫频信号的输出[1?4]功能。此外,在汽车检测或电机检测领域,变频信号与转速密切相关,对瞬时速度、转速等参数的检测往往需要通过传感器将被测信号转换成方波信号进行检测,而信号频率变化之间的时间间隔,即扫频时间,则反应了汽车、发动机或电机的加速或减速性能。目前,已有许多学者开展了汽车性能检测技术研究,这些研究主要是关于汽车底盘测功机检测技术[5?8]。也有学者开展扫频时间检测技术研究,尤其是在汽车性能检测领域[9?10]。虽然国内开展了大量关于扫频信号发生器、汽车底盘测功机的研究,可是关于扫频时间检测技术的研究还较少,由于变频信号应用广泛,开展扫频时间检测技术研究具有重要的应用价值。

针对这一情况,本文开展了关于低频方波信号的扫频时间检测技术研究,提出了一种新的基于FPGA电路的扫频时间检测技术。通过应用提出的扫频时间检测算法以及利用FPGA并行数据处理的优势,能够实现低频扫频时间参数的自动检测,其检测效率远远高于高性能示波器测量方法,具有测量稳定及测量精度高的优点。在制动时间、转速、车速以及瞬时速度等参数的检测校准领域有重要的应用价值。

1 扫频时间检测装置设计

由于FPGA电路可以实现精密时间间隔的测量[11?12],为了实现变频信号之间的时间间隔检测,本文设计了一种基于FPGA电路的扫频时间检测装置,该装置应用信号滤波技术提高检测电路抗噪声能力,应用100 MHz的时钟频率进行扫频时间参数的测量,可以提高时间参数测量的精度,实现低频扫频时间参数的自动检测。

1.1 检测系统原理

扫频时间检测装置的系统原理如图1所示。

被测仪器或光电编码器产生的变频信号经过同轴信号线与扫频时间检测装置相连接,扫频时间检测装置通过阻抗匹配模块将被测方波扫频信号的电压转换至FPGA测量控制电路许可的电压范围5 V以内,由FPGA测量控制电路采用扫频时间检测算法实时对扫频信号进行处理和计算。设被测信号的频率从高到低变化,当被测信号的瞬时频率小于等于设定的频率起始点的数值时开始计时,当被测信号的瞬时频率小于设定的频率终止点的数值时结束计时,从而可以计算出扫频信号从高频变化到低频所经历的时间间隔,即扫频时间。

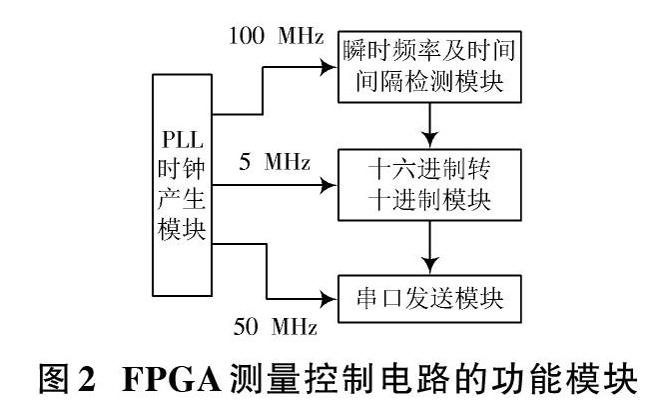

图1中FPGA测量控制电路是由PLL时钟产生模块、瞬时频率及时间间隔检测模块、十六进制转十进制模块以及串口发送模块构成,如图2所示。系统采用外部50 MHz晶振驱动PLL时钟产生模块,而PLL时钟产生模块为FPGA测量控制电路提供5 MHz,50 MHz和100 MHz共3种工作时钟。瞬时频率及时间间隔检测模块采用100 MHz工作时钟对被测方波信号进行实时频率检测,采用扫频时间检测算法对每一个连续的方波信号的上升边沿进行实时分析,如果被测信号频率达到设置的起始频率则启动计数器进行计时,当被测信号的瞬时频率达到设置的终止频率则停止计时,从而可以得到起始频率和终止频率之间的精确的时间间隔,实现对变频信号进行自动扫频时间检测功能。由于FPGA测量电路采用100 MHz时钟对被测信号进行实时分析计算,每隔10 ns对信号进行一次边沿检测,提高测量系统的精度。由于FPGA测量电路测量扫频时间间隔的计数器采用48位的二进制计数器,为了便于输出显示还需要将数据转换为十进制数据,系统设计了十六进制转十进制模块实现进制之间的转换功能,由于数据进制转换过程中耗时较多,需要较低的时钟频率。因此采用PLL提供的5 MHz时钟驱动。最后通过串口发送模块将转换后的十进制数据发送到上位机进行显示和分析。串口发送模块采用PLL产生的50 MHz时钟进行驱动,并在模块内部进行降频处理,得到串口发送需要的低频时钟信号,实现数据的发送功能。

1.2 扫频时间检测算法

在实际应用中往往需要将周期信号转换成方波信号来计算信号频率参数,因此本文主要研究方波信号的扫频时间检测算法。设f为连续的方波信号集合,可以表示为:

[f=fx1,fx2,…,fxm] (1)

式中,[fxk]为单个方波信号,可表示为:

[fxk=A, 0≤xk 式中:[A]表示方波信号的幅值;[T(xk)]为方波信号[fxk]的周期,而[k=1,2,…,m]。因此,连续方波信号周期的集合T可以表示为: [T=Tx1,Tx2,…,Txm] (3) 本文提出的扫频时间测量方法通过测量连续方波信号的瞬时频率来确定计时的起始点和终止点,而方波信号的瞬时频率可以通过测量信号的周期间接计算得到。对于频率随时间变化的方波信号,通过加窗函数的方法对信号进行截取,然后计算截取得到的若干个方波信号的周期,再将周期转换成瞬时频率,然后通过不断移动窗函数的位置就可以对整个连续方波信号进行瞬时频率的计算。对连续方波信号的周期集合T进行加窗函数运算,可得到处理后的信号周期集合[Tc],可以表示为: [Tc=Tcx1,Tcx2,…,Tcxm-n+1] (4) 式中, [Tc(xi)=k=ii+n-1WkT(xk)] (5) 式中:[i=1,2,…,m-n+1];而[W=[W1,W2,…,Wm]],本文设置[W1=W2=…=Wm=1]。在FPGA测量控制电路中,应用提出的扫频时间检测算法实时对连续的方波信号进行瞬时频率计算,对于某一个方波信号,通过计算该方波信号及其后连续的2个方波信号的频率平均值来确定该方波信号的瞬时频率。因此将式(5)中的n值设置为3。 2 FPGA电路设计 扫频时间检测装置采用Cyclone IV E系列EP4CE10F? 17C8控制芯片。该芯片具有功耗低和性价比高的优点,在仪器仪表类产品及工业控制产品中有重要的应用前景。该芯片中的M9K存储器模块具有9 Kbit的嵌入式SRAM 存储器,能够满足本项目系统运行过程中进行各种数据存储的需求。此外,通过使用芯片中的乘法器,便于實现更加高效的并行结构的扫频时间检测算法。除了核心架构资源,该芯片还拥有2个PLL时钟管理单元和多个系统I/O,便于对本项目系统电路时钟的管理。为了保障FPGA测量控制电路的正常运行,避免FPGA电路中的指令代码因掉电而丢失的情况,在系统上电后,通过主动串行方式(AS),由FPGA主动输出控制和同步信号发送给专用的串行芯片W25Q16。在串行芯片收到命令后,再把配置数据加载到FPGA电路的SRAM中,然后FPGA测量电路才能正常的工作。图3所示为FPGA主动串行方式配置电路的原理图。扫频时间检测装置在FPGA测量控制电路与被测方波信号连接端子处设有分压电阻,以限制被测信号的最高电压,从而实现对被测方波信号的扫频时间检测功能。 被测方波信号的扫频时间参数在FPGA测量控制电路中是以48位二进制数字的形式进行运算和处理的。为了便于上位机进行显示和处理,将扫频时间参数转换成十进制数据后,系统采用串口转USB芯片CH340G实现FPGA测量控制电路与上位機的数据传输功能。CH340G芯片是一种支持 5 V 或 3.3 V 供电的 USB 总线转接芯片,能够实现USB 转串口协议,支持通信波特率 50 b/s~2 Mb/s,可以通过一根普通的 USB数据线与上位机进行数据传输。串口转USB芯片CH340G与FPGA控制芯片的连接示意图如图4所示。 3 软件设计 基于FPGA电路的扫频时间检测装置采用了Cyclone IV E系列的FPGA控制芯片,其测量算法是通过Verilog HDL硬件描述语言实现的,主程序流程图如图5所示。软件工作原理是应用扫频时间检测算法通过信号上升沿来检测信号的瞬时频率,如果信号的瞬时频率满足设置的起始频率,则启动计时器开始计时。由于FPGA控制芯片的并行数据处理优点,信号处理电路还能实时对信号瞬时频率进行检测,当信号瞬时频率满足设置的结束频率时结束计时器计时功能,并将扫频时间数据转换成十进制数据形式发送给上位机进行处理和分析。在扫频时间检测软件中采用了2个脉冲宽度寄存器R1和R2交替连续的方波信号脉冲宽度进行计算,因此可以得到连续每一个方波信号的瞬时频率。图6所示为这种方波信号瞬时频率检测算法的ModelSim软件仿真图。 4 实验结果及分析 本文采用Keysight 33600A系列函数信号发生器来模拟频率线性变化的扫频信号,然后通过扫频时间检测装置和Tektronix MSO64混合信号示波器对该扫频信号同时测量,并对扫频时间测量结果进行比较和分析。通过函数信号发生器产生频率从70 kHz线性变化到10 kHz的扫频信号,扫频时间分别设置为10 s和20 s,那么信号频率从50 kHz线性变化到20 kHz需要的时间则分别为5 s和10 s。图7显示了函数信号发生器产生的频率从70 kHz线性变化到10 kHz的扫频信号截图。 本文采用混合信号示波器和扫频时间检测装置对频率从70 kHz线性降至10 kHz的变频信号进行扫频时间测量,设置扫频时间测量的起始频率和终止频率分别为50 kHz和20 kHz,对该信号进行3次扫频时间测量的平均值如表1所示。 通过比较可知,采用扫频时间检测装置和示波器测量方法都能得到准确的扫频时间参数,其测量结果非常接近,测量误差小于1 ms。可是,采用示波器测量方法需要将扫频信号进行连续存储,然后将存储的信号数据在计算机中通过Matlab软件采用类似的扫频时间检测算法进行分析计算,数据处理量较大。由于实验中使用的示波器的最大存储深度为62.5 MS样点,因此采样率最高可设为3.125 MS/s,而基于FPGA电路的扫频时间检测装置对信号进行分析的速率为100 MS/s。可以看出,采用示波器测量方法对扫频信号进行分析的频率远远低于基于FPGA电路的扫频时间检测装置,而且应用高端示波器检测方法来检测扫频时间参数需要对数据进行后处理,检测时间较长,不能实时显示测量结果;而采用基于FPGA电路的扫频时间检测装置能够实现对低频扫频信号扫频时间参数的自动检测。实验中还采用扫频时间检测装置对表1中的扫频时间信号进行11次测量,其测量结果的均方差低至1.5×10-4 s。因此,本文提出的基于FPGA电路的扫频时间检测装置具有很高的测量精度。 5 结 论 针对低频方波信号的扫频时间检测问题,本文提出了一种新的基于FPGA电路的扫频时间检测技术。详细介绍了扫频时间检测装置的检测系统原理,并对扫频时间检测算法进行了理论分析,设计了基于FPGA控制芯片的扫频时间检测电路,通过应用扫频时间检测算法以及利用FPGA并行数据处理的优势,能够实现低频扫频时间参数的自动检测。通过与高性能示波器测量方法得到的结果进行比较分析,结果显示本文提出的基于FPGA电路的扫频时间检测装置能够实时检测和显示扫频时间测量结果,其检测效率远远高于高性能示波器测量方法,具有测量稳定及测量精度高的优点。在制动时间、转速、车速以及瞬时速度等参数的检测校准领域有重要的应用价值。 参考文献 [1] 冷建伟,徐琼琼.基于单片机和FPGA的扫频信号发生器[J].化工自动化及仪表,2014,41(8):939?942. [2] 段惠敏,周泽华,查长军,等.基于FPGA和单片机的扫频信号源的设计[J].合肥学院学报(综合版),2018,35(2):51?55. [3] 朱科.基于DDS技术的扫频信号发生器设计与实现[J].工业控制计算机,2018,31(10):47?49. [4] 黄丽,刘永芳.基于FPGA和DAC的扫频信号发生器的研制[J].自动化与仪器仪表,2019(3):8?10. [5] 邬洋,刘嘉靖,刘海鹏,等.四驱汽车底盘测功机计量检测方法的研究[J].中国质量与标准导报,2017(12):91?93. [6] 张乐.汽车底盘测功机自检系统的设计[J].工业计量,2018,28(3):66?69. [7] 靳建波,卜树峰,李永军,等.基于电力测功机的电动车辆直驶负载模拟技术研究[J].计算机测量与控制,2018,26(5):261?265. [8] 叶青艳.基于单片机的汽车底盘测功机试验台检测系统设计应用[J].微型电脑应用,2019,35(9):151?154. [9] 朱卫民.滑行时间检测仪的研制[J].计量技术,2012(7):50?52. [10] 吕庆斌,刘嘉靖,邬洋,等.四驱汽车底盘测功机用滑行时间测试仪的研发与应用[J].中国质量与标准导报,2018(2):71?74. [11] 瞿鑫,吴云峰,江桓,等.基于FPGA的时间间隔测量系统的设计[J].电子器件,2013,36(6):825?827. [12] 马芸,郭芃.基于FPGA延迟时间插入法实现精密时间测量[J].现代导航,2013,4(5):317?322.