基于Innovus工具的28 nm DDR PHY物理设计方法

王秋实, 张 杰, 孟少鹏

(中国电子科技集团公司第三十八研究所, 安徽合肥 230088)

0 引言

DDR技术起始于2001年,之后广泛应用于各类芯片并成为主流。基于这个前提,双倍数据率物理层接口(DDR PHY)技术应运而生。DDR PHY成为存储控制器逻辑和DRAM颗粒物理接口间的通用规范接口,加速了DDR技术的发展。在芯片中,DDR PHY通常作为一个独立模块单独设计[1]。

集成电路设计分为前端设计和后端设计。前端设计包含系统架构设计、子模块设计、硬件描述语言实现及功能仿真验证等。后端设计是将前端设计映射到可加工的硅工艺的过程,包括综合、布局、电源布线、标准单元摆放、时钟树综合、绕线等[2]。

DDR PHY的物理设计流程与全芯片的物理设计流程相同。针对28 nm工艺的特殊性,我们特别定制了一些设计流程,包括在布局阶段插入特殊的物理单元(Physical Cell)、时钟树绕线层(NDR)的选择、绕线策略的更改等[3-4]。DDR PHY的物理设计的关键在于时序路径的设计,时序路径质量的好坏将严重影响DDR系统的性能。

本文首先在第一节介绍所用DDR PHY的架构,第二节描述了DDR PHY的时序路径及其后端设计的难点,第三节提出了基于Innovus工具的解决办法,最后总结全文。

1 DDR PHY简介

本文中的DDR PHY是我单位采购的商用“半硬核”IP,基于28 nm流片生产。它能够提供与JEDEC标准的DDR3和DDR4 SDRAM通信的完整物理接口,最高数据率为1 400 Mbps。

之所以称之为“半硬核”IP,是因为整个DDR PHY基于slice构成,IP开发商提供已经固化完成的slice模块。slice模块是DDR控制器和DRAM颗粒的“桥梁”,整个DDR PHY使用到的slice模块种类包括:

(1) Data slice (8 DQ/1 DM/1 DQS),负责数据信号的串并转换;

(2) Address/control slice (4 control/address),负责地址信号的转换;

(3) Address/control master slice,负责控制各个Address/control slice;

(4) Memory clock slice,负责时钟信号的转换。

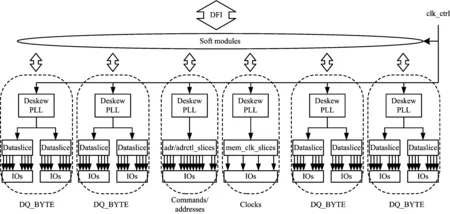

图1是DDR PHY的结构图。除slice模块之外,整个DDR PHY还包括一些数字模块,称之为soft module,包括DFI接口、配置接口、内部寄存器等,构成存储控制器和slice模块之间的电路。

图1 DDR PHY的结构图

2 时序路径的设计难点

DDR PHY的输出信号包括数据信号、地址信号、地址控制信号、时钟信号等,每一条从时钟输入管脚到这些输出信号的路径都是需要重点关注的时序路径。

归纳来说,DDR PHY中的时序路径可以分为如下5段:

Stage 1:时钟输入端clk_ctrl到deskew PLL;

Stage 2:deskew PLL到slice模块时钟端;

Stage 3:slice模块时钟端到内部寄存器CK端;

Stage 4:slice模块内部寄存器到slice模块输出端;

Stage 5:slice模块输出端到IO。

DDR PHY需要为存储控制器逻辑和DRAM颗粒之间提供高速、稳定、可靠的数据通信,这对时序路径的整体延时、不同路径之间的延迟差等设计指标提出了苛刻的要求。

2.1 时间预算

时间预算就是在时序路径中分配延时的过程。由于各个slice模块已经固化,因此Stage 3和Stage 4的延迟已经固定。为保证达到设计目标,在设计初期需要时序路径中其他阶段的延时进行合理的规划。

2.2 延时优化

DDR的存取时间代表了读取数据所延迟的时间,与时序路径的整体延时直接相关。从设计指标上来说,存取时间越小则越优。

在布局阶段,通过将deskew PLL与slice模块就近摆放来减小Stage 2的延时;通过将slice模块与IO单元就近摆放来减小Stage 5的延时。

2.3 路径对齐

路径对齐是DDR PHY时序路径设计的最大难点。如图2所示,在所有延迟角落下,路径对齐要求如下:同一个data slice和同一个address slice的输出信号间的延迟偏移均不能超过75 ps,同一个address control slice的输出信号间的延迟偏移不能超过85 ps;memory clock slice的输出信号的延迟要大于所有data slice和address slice的输出信号间的延迟,且它们之间的延迟偏移不能超过125 ps;address slice、address control slice和memory clock slice的输出信号间的延迟偏移不能超过150 ps;所有DDR PHY的输出信号之间的延迟偏移不能超过170 ps。

图2 DDR PHY路径对齐要求

3 基于Innovus的设计方法

Innovus为CADENCE公司于2015年发布的全新后端物理设计平台,基于该平台可以进行从RTL到GDSII的全流程实现,采用平台内嵌命令结合LINUX可以很方便地实现对数字电路网表文件的编辑[5]。

本节将结合项目实例从4个方面来阐述DDR PHY时序路径设计难点的解决方法。

3.1 使用DCCK单元

DCCK单元为专门设计的带耦合电容的时钟树驱动单元,具有如下优点:单元延迟经过优化,保证时钟路径的延迟尽可能的小;具有对称的上升时间和下降时间,保证了延时链的精度;由于耦合电容的存在,使时钟树的时钟延迟、传输时间、时钟偏移等参数不易受电源波动影响。

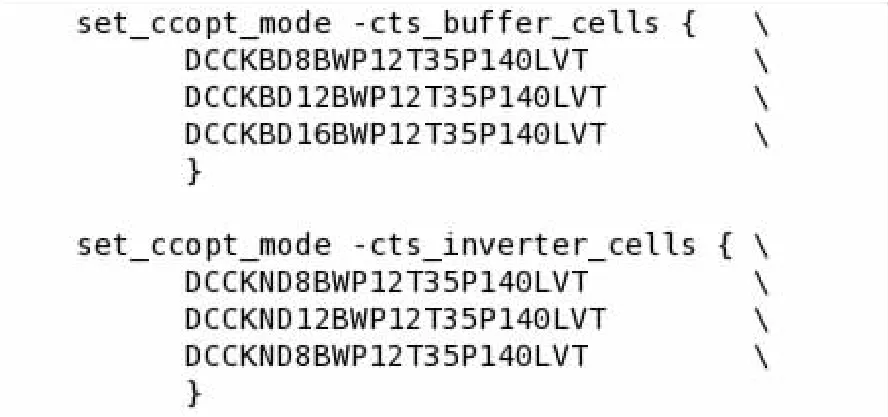

项目选取DCCK单元中阈值电压为LVT、驱动能力为X8/12/16的缓冲器(buffer)和反相器(inverter)作为DDR PHY时钟路径的驱动单元,方法如图3所示。

图3 使用DCCK单元的设置脚本

3.2 利用insertion delay

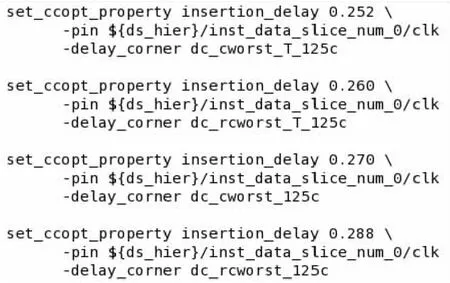

如前文中所说,各个slice模块已经固化,slice模块时钟输入端到slice模块内部寄存器CK端的时钟树路径(即Stage 3)已经固定,项目使用insertion delay代表该部分时钟树的延迟。

项目使用create_ccopt_macro_model_spec命令将传统cts引擎的macro model delays转换成ccopt引擎中的insertion delay。需要注意的是,为了保证时钟树设计的精确性,需要在多模式多角落(MMMC)下设置insertion delay。图4为使用insertion delay的部分设置脚本。

图4 使用insertion delay的设置脚本

3.3 创建skew group

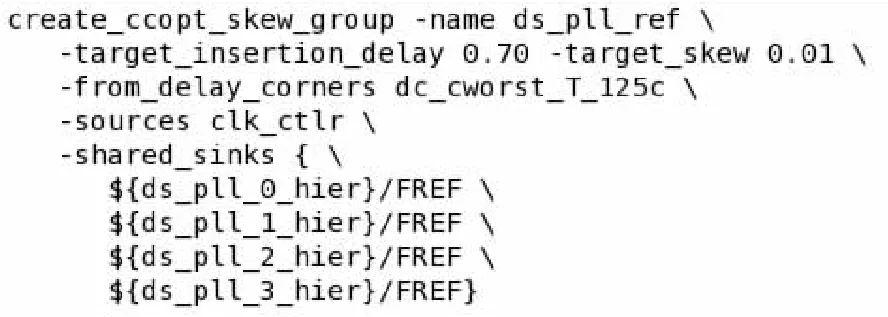

在ccopt中,skew group可以看作整个时钟树的子时钟树,用户可以根据需要定制leaf pin、insertion delay、target skew等参数。

为了满足2.3节提到的路径对齐要求,项目创建不同的skew group来调整不同类别时序路径的延时。主要进行延时调整的时序路径为时钟输入管脚clk_ctrl到deskew PLL的时钟树路径(即Stage 1)。图5所示为将所有data slice的deskew PLL的参考时钟输入端创建skew group。

图5 创建skew group脚本

3.4 手工调整

为了使deskew PLL到slice模块时钟端(即Stage 2)的延时尽可能小,需要手工调整该段路径上时钟缓冲器的位置,使时钟走线结果达到最优。

在最终的设计结果仍然无法达到路径对齐的要求但不是很大的情况下,可以根据静态时序分析(STA)结果手工添加缓冲器来调整,主要进行手工调整的时序路径为slice模块输出端到IO的数据路径(即Stage 5)。

3.5 设计结果

DDR PHY最终的PPA(Performance, Power, Area)结果为:

(1) 尺寸为:宽8.7 μm,高1.4 μm;

(2) 工作频率700 MHz,速率1 400 Mbps;

(3) 功耗1.5 W,静态电压降1.3%。

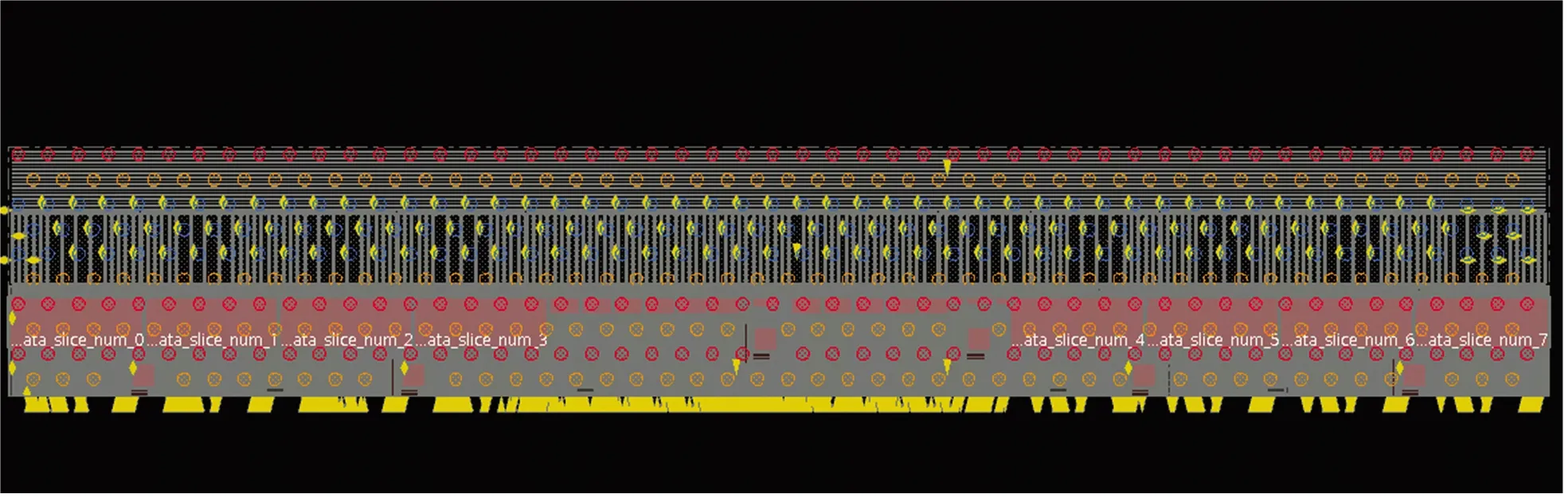

图6为DDR PHY完成物理设计后的结果局部图。

图6 DDR PHY物理设计结果图

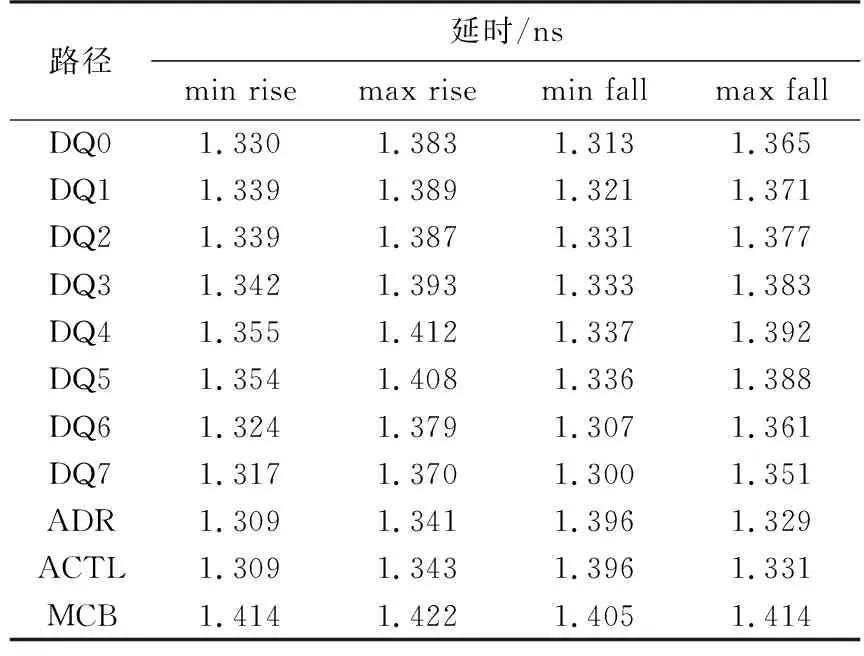

表1为延迟偏移最大的工艺角情况下各时序路径的延时信息。从表中可以看出,所有DDR PHY的输出信号之间的延迟偏移为122 ps,满足170 ps的设计要求。

表1 时序路径的时序预算

4 结束语

集成了该DDR PHY的一款工业级DSP已经成功流片并通过测试,在测试板上,DDR系统能够稳定运行在1 400 Mbps速率上。测试结果进一步证明了本文提出的DDR PHY物理设计方法的可行性和有效性。另外,随着工艺推进到12 nm及对DDR PHY的速率要求提升到3 200 Mbps,本文提出的物理设计方法还有进一步的提升空间。