一种超低功耗的全CMOS基准电压源设计

王梓淇 王永顺 陈昊

摘 要: 基于SMIC 0.13 μm CMOS工艺,设计一款纳瓦级功耗的全CMOS带隙基准电路。该电路由全CMOS电路实现,避免使用三极管和电阻,实现了节省芯片面积的目的。晶体管工作在三极管区和亚阈值区,大幅降低了功耗。Cadence仿真结果表明:在-20~100 ℃范围内,温度系数为31 ppm/℃;在电源电压1.2~3.3 V的变化范围内,电源电压漂移系数为0.42%/V。参考电源电压下,电路的电源抑制比(PSRR)达到51.7 dB@100 Hz;室温下,电路总静态电流为22.8 nA,功耗为27.4 nW@1.2 V;该电路可调节性强,适用于低功耗芯片中。

关键词: 全CMOS; 带隙基准; 基准电压源; 电路设计; 超低能耗; Cadence仿真

Abstract: A nava?level power?consumption full?CMOS band?gap reference circuit is designed based on SMIC 0.13 μm CMOS technology. The circuit is realized by full?CMOS circuit, and the use of BJTs and resistances has been avoided, and the chip area has been saved. The transistor works in the triode region subthreshold region, which greatly reduces the power consumption. The Cadence simulation results show that the temperature coefficient is 31 ppm /℃ when the temperature ranges from -20 ℃ to 100 ℃. The drift coefficient of power supply voltage is 0.42%/V within its range from 1.2 V to 3.3 V. The circuit′s PSRR can reach 51.7 dB@ 100 Hz under the reference voltage. At room temperature, the total quiescent current of the circuit is 22.8 nA, and the power consumption is 27.4 nW@1.2 V. This circuit has strong adjustability and is suitable for the low?power consumption chip.

Keywords: full CMOS; band?gap reference; reference voltage source; circuit design; ultra?low power consumption; Cadence simulation

带隙基准电路是每个模拟电路的核心组成部分之一。带隙基准的输出电压要求不随电源电压的变化而变化,为后续模块提供稳定的输入电压和电流。可穿戴集成电路应用非常广泛,小到智能手表,大到人体肢体助力机器人应用的兴起。集成电路设计对带隙基准电路提出了更低的功耗、更高的稳定性等要求[1]。

带隙基准的应用非常广泛,如在AD/DA,DC?DC,LDO等集成芯片中,在设计上可大致分为两大类:全CMOS带隙基准和非全CMOS带隙基准。本文提出一款全CMOS带隙基准,不包含三极管(BJTs)和电阻(Resistances)。 随着工艺的进步,工艺尺寸越来越小,晶体管启动所需要的阈值电压([VTH])也随之降低,但是亚阈值电压变化范围较大,给设计带来了一定的难度。

如今很多晶体管和电路结构不再需要1.2 V的基准电压,在这样的趋势下,全CMOS带隙基准电压源得到迅速发展。这种结构大幅减小了芯片面积,节约成本。本设计基于SMIC 0.13 μm工艺,实现了良好的温漂系数及超低功耗。

1 电路设计

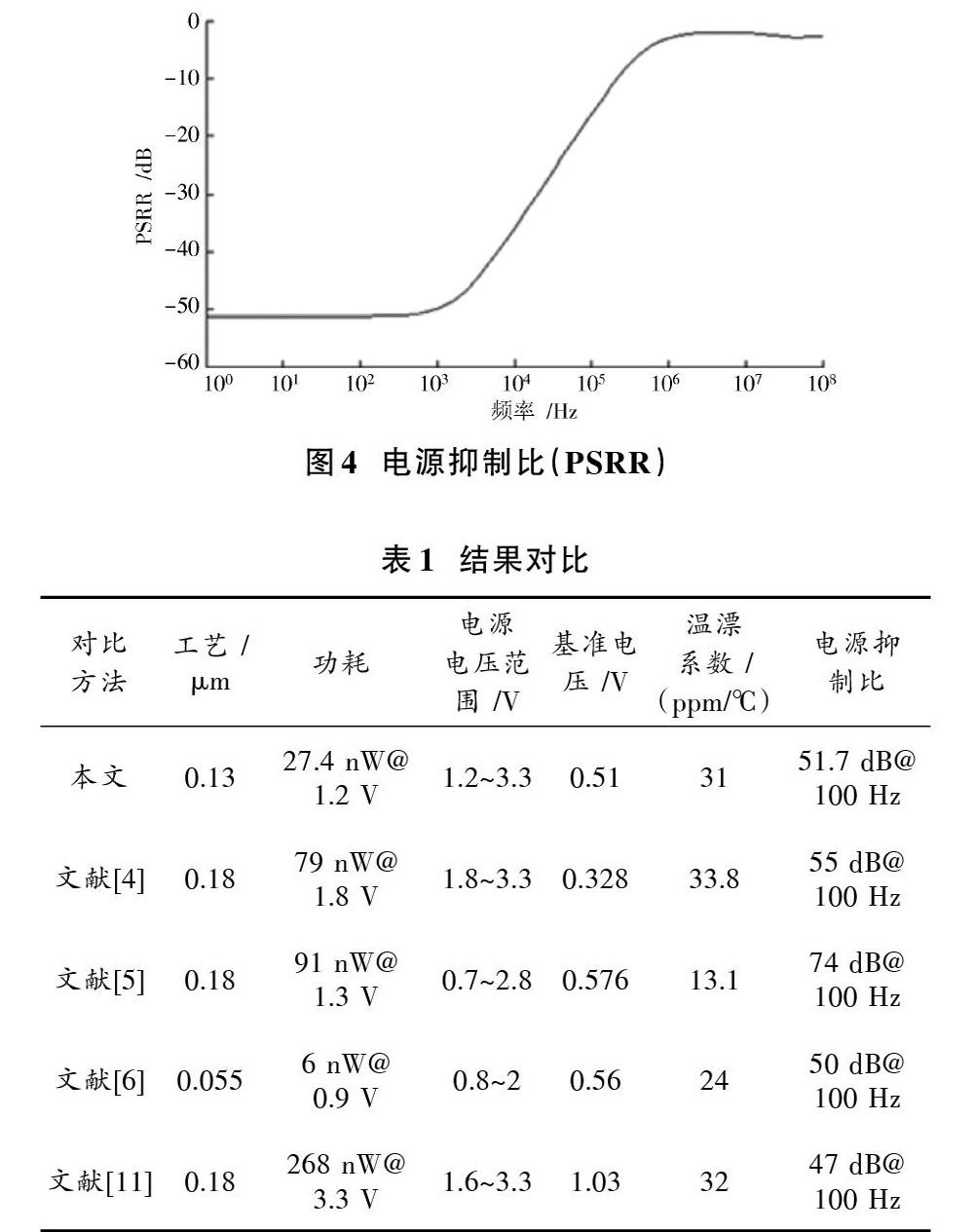

本次设计的电路结构如图1所示,包括启动电路[2]和带隙基准核心电路。

启动电路是使电路进入正常工作状态的必要组成部分,由晶体管PM1,PM2和NM1构成。主体基准电压核心电路由晶体管PM3~PM7和NM2~NM10构成。

1.1 亚阈值区工作原理

MOS管在亚阈值区的工作状态是栅源电压([VGS])小于阈值电压([VTH]),即:

式中:[μ]是载流子迁移率;[Cox]是栅氧层电容;[VT]是热电压,表示为[VT=kBTq],[kB]是玻尔兹曼常数,[q]是电荷数,[T]是绝对温度[3]。当[VDS]约为[VT]的3倍时,[exp-VDS VT≈0] ,亚阈值电流[I]可以简化为:

1.2 核心电路工作原理

完整的电路已在图1给出,由启动电路和核心电路组成,下面是核心电路的原理分析。基准电压产生的电路由一个PTAT电流电路和负载电路构成,其中PM3~PM5和NM2~NM7是PTAT电路,PM6~PM7和NM8~NM10是负载电路。特别是NM3工作在三极管区(强反型),其[VDS_NM3?VGS_NM3 -VTH]。此时,NM3作为一个可调电阻使用,从而调节正向电压的最大值。其余晶体管全部工作在亚阈值区,实现纳安级电流,流经NM3的电流为[Ia]。为保证实现电路工作正常,NM2和NM4~NM7为NM3提供[VDS_NM3],表达式为:

有源负载电路由NM8~NM10组成,其中NM8为NM3提供偏置电压,NM9和NM10用于调节负向输出电压。PM6和PM7为电流镜电路,用于镜像电流[Ia]。需要调整[KP6]和[KP7],得到合理的[KP6KP3]和[KP7KP3],使得NM8工作在饱和区。NM8的电流[INM8]根据上述原理,可以得到:

1.3 启动电路工作原理

在图1中将PM1的栅极接地,漏极接NM1的栅极,将NM1作为电容使用,所以晶体管面积略大,但比直接使用电容要节省面积[1?2]。电路工作之初,PM1的栅电压为0,随后PM1导通,PM2开始工作,基准电路开始工作,即PM2的漏极给PM3一个启动电流,随后PM1关断。此时NM1的栅极电压由于PM1的充电,已增大到VDD,因此启动电路的两个PMOS晶体管截止,启动电路不再工作。

2 结果分析

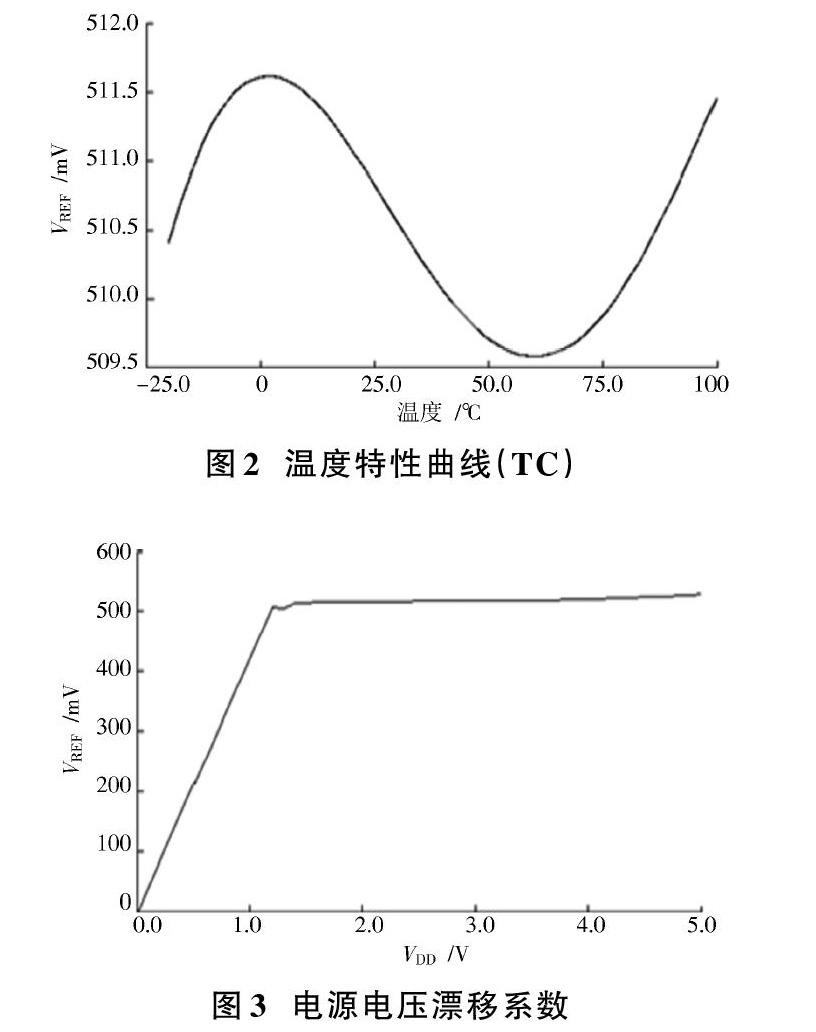

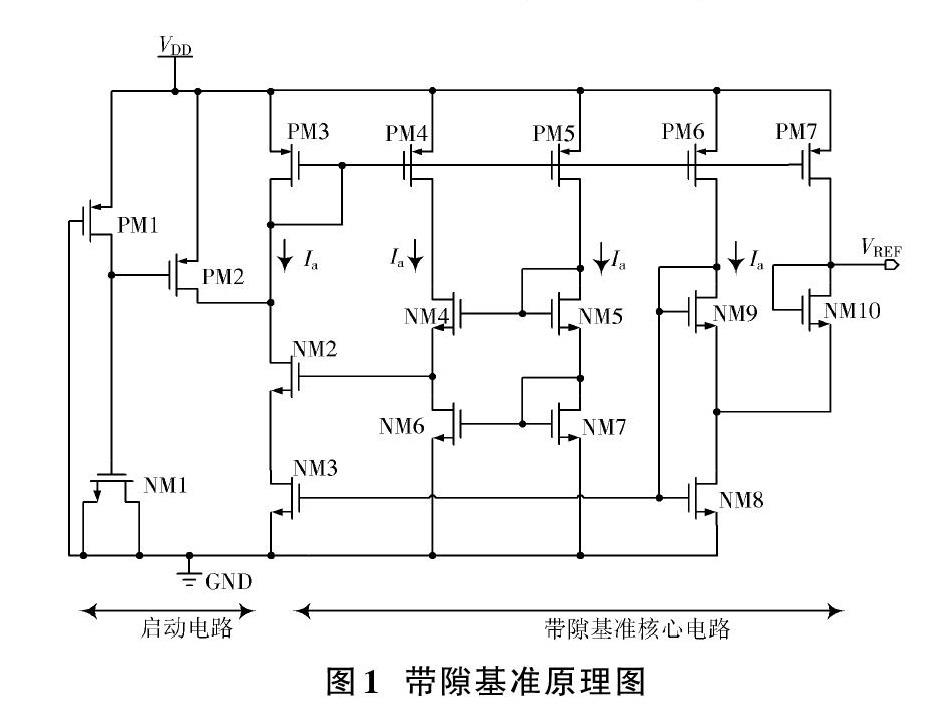

本设计基于SMIC 0.13 μm CMOS工艺,采用Cadence Spectre进行仿真。图2~图4是输出电压[VREF]的温度特性曲线(TC)、电源电压漂移系数和PSRR的仿真结果。由图2的仿真结果,计算得到了-20~100 ℃的温度范围内温漂系数为31 ppm/℃,基准电压为510 mV。图3中,在1.2~3.3 V的电源电压范围内,电源电压漂移系数为0.42%/V。

图4展示了基准电路的PSRR,在低频下为51.7 dB@100 Hz。表1列举了4篇主要参考文献的结果对比,实现了纳瓦级的超低功耗和良好的温漂。

3 结 论

本文设计的电路结构实现了超低功耗和良好的温漂系数,这种基准电压电路可应用于各种超低功耗芯片中。在-20~100 ℃范围内,带隙温漂系数为31 ppm/℃;电源电压在1.2~3.3 V变化范围内时,电源电压漂移系数为0.42%/V。参考电源电压下,PSRR达到51.7 dB@100 Hz。室温下,静态电流为22.8 nA,功耗为27.4 nW@1.2 V。

参考文献

[1] 黄静,杨羽佳,王玉娇,等.一种自偏置全集成的低功耗带隙基准电路设计[J].半导体技术,2019,44(7):494?499.

[2] 刘锡锋,孙萍,居水荣,等.一款全CMOS结构低功耗亚阈带隙基准源[J].半导体技术,2018,43(9):645?651.

[3] XU Yusen, HU Wei, HUANG Fengying, et al. Design of a novel all?CMOS low power voltage reference circuit [C]// 2013 IEEE 10th International Conference on ASIC. Shenzhen: IEEE, 2013: 17?23.

[4] DUAN J H, ZHU Z Y, DENG J L, et al. A novel 0.8?V 79?nW CMOS?Only voltage reference with ?55?dB PSRR @ 100 Hz [J]. IEEE transactions on circuits and systems II: express briefs, 2018, 65(7): 849?853.

[5] GUO J P, LI W M, LI Y C, et al. A 70?nA 13?ppm/°C All?MOSFET voltage reference for low?power IoT systems [C]// 2018 IEEE International Symposium on Circuits and Systems. Florence: IEEE, 2018: 205?251.

[6] 胡安俊,胡晓宇.一种超低功耗全CMOS基准电路[J].电子设计工程,2019,27(1):14?18.

[7] ALHASSAN N, ZHOU Z, S?NCHEZ?SINENCIO E. An All?MOSFET voltage reference with?50?dB PSR at 80 MHz for low?power SoC design [J]. IEEE transactions on circuits and systems II: express briefs, 2017, 64(8): 892?896.

[8] ZHU Y M, LIU F, YANG Y J, et al. A?115dB PSRR CMOS bandgap reference with a novel voltage self?regulating technique [C]// Proceedings of IEEE 2014 Custom Integrated Circuits Conference. San Jose: IEEE, 2014: 1?4.

[9] LI J, LI J C, YANG L. A nanopower, high PSRR full CMOS voltage reference circuit consisting of subthreshold MOSFETs [C]// 2015 IEEE 11th International Conference on ASIC. Chengdu: IEEE, 2015: 1?4.

[10] 周茜,邓进丽,岳宏卫,等.一种超低温漂低功耗全CMOS基准电压源[J].微电子学,2017,47(6):769?773.