一种低成本高可靠的星载计算机存储器容错方法*

吕 岩

0 引 言

一般而言,星载计算机系统主要由:处理器、程序存储器、数据存储器等部分组成.

传统的星载计算机系统一般选用高等级器件,程序存储器一般选用对单粒子免疫的反熔丝型器件,数据存储器(static random-access memory,SRAM)一般选用抗单粒子阈值高的器件,或者通过错误检测与纠正(error detection and correction,EDAC)等技术来对抗单粒子翻转[1].通过提高单个元器件可靠性的方式来提高整个计算机系统的可靠性,这种方式的优点是可靠性高,代价是成本高昂.

随着航天技术的发展,商用现货(commercial off-the-shelf,COTS)器件凭借着成本低,集成度高等优点,应用日益广泛.目前商业卫星公司通常采用降低器件质量等级的方式来降低成本.由于COTS器件大多采用塑封形式,存在吸潮、爆米花效应等问题,其可靠性相对较低,且由于未针对航天应用环境进行特殊设计,其抗空间环境能力也较弱,在轨易发生因单粒子、总剂量等问题导致的在轨异常[2-4].鉴于此,商业卫星在设计时一般会对COTS存储器件有容错措施,但大部分容错只限于存储器单芯片内的软件多模技术,比如在存储器中存放多份程序代码冗余,用来对抗单粒子翻转导致的系统无法启动[5],此方法只能在一定程度上对抗单粒子翻转,不能够对抗存储器单芯片失效,而存储器单芯片失效也就意味着整个计算机系统的失效.因此,选用COTS器件虽然可以降低计算机成本,但也降低了系统的可靠性.

目前提高计算机系统可靠性的方法主要有三模等技术,即对计算机系统进行整机三模[6],该方法可大幅提高系统的可靠性,但付出的代价很大,需要同时配置三套计算机系统,体积大,重量大,功耗高,带来的附加成本较高,在商业卫星领域不易推广.

针对此问题,对于低轨应用场景,提出了一种设计方法,利用COTS器件,通过程序存储器和数据存储器双冗余的方式来提高计算机系统的可靠性.相比于计算机系统三模,本设计付出的代价较小,仅需要增加两片存储器即可对计算机系统的可靠性和抗空间环境能力有较大提升,且系统具有优异的容错能力,即便单个存储器失效,系统也能够正常运行.

1 系统组成

在计算机系统中,受器件复杂度等因素影响,失效率高的器件主要为:程序存储器、数据存储器和处理器.其它器件诸如电阻、电容、电源、逻辑门电路等器件失效率相对较低[7].考虑到处理器的重要性,一般商业卫星都会选用高等级器件作为处理器.因此,在提高可靠性方面我们主要对低等级的程序存储器和数据存储器进行可靠性加固,代价小,收益高.

由于低等级的程序存储器和数据存储器多为塑封器件,存在吸潮、爆米花效应等问题,长时间在轨应用有失效的风险[8].因此对其进行了双冗余.由于COTS器件自身抗空间环境能力相对较弱,在轨易发生单粒子翻转.因此,选用了芯片自身带有错误检查与纠正(error correcting code,ECC)功能的存储器件.

综合以上原则,本设计的计算机系统主要由以下几部分组成:处理器(高等级器件)、双冗余SRAM(COTS器件)、双冗余NOR FLASH(COTS器件).其中SRAM选用两片同样规格的带ECC纠检错功能的SRAM,FLASH选用两片同样规格的带ECC纠检错功能的NOR FLASH,两片SRAM和FLASH均同时工作.系统框图如图1所示.

图1 计算机系统组成框图Fig.1 Computer system function block diagram

2 系统设计

2.1 硬件设计

处理器选用ACTEL的SmartFusion2系列片上系统FPGA,内部集成了166MHz的Cortex-M3硬核处理器,资源丰富,体积小,功耗低[9],有过大量飞行验证.本设计选用SmartFusion2系列的M2S050T-1FGG484M型处理器.

程序存储器选用CYPRESS公司生产的NOR FLASH,可存储Boot程序和应用程序,芯片选型为S25FL512SAGBFI211,容量512 Mbit,芯片自带ECC功能,每16bytes可以纠正1bit数据位翻转,ECC纠检错状态可以通过访问FLASH的ECC寄存器来查看.芯片采用串行外设接口(serial peripheral interface,SPI),Quad模式下读取速率可以达到104 MHz.

数据存储器选用ISSI公司生产的SRAM,可用于运行计算机程序,芯片选型为IS61WV102416EDBLL-10B2L,容量16Mbit,自带ECC纠检错功能,每1byte可以纠正1bit数据位翻转,芯片输出ECC纠检错状态管脚ERR,用高低电平来表征当前是否发生ECC纠检错.SRAM的访问速度可达到100 MHz.

计算机系统搭建原理如图2所示.

图2 计算机系统原理图Fig.2 Schematic diagram of computer system

2.2 程序运行设计

NOR FLASH作为程序存储器,将引导程序和应用程序拷贝相同的两份存放在两片NOR FLASH中,FPGA主要实现CPU与FLASH之间的地址转换以及2片FLASH数据的表决.处理器加电后,CPU通过FPGA映射地址从FLASH中加载,将FLASH中存放的应用程序加载到SRAM中,完成程序加载后,CPU从SRAM中运行.

2.2.1 程序加载

M2S050T处理器CPU主频设置为128MHz,处理器在启动时对程序加载速度一般无特殊要求,设置访问FLASH为64个等待周期,即CPU对FLASH的访问周期为496ns.FLASH在Quad模式下单次访问耗时21ns.读取FLASH的ECC状态寄存器需要采用FAST READ方式,单次访问耗时421ns.

在CPU一个取指周期内,FPGA依次完成以下操作:

T1阶段:FPGA将CPU的访问地址映射给2片FLASH并判读2片FLASH给出的数据是否一致;

T2阶段:FPGA判读两数据一致则将FLASH1数据映射给CPU,如果不一致则访问2片FLASH的ECC寄存器状态;

T3阶段:FPGA将ECC寄存器状态正确的FLASH数据映射给CPU.

一个取指周期内,各阶段所耗费的时间如图3所示.

图3 CPU程序加载一个取指周期Fig.3 CPU program loads addressing cycle

程序加载流程如图4所示.

2.2.2 程序运行

M2S050T处理器CPU主频设置为128MHz,星上平台应用场景,一般设置SRAM为4个等待周期即可满足大部分应用需求,即CPU对SRAM的访问周期为31ns.SRAM的单次读写耗时10ns.

图4 CPU程序加载工作流程Fig.4 CPU program loading workflow

在CPU一个SRAM访问周期内,FPGA依次完成以下操作:

T1阶段:FPGA将CPU的访问地址映射给2片SRAM并判读2片SRAM给出的数据是否一致;

T2阶段:如果数据一致则将SRAM1给出的数据映射给CPU,如果不一致则判读2片SRAM的ERR管脚状态;

T3阶段:FPGA将ERR状态正确的SRAM数据映射给CPU,同时FPGA将错误的SRAM数据回写并纠正.

一个访问周期内,各阶段所耗费的时间如图5所示.

图5 CPU程序运行一个取指周期Fig.5 CPU program runs addressing cycle

程序运行流程如图6所示.

图6 CPU程序运行工作流程Fig.6 CPU program operation workflow

3 容错分析

针对COTS器件在轨易发生的故障进行了分析和对比,见表1.

由表1可知,采用本设计的计算机系统,基本可抵御在轨的常见异常,且对抗单粒子翻转的鲁棒性更强,能够容忍单bit或多bit翻转,因此,在容错方面,本设计要优于传统的计算机系统.

4 可靠性预计

根据GJB/Z 299C-2006电子设备可靠性预计手册,在计算机系统中,受器件工艺复杂度等因素影响,计算机系统中失效率较高的器件主要为:程序存储器、数据存储器和处理器等大规模集成电路.其它器件诸如电阻、电容、电源、逻辑门电路等器件其失效率相对较低.因此我们将计算机核心部分简化成以下模型,如图7所示.

表1 计算机在轨易发生的故障分析对比Tab.1 Analysis and comparison of computer-prone faults

由上图可知,传统计算机或商业卫星计算机系统可简化为串联模型,任何一部分失效,均会导致系统失效.

由上图可知,本设计计算机系统可简化为串并联混合模型,只有两片SRAM或FLASH同时失效,才会导致系统失效.

对比两个模型可知,除SRAM和FLASH连接方式不同外,其余部分两个模型均为串联模式(两个模型的Ra、Rb可靠性相同).因此,为了突出两种模型的对比情况,下面仅针对两种模型的SRAM和FLASH进行局部可靠性预计.

图7 传统计算机或商业卫星计算机可靠性简化模型1Fig.7 Traditional computer or Commercial satellites computer reliability model 1

图8 本设计计算机可靠性简化模型2Fig.8 Computer reliability model 3 of the paper

根据GJB/Z 299C-2006电子设备可靠性预计手册,进口集成电路的失效率计算公式为[7]:

λp=(C1πT+C2πE)πQ

(1)

其中:λp表示模型中各器件的失效率;C1表示电路复杂度失效率,10-6/h;πT表示温度应力系数;C2表示封装复杂度失效率,10-6/h;πE表示环境系数;πQ表示质量系数;

根据式(1)查表并计算等规模的宇航级和工业级芯片的失效率如表2所示.

根据可靠性预计公式[10]:

(2)

其中:RS(t)表示模型中存储器部分总的可靠性;Ri表示模型中各部分的可靠性;λi表示模型中各器件的失效率;t表示模型中器件的工作时间;Rflash1表示FLASH的可靠性;Rsram1表示SRAM的可靠性。

表2 等规模的宇航级和工业级芯片的失效率计算Tab.2 Calculation of failure rates of aerospace-grade and industrial-grade chips of equal scale

模型1中存储器由SRAM和FLASH两部分组成,任意一片SRAM或FLASH失效均会导致系统失效,由式(2)可知,其失效率为SRAM和FLASH的总和,可靠性为两部分可靠性的乘积,因此模型1存储器部分总的可靠性为[10]:

RS(t)=e-(λsram+λflash)×t

(3)

其中:λsram表示SRAM的失效率;λflash表示FLASH的失效率;

模型2中存储器由SRAM和FLASH两部分组成,即:两片SRAM并联,两片FLASH并联,之后二者再串联.只有两片SRAM或两片FLASH均失效才会导致系统失效,模型2中并联部分的可靠性为[10]:

(4)

其中:RS2(t)表示并联部分的可靠性;因此,2片FLASH并联后的可靠性为:

Rflash2(t)=1-(1-e-λflash×t)2

(5)

2片SRAM并联后的可靠性为:

Rsram2(t)=1-(1-e-λsram×t)2

(6)

综上,模型2存储器部分总的可靠性为:

[1-(1-e-λflash×t)2]×[1-(1-e-λsram×t)2]

(7)

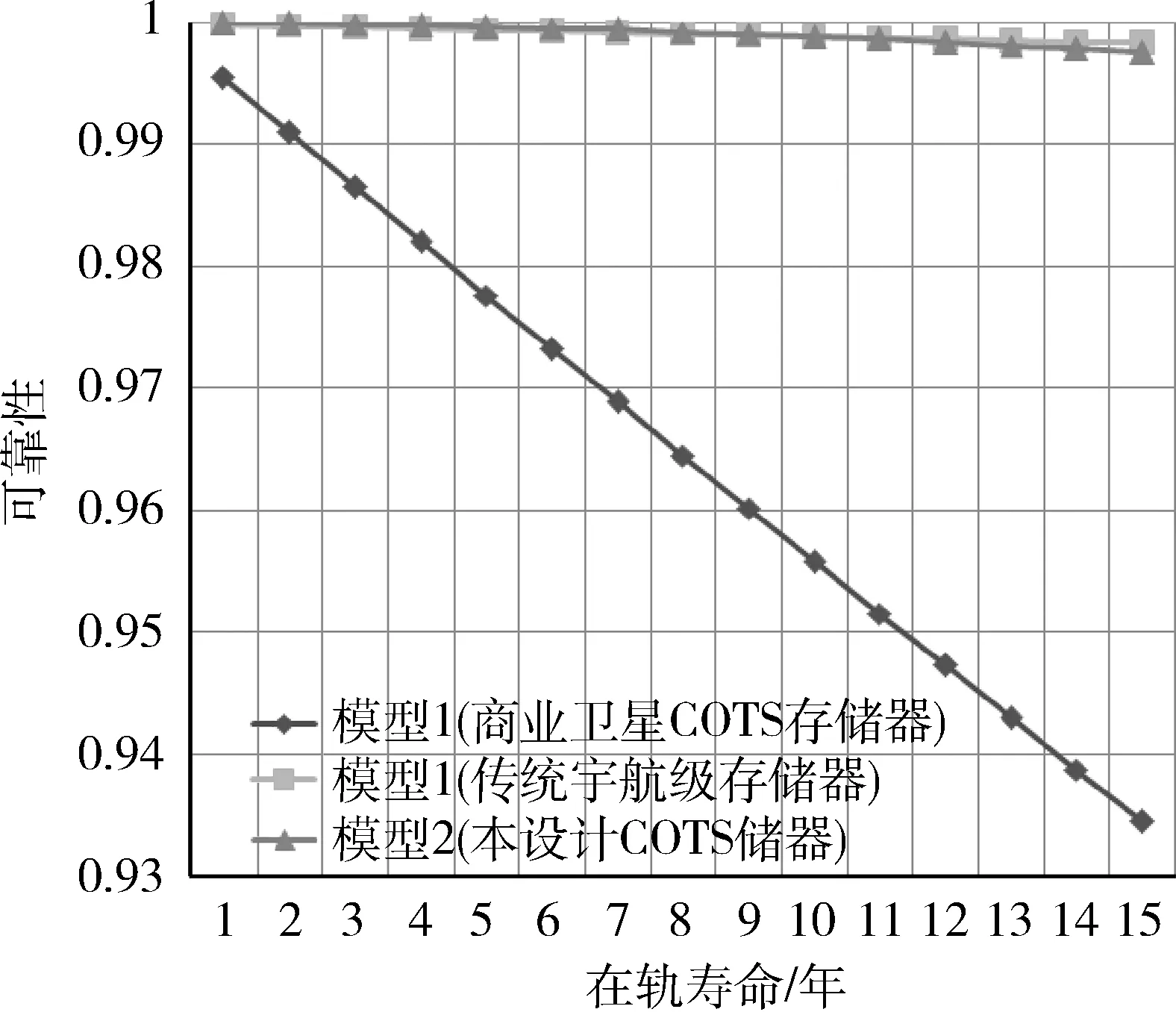

根据式(3)和(7)计算得到,2个模型的存储器部分可靠性预计曲线如图9所示.

图9不同模型可靠性预计曲线Fig.9 Computer reliability model 3 designed in the paper

以卫星在轨15年寿命为例,寿命末期各模型的存储器部分可靠性和失效率计算见表3.

表3 不同模型的计算机系统可靠性预计(存储器部分)Tab.3 Reliability predictions of computer systems with different models(memory section)

由上表可知,15年寿命末期,采用本设计的计算机系统存储器部分的失效率为0.0184/10-6h,与传统宇航级器件的失效率0.0126/10-6h相当,比商业卫星计算机系统存储器失效率0.5161/10-6h降低96.4%,失效率大大降低;

由上表可知,15年寿命末期,采用本设计的计算机系统存储器部分的可靠性为0.9976,与传统宇航级计算机系统可靠性0.9983相当,比一般商业卫星计算机系统整体可靠性0.9344提高约6.7%.

5 结 论

针对星载计算机低成本和高可靠的矛盾问题,本文提出了一种解决方法,在低成本器件的基础上,利用程序存储器和数据存储器双冗余的方式来提高计算机系统的可靠性、容错能力以及抗空间环境能力,采用本设计的计算机其存储器部分的可靠性与传统宇航计算机相当,成本与商业卫星计算机相当,实现了低成本与高可靠兼顾,在低轨卫星应用领域具有良好的应用前景.