基于ZYNQ的远程程序并行固化设计

闫成亮 曹凤才 岳凤英

摘 要: 北斗卫星导航信号接收机分布较为广泛,地处偏远,而且机箱内部芯片的程序又需要及时更新,这就造成了开发维护人员不能及时、方便地对芯片内的程序进行更新的问题。从环境的约束、人力成本、便利性等角度考虑,在这种情况下,以常规的方式对设备中的芯片进行软件更新是难以实现的。为了解决这个问题,提出基于ZYNQ的远程并行固化设计,在Linux运行环境下,利用远程计算机、FPGA和以太网通信组成一种远程并行固化系统,对FLASH中的程序进行固化更新。系统目前已在实际中得到应用,极大地提升了开发人员的效率,节省了大量的人力成本,具有很高的实际应用价值。

关键词: 远程程序; 并行固化设计; 程序更新; 控制模块设计; 软件设计; 系统测试

中图分类号: TN927?34; TP274 文献标识码: A 文章编号: 1004?373X(2020)10?0038?05

ZYNQ?based parallel curing design for remote program

YAN Chengliang, CAO Fengcai, YUE Fengying

(School of Electrical and Control Engineering, North University of China, Taiyuan 030051, China)

Abstract: The Beidou satellite navigation signal receiver is widely distributed and located in remote areas, and the program of chip in its crate needs to be updated timely, which makes it impossible for developers and maintainers to update the program inside the chip timely and conveniently. In consideration of the environment′s constraint, labor cost and convenience, it is difficult to achieve the software update of the chip in the device in the usual way. A remote program parallel curing design based on ZYNQ is proposed to solve above problems. A remote parallel curing system is composed of remote computer, FPGA and Ethernet communication in the Linux operating environment to cure and update the programs in FLASH. This system has been applied in practice, which has greatly improved the developers′ working efficiency and saved a lot of labor cost.

Keywords: remote program; parallel curing design; program update; control module design; software design; system test

0 引 言

隨着“一带一路”建设对北斗导航卫星沿线国家服务的需要,需要在全球范围内部署地面接收机。因国防技术发展的日新月异,北斗精度算法不断迭代,需要对已经完成全球部署的地面接收机实时进行功能更新,以满足我军技术的不断发展。已经部署在全球的地面接收机,如赤道、沙漠、南北极等,设备数量庞大,人工实地软件升级成本巨大。北斗地面接收机具有基于软件定义的无线通信协议而非通过硬连线实现。频带、空中接口协议和功能可通过软件远程下载和更新来升级,而不用更换硬件。为满足当前地面接收机发展需求,设计基于ZYNQ的远程程序并行固化系统。

ZYNQ?7000可扩展处理平台是赛灵思新一代FPGA(Artix?7与Kintex?7系列FPGA)所采用的最新系列产品。该芯片可编程逻辑可由用户配置,并通过“互连”一起,这样可以提供用户自定义的任意逻辑功能,从而扩展处理系统的性能及功能[1]。且该芯片采用带有NEON及双精度浮点引擎的双核ARM Cortex?A9 MPCore处理系统,该系统通过硬连线完成了包括L1,L2缓存、存储器控制器以及常用外设在内的全面集成,该处理系统不仅能在开机时启动,并运行各种独立于可编程逻辑的操作系统,而且还可根据需要配置可编程逻辑。ZYNQ?7000主要包含PS(Processing System)和PL(Programmable Logic)两部分,将ARM CPU和外设集成在一个芯片内,使得ZYNQ?7000系列具有处理器和FPGA的双重特性,适用软硬件协同设计。相对于ARM与FPGA结合的系统[2],其优势主要为以下几点:

1) 高集成度、高性能、低功耗。导航信号接收机分布在世界各地,其中不乏炎热、干旱地区,机箱内温度过高会影响系统运行的稳定性。

2) PS与PL间的高速数据传输协议。PS与PL间通过AXI总线协议进行数据传输。AXI总线协议具有低延迟、数据吞吐能力强的特性,最大带宽可达1 200 MB/s,极大地提高了PS与PL之间的数据传输速率。

3) PS端将接收到的配置文件按照数据协议直接写入PL端不同地址中,免去了FPGA在控制固化不同的板卡时检测板卡ID号的步骤,释放了更多的引脚资源。

1 并行固化总体方案

1.1 系统概述

采集主板上的ZYNQ?7000芯片作为系统的主控核心,其ARM端(Linux运行环境[3?4])通过TCP/IP协议与远程计算机进行通信[5],接收配置文件并解包,根据数据包中不同的板卡号将配置文件通过AXI?Lite总线接口写到主板的PL层的逻辑单元地址中。FPGA端在地址中读取该板卡的配置文件,对其解包后根据包格式中的FLASH号将配置文件固化到对应的FLASH中。同时将地址中对应信号处理板的配置文件取出,通过LVDS协议转发至每块信号处理板中,由信号处理板中的ZYNQ芯片对其进行读写FLASH操作。系统功能架构如图1所示。数据流向图如图2所示。

1.2 硬件电路构成

本系统由信号采集传输板卡、高速传输背板、信号处理板构成。其中采集传输主板由Xilinx的ZYNQ?7000系列芯片XC7Z015作为系统的控制核心。一片Xilinx公司的XC7K410T和一片XC7K325T Kintex?7系列芯片作为被配置FPGA,三片TI的TMS320C6655芯片作为被配置DSP,实现数字信号处理的辅助计算和通信功能,一片PHY芯片作为网口通信的协议通信芯片[6?7]。高速传输背板的功能是负责信号采集传输主板和信号处理板的板间高速互连和电源分配。

信号处理板由Xilinx的ZYNQ?7000系列芯片XC7Z015作为系统的控制核心。一片Xilinx公司的XC7K410T芯片作为被配置FPGA,两片TI公司的TMS320C6747芯片作为被配置DSP。

本设计使用恒忆公司设计生产的FLASH存储模块N25Q128芯片作为被固化存储设备,通过SPI串行总线接口配置芯片读/写,128 MB数据存储空间,最高支持108 MHz时钟频率。在每块板卡中都有一片接口模拟开关TS3L301DGG,用于切换写FLASH和从FLASH中加载程序。

1.3 ARM与FPGA数据传输

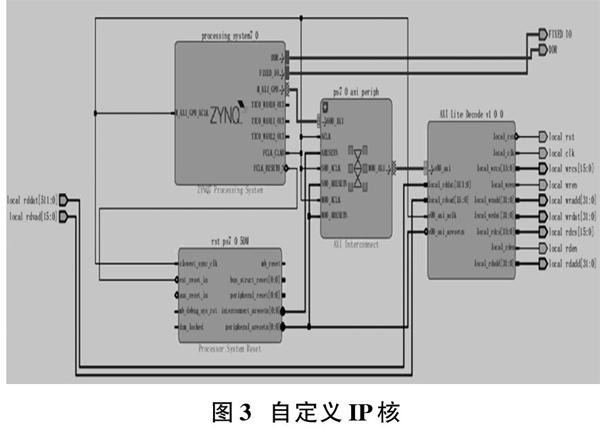

综合考虑系统的传输类型、传输速度需求以及功耗等各个因素,ARM与FPGA端的通信协议选择AXI4?Lite协议,其通常用于允许由某种形式的CPU或微控制器控制设计。使用VIVADO软件自定义ZYNQ的IP核,利用AXI4?Lite总线将ZYNQ核与编码模块连接到一起,并为IP核添加编码模块到FPGA端的地址和数据通道。自定义ARM的IP核如图3所示。

其中local_wrcs[15:0],local_rdcs[15:0]分别为写、读片选信号;local_wren,local_rden分别为写、读使能信号;local_wradd[31:0],local_wrdat[31:0]分别为写地址、写数据通道;local_rdadd[31:0],local_rddat[511:0]为读地址、读数据通道;local_rdvad[15:0]为读数据有效信号。

主板中ZYNQ芯片的ARM端作为master,FPGA端作为slave,通过AXI?Lite协议将配置文件发送到FPGA端。ARM调用写函数时自定义IP地址映射为0x4000_0000,为每一块板卡分配不同的地址空间。采用AXI4?Lite协议的突发式读写模式,master模块通过读地址通道发出寄存器的地址值,然后通过读数据通道读取slave模块对应done信号地址空间中的done信号值,若done信号为0,master模块则根据远程计算机发送的数据包协议,通过写地址通道和写数据通道将每块板卡的配置文件地址值和配置数据发送到slave模块,slave模块接收到数据后对配置数据进行解包,完成固化并返回固化完成的done信号,并将done信号写到对应的读地址空间中。master模块通过读地址通道发出寄存器地址值,读取slave端返回的done信号为1,停止发送对应板卡的配置文件。

1.4 FLASH控制模块设计

FPGA與FLASH之间的数据传输采用串行SPI接口[8?10]。时钟由FPGA 控制,在时钟移位脉冲下,数据按位传输,高位(MSB)在前,低位(LSB)在后;SPI接口有两根单向数据线,为全双工通信,目前应用中的数据速率可达几Mb/s的水平,能满足本设计传输速率的需要。在向FLASH中写配置文件时,由XC7Z015通过模拟开关TS3L301DGG选通XC7Z015到N25Q128芯片通路,并通过片选信号选中目标FLASH,此时由XC7Z015通过SPI接口向N25Q128中写入数据;当从FLASH中启动已经固化的程序时,通过模拟开关选通XC7K325T到N25Q128芯片通路,实现由上位机软件控制程序加载。主控芯片XC7Z015、被配置芯片XC7K325T、存储元件N25Q128之间的连接原理图如图4所示。

在对FLASH进行写操作时,必须严格按照FLASH的时序控制信号进行。在FLASH上电后,首先对FLASH进行初始化操作,将指定区域进行擦除操作,主板FPGA将ARM端写入FPGA地址的配置文件写入数据缓存队列(First Input First Output,FIFO)中,根据数据包协议,设置FIFO位宽为32,为防止FIFO溢出,设置FIFO的深度为8 192。当主板FPGA检测到对应主板配置文件的FIFO非空时,开始按照数据手册中的时序图通过SPI接口向FLASH中写入配置数据。

N25Q128的写时序图如图5所示,首先拉低片选信号CS,在时钟上升沿将指令写入FLASH,在指令之后是24位的首地址,地址发送完成后开始写入数据,页面编程一次最多能够输入256个字节,大于256个字节时,保留最后输入的数据。在输入不全为0的首地址后,从首地址开始写入数据,直到该页的最后,接着从下一页的起始地址进行写入,写入数据完成后拉高片选信号。

在对FLASH进行读操作时,N25Q128的读时序图如图6所示,首先拉低片选信号CS,在时钟上升沿向FLASH中写入读数据指令,读数据指令写完成后写入24位的首地址,在写入地址完成后,FLASH中的数据将按照輸入的首地址输出数据。首地址数据输出完成后地址自动增加,指向下一个地址,继续输出数据,输出数据完成后,拉高片选信号,读FLASH完成。

2 软件设计

远程计算机作为人机交互界面,承担着连接网络服务器,查询和修改IP地址,选择固化文件,复位、模拟上电,显示下载进度和状态信息等功能。开始固化时,远程计算机根据软件接口协议向下位机发送数据包,数据包中包含设备号、命令字、联网模式、参数类型、工作模式、通道号、参数包长度、CRC校验、参数包等内容,每次发送配置文件的有效数据的长度为20 KB,经实验测得每次发包的间隔为15 ms。每当下位机接收到一个完整的配置文件后,向远程计算机返回一个对应的完成指令,并且根据指令内容打印下载进度。固化完成后,通过远程计算机软件发送模拟上电指令,由XC7Z015芯片控制从FLASH中加载程序。

2.1 软件接口协议

数据帧格式定义如图7所示。

参数包具体数据:第一个4 B为数据的包号;第二个4 B为参数包的校验和;第三个4 B为参数包中有效数据长度,参数包大小以B为单位。

2.2 下载和启动程序

固化的过程,根据以下步骤进行:

1) 远程计算机发送命令字和配置文件,发送命令字数据包、文件长度、文件CRC校验到下位机,若下位机返回的数据长度、文件长度和CRC校验成功,则上位机将配置文件下载到下位机,每个数据包的大小为20 KB;若校验失败则尝试重新发送失败指令。

2) 下位机将接收到来自远程计算机发送的数据包进行解包,数据包的帧格式中包含配置文件对应的板卡号,并将配置数据进行存储。

3) 下位机接收配置数据完成后检测信号采集传输主板的FPGA端发送过来的done标志,若done标志为0,则根据不同的板卡号通过AXI接口向主板的PL层的逻辑单元地址中写入配置文件,每包数据大小为32 bit。

4) 采集传输主板侧的FPGA在地址中读取该板卡的配置文件,对其解包后根据包格式中的FLASH号将配置文件固化到对应的FLASH中。同时将地址中对应信号处理板的配置文件取出,通过LVDS协议并行转发至每块信号处理板中,由信号处理板中的XC7Z015芯片对其解包,根据包格式中的FLASH号将固化文件写入FLASH。

5) 当FPGA检测到固化数据长度和文件长度一致时,向下位机返回done标志为1,此时下位机停止发送配置文件,并向远程计算机返回固化完成信号,打印下载进度。

固化完成后,启动FLASH中的程序需要对板卡进行掉电重启或者由软件控制对被配置芯片进行模拟上电。考虑到设备投放地点环境较为复杂且距离较远,不方便研究人员的操作,所以采用软件控制,由远程计算机发送复位协议到下位机,下位机对数据包进行解包,通过XC7Z015芯片控制对其进行模拟上电,实现程序的在线加载,并且在加载的过程中不影响接收机正常工作。程序下载流程图如图8所示。

2.3 多机箱并行固化

由于导航信号处理机箱可能处于全球不同的地理位置,分布范围较大且数量较多,每次操控单个机箱会耗费科研人员大量的精力,致使其工作效率降低。因此,多机箱通过交换机同时并行固化的方案将会极大降低人力成本,提升工作效率。

ZYNQ的寄存器共有三个区:Bank0,Bank1,Bank2,其中Bank0是ZYNQ的本地寄存器空间0x4000_0000~0x4000_0FFF。该分区用于对SPI FLASH的固化操作,在Bank0未被使用的地址空间中写入每个机箱的初始IP地址。使用上位机连接机箱后,通过发送对应的修改IP指令,为每个机箱配置不同的IP地址。修改IP完成后,将多个机箱通过交换机连接到上位机后,即可同时为每个机箱发送配置文件,进行多机箱并行固化。

远程计算机界面如图9所示。

3 系统测试

将boot.bin文件通过JTAG固化到信号采集传输主板和信号处理板中,固化完成后掉电重启系统。将多个机箱通过交换机连接到远程计算机,为每台机箱配置不同的IP地址,并为待配置芯片选择对应的配置文件,然后开始固化。系统测试时,为FPGA选择的配置文件大小为28 MB,为DSP选择的配置文件大小为3 MB。在串行测试的情况下,每个FPGA固化所用时间大约为10 min 25 s,每个DSP固化所用时间大约为2 min 14 s,整个机箱固化总共需要176 min左右,如果对多个机箱进行固化时,耗时非常多,将极大降低开发人员的工作效率。而在并行测试的情况下,由于各个芯片同时开始固化,固化所用时间与最大固化文件的大小以及下载文件时间有关,所以实际固化多个机箱时只需要大约11 min,并且固化过程中板卡内原有的闪灯测试程序继续运行。固化完成后,通过远程计算机对各个板卡进行复位,然后对每个被固化的芯片进行模拟上电,远程计算机界面更新芯片状态显示已经固化,板卡上的闪灯已经按照新的程序闪烁。

系统测试时间对比如表1所示。

4 结 语

本文设计开发一种在Linux系统下,利用上位机软件、FPGA和以太网通信组成一种远程程序并行固化系统,对设备中的FLASH进行固化更新。与目前文献中出现的在线并行固化FLASH方式有较大的技术突破,主要体现在以下几点:

1) 在线并行固化。采用集ARM与FPGA结合的ZYNQ芯片,ARM与FPGA通过AXI总线协议,在使用时更灵活且数据传输速率更高。并且经由ARM芯片直接将每个板卡的配置文件写入到FPGA端不同的地址中,并且通过主板上的FPGA将不同地址中的配置文件通过LVDS总线协议分发到不同的板卡中,由每块板卡上的FPGA芯片去控制FLASH读写。而通过FPGA检测板卡号的方式首先需要在硬件上将控制板卡号的几个引脚拉高或拉低,占用了过多的引脚资源,在开发此芯片的其他功能时可能会产生引脚冲突。

2) 启动程序的时间可控。在FPGA的程序设计中,添加了复位模块和模拟上电模块。通过检测接收到的数据进行解析,识别到复位协议或模拟上电指令时,通过FPGA发出相应的操作。并且在固化的过程中,芯片中的原有程序正常运行,使得接收机在升级过程中始终能够正常工作。

3) 查询和修改IP功能。地面的导航信号接收机分布在全球各地,并且在一个基站内需要很多个机箱对数据进行接收处理。即使使用并行固化的方式,单独为每个接收机进行升级需要的人力资源和时间也是十分庞大的。而查询和修改IP的功能即可快速查询基站内的每个机箱配置的IP地址,并且为这些机箱配置不同的IP地址,然后将所有机箱通过交换机经由以太网连接至远程计算机,就能同时对接收机基站内的机箱进行固化升级,节省大量的时间。

本系统已实际应用于导航信号接收机的升级,目前系统运行稳定,多次对接收机机箱升级未出现异常情况。

参考文献

[1] 龚行梁,周强,赵天恩,等.CAN总线实现的ZYNQ?7000程序在线升级方法 [J].单片机与嵌入式系统应用,2018(11):63?66.

[2] 林天静,阮翔,刘春.基于FLASH控制器的FPGA在线加载功能设计[J].电子技术应用,2019,45(1):88?91.

[3] 夏凌云.嵌入式Linux通信软件开发中的设计模式[J].数字通信世界,2017(11):67?68.

[4] 陈文伟,于卓智,张叶峰.基于Linux系统的智慧安全型专网无线通信模块设计[J].电子设计工程,2019,27(5):121?126.

[5] 郑述堂.基于以太网传输的FPGA在线配置[C]//全国第五届信号和智能信息处理与应用学术会议专刊(第一册).银川:计算机工程与应用杂志社,2011:246?248.

[6] 汪灏,张学森.一种基于串行方式的FPGA远程加载电路[J].电子科学技术,2016,3(2):171?173.

[7] 张学森,李宏.一种远程配置FPGA的设计方法[J].中国科技信息,2010(14):95?96.

[8] 陈炳成.基于FPGA的SPI FLASH控制器的设计与实现[J].电子世界,2013(12):137.

[9] 张立为,钟慧敏.实现基于FPGA的SPI FLASH控制器设计[J].微计算机信息,2010,26(17):124?126.

[10] 李春雨,夏敏磊.基于CPLD的SPI FLASH程序在線加载方案[J].自动化与仪器仪表,2015(12):140?141.