基于BSC9132平台的双波形DSP软件系统设计∗

(广州海格通信集团股份有限公司 广州 510663)

1 引言

在信息技术飞速发展的今天,信息的高速传输在各行各业中已是必然需求,然而在某些特殊领域,如海上船船通信、海上与岸基通信、地空通信等,由于其自身特点及地理条件的限制,无法直接使用地面网络,且传统4G基站存在覆盖范围小的缺点,在海上大量铺设基站显然不太现实[1~4]。卫星通信系统虽能够满足大覆盖范围的需求,但其存在时延大、系统造价及运行成本较高的缺点[5~6],对此,文章提出了一种基于BSC9132平台DSP的宽窄带双波形并发的基站物理层设计方式,用于保证高速数据传输能力的同时达到扩大基站覆盖范围的目的,满足这些特殊领域的通信需求,作为地面通信与卫星通信的补充。

2 BSC9132平台介绍

BSC9132芯片是Freescale公司面向小基站解决方案研制的产品,主要用于小型移动通信基站、智能电网控制、军工领域等。BSC9132芯片由两个基于Power Architecture技术的e500内核、两个StarCore SC3850 DSP内核和若干MAPLE(Multi Accelerator Platform Engine,多加速器平台引擎)基带加速处理单元组成,能够满足高性能、低成本、集成解决方案的需求。

e500内核基于Power Architecture技术,主要用于高层协议开发,如部署接入层、传输层、网络层、主控以及声码话等功能,实现通信波形的整体调度。DSP由两个StarCore SC3850内核组成,定位于主流的DSP应用市场,如无线通信、电力通信等行业,主要用于通信波形的物理层功能实现。文章主要关注基带部分的设计与开发,因此仅对DSP部分性能参数进行介绍。

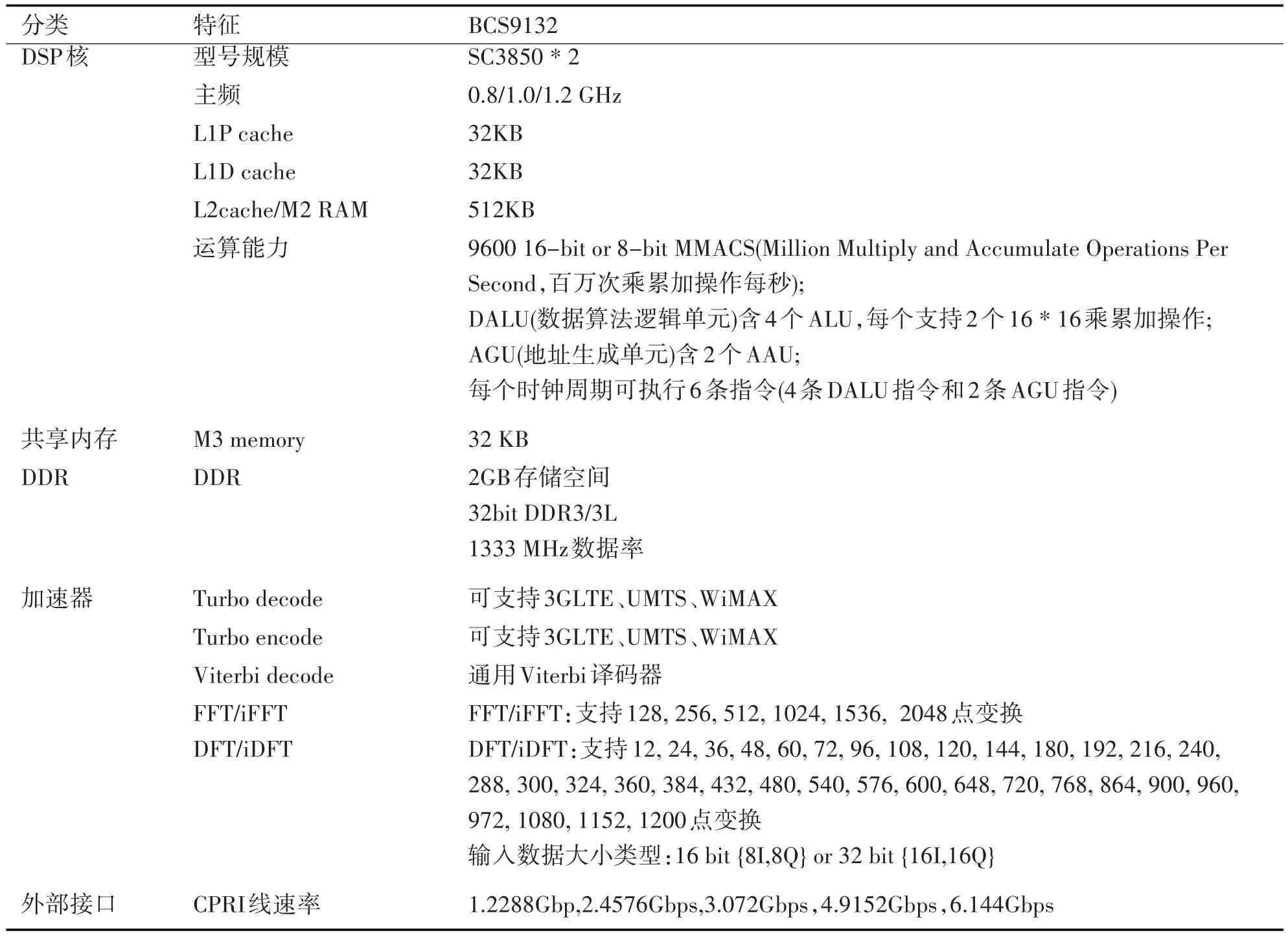

由表1可知,DSP包含两个核,每个核主频最高达1.2G;拥有L1、L2等较大的高速数据缓存空间;具备高数据逻辑运算能力及寻址能力;同时拥有多个支持常用标准协议的硬件加速器和外部CPRI(Common Public Radio Interface,通用公共无线电接口)接口,因此可以在DSP双核中完成物理层算法的实现、流程控制等功能。

表1 BSC9132芯片参数介绍[7~8]

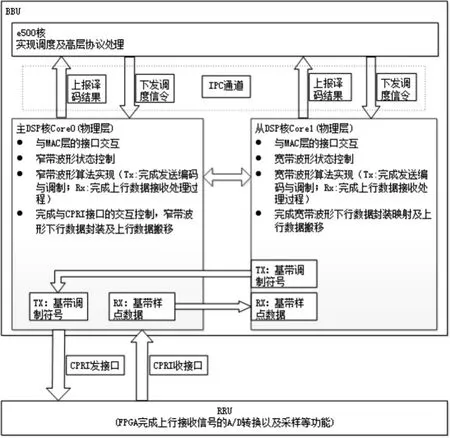

3 双波形软件系统设计

通信波形物理层的实现主要包含算法实现、时序控制、状态控制、消息交互、射频收发控制等。算法实现、时序控制、状态控制属于DSP内部实现的功能,除软件实现的功能以外,部分复杂的运算需要用到硬件加速器。消息交互、射频收发控制除涉及DSP内部核间交互外,还涉及处理器间的交互,如DSP核与e500核的交互、DSP与CPRI模块的交互。双波形DSP软件功能框架及流程控制如图1所示。

由图1可知,双波形软件中以DSP的双核分别处理宽窄带波形的物理层处理流程,外部接口主要涉及DSP双核与e500核的通信、DSP与CPRI模块的交互。为保证两核进行收数据搬移时CPRI模块已完成子帧数据的接收,物理层的子帧中断通过配置CPRI的数据传输结束中断提供。同时,由于宽带窄带波形具有相同的子帧长度,可共用相同的子帧中断来保证两核的同步运行,考虑这些因素,可由Core0单独对CPRI接口进行收发控制,在发送端,宽窄带波形数据同时映射到CPRI接口的不同位置中进行发送;在接收端,根据BBU(Base Band Unit,基带处理单元)与RRU(Remote Radio Unit,射频拉远单元)所拟定的映射接口对窄带波形数据进行提取搬移,并通过核间中断通知Core1进行窄带波形数据进行搬移。双波形并发基站需要在RRU射频端将宽带与窄带波形的频谱分别搬移到不同的频点,形成两个互不干扰的小区,文章主要关注BBU基带部分的软件设计,因此以下主要从DSP双核的物理层波形软件设计、L1/L2间交互及射频收发控制流程来描述BSC9132芯片上双波形并发的设计。

图1 双波形软件功能框架

3.1 物理层算法实现设计

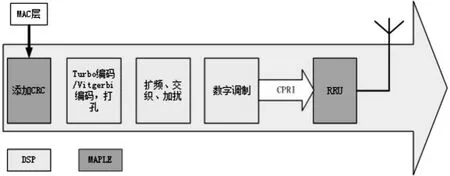

图2 基站物理层下行处理流程图

图3 基站物理层上行处理流程图

如图2、图3所示,DSP双核分别完成宽带、窄带波形的上下行数据处理过程,其中下行主要包括数据的编码调制,上行主要包括数据的检测、信道估计、均衡、解调和译码过程。上下行数据的处理除软件实现外,对于较为复杂耗时的运算,如FFT/IFFT、Turbo译码,Viterbi译码、CRC校验等可以使用芯片平台提供的MAPLE多加速器平台[9]来完成,从而达到提高软件运行效率的目的。

3.2 L1/L2间交互

物理层波形软件需要频繁与上层调度程序进行信令与数据的交互,这需要通过处理器间的通信接口来完成,BSC9132平台提供了一种IPC(Inter Process Communication,进程间通信)机制用于消息的传输,IPC机制既能高效灵活地实现L1-L2间的通信,同时也可用于L1-L1进程间通信,其所能提供的功能如下[10]:

1)MAC层与PHY层间L1/L2通信接口;

2)PHY层核间的L1/L1通信接口;

3)启动过程中L1-L2的框架同步;

4)StarCore与Powe Architecture间状态/指令的交互;

5)时钟同步;

6)跟踪调试。

由于IPC机制能够通过不同的通道实现与两个DSP核的并行通信而不相互影响,因此,可通过开辟不同的IPC通道来实现上层对两种带宽波形物理层的并行调度。

3.3 射频收发接口

分布式基站系统包含BBU与RRU两部分,其中BBU完成数字基带处理,RRU完成模拟射频处理功能,两者通过光纤连接,光纤传输采用CPRI通用标准接口技术,这是一种规范BBU内部射频设备控制器(REC)和RRU射频设备(RE)之间的接口标准协议。基于CPRI接口的分布式基站具有以下优点[11]:

1)BBU可集中放置,RRU放置于天线抱杆,既利于设备维护,也节省了机房空间;

2)应用大容量的宏基站可支持大量的光纤,实现了容量与覆盖转化;

3)容量大的宏基站可以为多个RRU所共享,这样在实现相同话务量的同时,节省了基带成本;

4)BBU与RRU通过光纤连接,避免了传统基站中馈线干扰带来的损耗;

5)适用于人口分布密度稀疏的农村到人口密集的城市等多种环境。

CPRI帧结构由基本帧、超帧和无线帧组成,如图4所示。

图4 CPRI帧结构图[12]

由图4可知CPRI的帧结构关系为1无线帧=150超帧=150*256基本帧。基本帧长:1 Tc=1/3.84 MHz=260.416667 ns,一个基本帧包含16个字:W=0…15,字长依赖于线比特率。

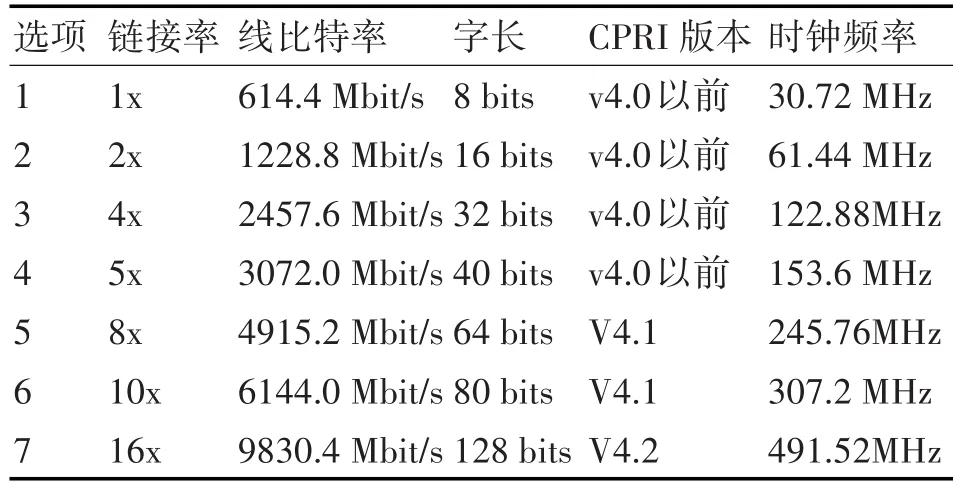

BSC9132芯片平台提供了CPRI接口控制模块,其支持多种线速率,对应的字长及时钟频率如表2所示。

表2 CPRI线速率[12]

线速率的选取需要根据波形算法设计中的最大数据传输速率来进行选择,既要满足吞吐量的需求,也要考虑传输效率。文章设计的波形系统中,BBU与RRU间传输的IQ数据位宽为16bits,则一对IQ数据占用空间为32bits{I 16bits,Q 16bits},因此,为数据映射简便,采用2457.6 Mbit/s线比特率,其字长为32bits,每个字刚好传输一对IQ数据。宽窄带两种波形采用相同子帧频率或者子帧频率具有倍数关系,这样可使波形控制更为简便,且可将宽窄带双波形的数据统一在主核(Core 0)中进行发送端的映射发送以及接收端的提取转发。因此,对于CPRI的收发数据存储空间,需要开辟在两核均能够访问的共享内存中。

4 结语

BSC9132芯片虽然定位于民用小型移动基站市场,包含了针对LTE、WiMAX、UMTS等多种标准的专用硬件加速器,在通用性上存在一定的限制,但由于其性能优异、功耗低等特点,同时除了专用标准硬件加速器外还提供了部分通用的硬件加速器,能够满足一般通信波形软件开发的需求,在其基础上针对特殊通信系统波形的需求,实现宽窄带波形并发,既能充分发挥其双核的作用,又具备实现小型化、低成本、低功耗的优势,能够满足舰载、空载基站的特殊需求。