基于FPGA的人体通信编码设计∗

刘乂毓 杨济宁

(1.内江师范学院计算机科学学院 内江 641110)(2.珠海博闻教育科技发展有限公司 珠海 519000)

1 引言

人体通信技术可以实现人体体表、体内的一系列穿戴式、植入式医疗传感器。由于人体通信的特殊性,不得不使用一种纠错能力强的编码方式来提高传输可靠性,RS(n,k)码最多能纠正t=(n-k)/2个错码,但编码的复杂程度使得我们需要使用一种高效的处理器来进行RS编码。

FPGA是现场可编程门阵列的简称,几乎能完成任何数字电路的功能,源于它内部是由许多不同的数据选择器(二选一、四选一等)、逻辑门,使用VHDL或Verilog HDL语言对这些基本逻辑器件进行组合编程,从而达到所需的功能。所以FPGA是制作RS编码器的理想器件。

2 RS编码原理

2.1 伽罗华域的构造

伽罗华域简称GF(q)域,域中共有q个符号且通常取q=2m,域中的每个元素都可以用α0,α1,α2,…αm-1的和来表示,α为本元多项式p(x)的根。在纠错编码运算过程中,所有的运算都是在伽罗华域中进行的。本元多项式p(x)是根据得到的余式为0来确定的。

2.2 RS码生成多项式

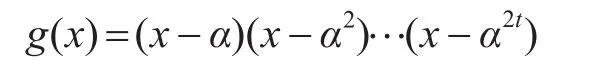

码长n=2m-1,监督元数目r=n-k=2t,能纠正t个错误。在RS(n,k)码中,存在唯一的n-k次多项式g(x),使得每一个码多项式c(x)都是g(x)的倍式。我们称g(x)为RS(n,k)码的生成多项式。一般情况下

2.3 RS码的校验多项式

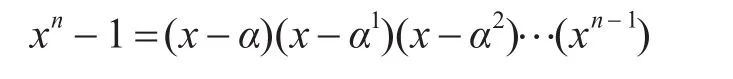

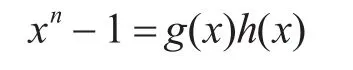

由于生成多项式g(x)是xn-1的因式,所以:

因为g(x)为n-k次多项式,所以h(x)为k次多项式:

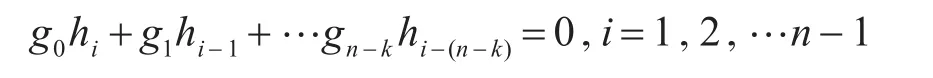

由上式可以看出xn-1,xn-2,…x的系数均为0,所以:

我们称h(x)为码的校验多项式。

3 FPGA实现方法

3.1 设计方案确定

使用Verilog HDL硬件描述语言实现RS编码难度较大,为了降低开发难度实验采用Altera公司推出的NIOS II软核来进行RS编码器的设计。使用Verilog HDL构造一个信息源为NIOS II软核提供数据进行编码测试。

3.2 SOPC的搭建

使用Quartus II开发环境下的SOPC Builder工具可以进行SOPC的搭建,使用NIOS II软件集成开发环境可以进行SOPC的软件开发工作以及软件调试、烧录等工作。其中jtag_uart是用于调试的接口,sdram是2块64M的内存,sysid是软件工程和硬件工程的匹配ID,data_in和data_out分别为数据I/O口。通过此步骤生成的就是图1的核心器件DE2-115。

3.3 编码软件实现

本次实验所用到的RS(255.239)编码,通过计算得到本元多项式为1+x2+x3+x4+x8,用二进制表示为101110001,将其存放到数组pp[mm+1]中表示为pp[mm+1]={1,0,1,1,1,0,0,0,1}。

在实际计算中,由于伽罗华域中的元素都是由二进制表示的,不能直观地看出域中每个元素的指数,因此,在生成GF(2m)域时,建立了一个用于存放域中每个元素对应的指数的数组index_of方便计算。

4 实验结果与讨论

4.1 实验

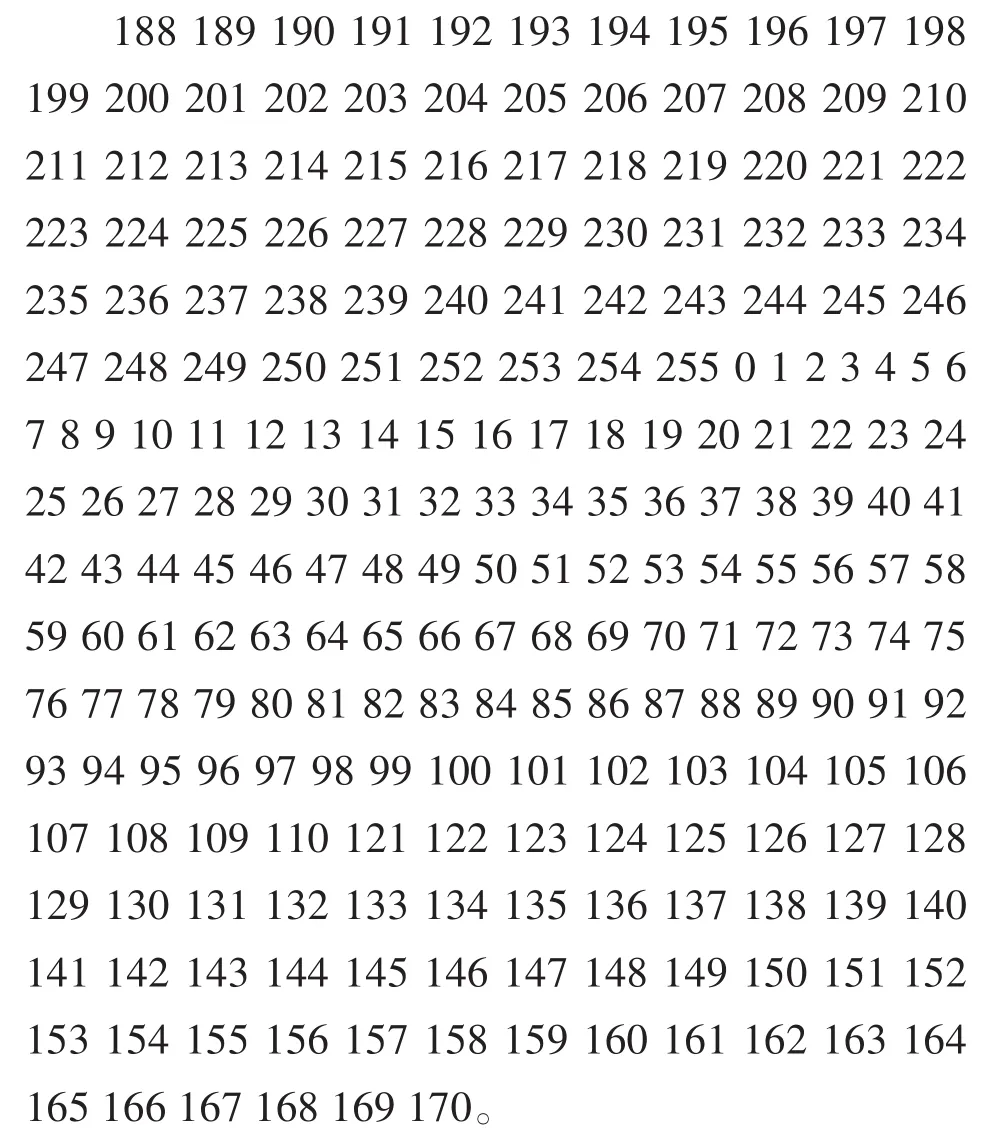

通过Quartus II将编译通过的硬件工程下载至FPGA开发板中,通过NIOS II软件集成发开环境将编译通过的软件工程下载至FPGA中进行测试。通过jtag调试接口返回的数据中得到,被编码数据:

产生的校验位为

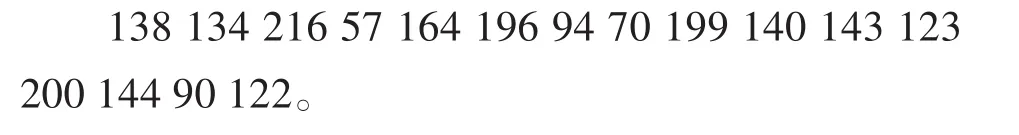

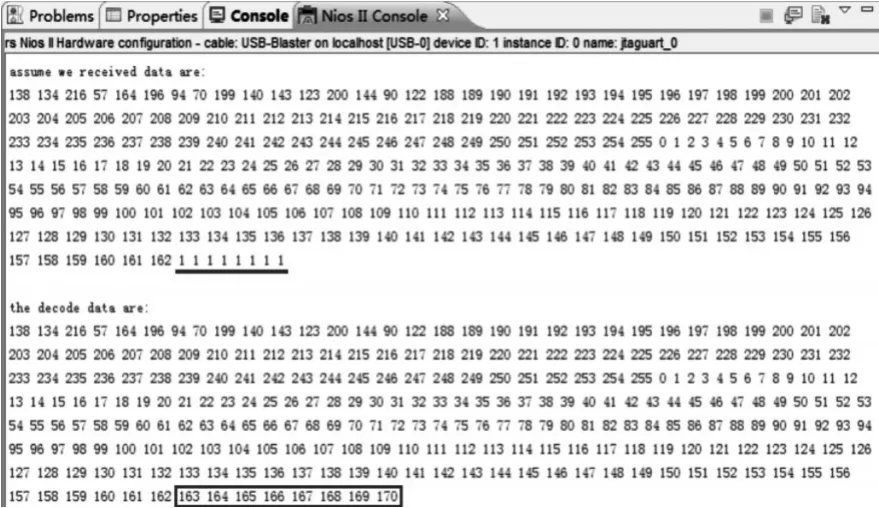

将校验位放在信息位前封装成长度为255位的码字,进行错值插入。RS(n,k)码的纠错能力t=(n-k)/2,因此本次设计采用的RS(255,239)的最大纠错能力为8,故错误数在8个以下理应能正确找出错误位置并纠正发生错误的码字,图1为插入3个错误值的解码情况。

图1 3个错误数的解码情况

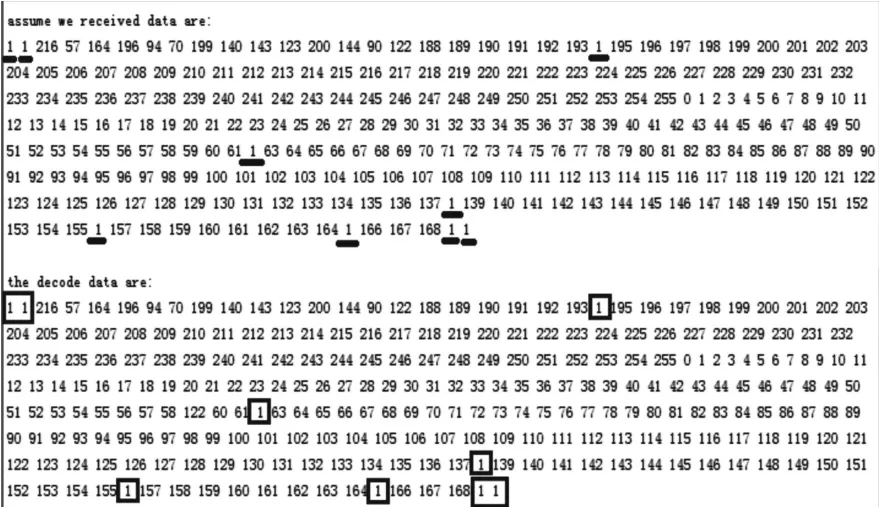

图2为8个错误数的解码情况。

图2 8个错误数的解码情况

图3为产生9个错误数的解码情况。

图3 9个错误数的解码情况

4.2 实验结果分析

在RS(n,k)码是一种优良的纠错码,从图1可以得到,通过人为错误值插入,将编码后的数据第1位和第254位和255位修改为1。使用解码函数进行解码,解码过程纠正了第1位和第254位和255位的错误。从图2可以得到,连续发生8个错误也能将其发生错误的码字纠正过来。从图3可以得到,当传输过程中,产生的错误数大于RS(n,k)码的最大纠错能力后,不能将其错码纠正。

5 结语

SOPC高度的灵活性使得用SOPC技术结合IP核可以在某些特殊情况下一定程度上简化FPGA的开发流程,但其缺点是速度相对较慢。使用NIOS II软核做成的RS编码器还有许多不足的地方,还需要添加一些外围电路来稳定整个系统。RS编码是一种纠错能力很强,应用范围很广的纠错编码,尤其是在产生突发错误的信道中得到广泛的使用。

——编码器