基于Avalon总线的双口RAM与PCI总线数据交换的设计

魏 珊,魏 丰,陈梦桐

(华中科技大学 人工智能与自动化学院,武汉 430074)

0 引言

实现数据的暂存和双向传输,一般会采用FIFO和双口RAM这两种模式作为数据交换和存储的共享存储器。FIFO(first input first output)是数据从一端先写入然后在另一端优先读出来的存储器,一般用于异步时钟的数据交换系统中,充当两个不同时钟系统间的数据暂存器。所以称它为异步FIFO。双口RAM是具有两个端口的静态存储器,两个端口分别有其自己的数据线,地址线和控制线,由于端口两边有独立的总线,所以两个CPU可以对双口RAM同时进行读写操作,或者一个CPU在一端对其读操作,另一个CPU在另一端对其写操作。双口RAM的此特性实现了CPU之间数据的高效灵活交换。实验室的同步数据采集卡项目要求上位机可以根据需要对存储器任意单元内的数据进行读写,这就对共享存储器的读写方式有了一定的要求。FIFO存储器的读写严格的按照先进先出的规则,满足不了该项目的需求。双口RAM存储器的读写是灵活的,可以根据需求清楚地了解到双口RAM各个存储单元的信息,正好符合此项目的要求,因此本文选择双口RAM作为该项目的共享存储器[1]。

双口RAM存储器的实现既可以采用现成的双口RAM芯片,也可以通过Verilog HDL语言在FPGA内设计功能模块,然后在Nios II开发环境中封装成IP核来构造完成。现成的双口RAM芯片有Integrated Device Technology公司研发的IDT7130,IDT7130是一种1K*8高速的双端口的静态RAM[2],RAM两个端口的数据,地址和控制线是独立且对称的,两个CPU通过IDT7130内部的硬件地址仲裁信号BUSY 信号可以从任一端口对IDT7130进行完全异步的操作。此外IDT7130具有自动进入低功耗状态的特点,因此IDT7130在民用和军用上都很受欢迎。为了充分利用FPGA上现有的存储器资源,同时简化该项目硬件设计的复杂程度,本文采用通过对FPGA内的存储器进行配置并将其封装成IP核的形式来构造双口RAM。对其进行功能测试后结果表明本文设计的双口RAM实现了数字量和时标信息在FPGA与PCI总线接口之间高速有效且不丢包的实时传输。

1 Avalon总线和PCI总线接口芯片

Altera公司为了提高主从设备之间数据交换效率和速率,开发了一种新的总线结构Avalon总线。Avalon总线是Nios II处理器内部模块和外围设备数据交换的一座桥梁,模块之间通过Avalon总线连接形成片上可编程系统SOPC。Avalon总线的特点是采用了分离的地址、数据和控制总线,没有信号选择电路,大大简化了数据传输的复杂性,提高了传输效率;Avalon总线上的信号是高低电平,这样简单的信号可以在总线上高效地传输[3]。PCI总线接口芯片CH365主要将高速复杂的PCI总线转换成八位并行的数据线和地址线[4],上位机驱动程序通过总线接口芯片CH365对双口RAM共享存储器进行读写。实现数据在FPGA和上位机之间双向实时地传输。图1是Avalon总线和PCI总线接口芯片CH365通过共享存储器双口RAM进行数交换示意图。

图1 PCI总线接口芯片CH365通过双口RAM与Avalon总线通信

说明:PCI总线接口芯片CH365将复杂的PCI总线转换为八位数据线和地址线,图1可以看出接口芯片CH365对双口RAM的读写操作的总线是公用的,Avalon总线的读写数据线则是分开的,为了充分使用FPGA现有的片上存储器资源,本文在设计单时钟真双端口RAM的时候需要对CH365的数据线进行一定的配置,使其符合FPGA自带的存储器的使用规则。这一特点也是设计双口RAM的初衷之一和难点之一。由图1可知整个系统只有一个时钟clk,该时钟来自于FPGA的系统时钟,其作用是让两个CPU对双口RAM有效有序的读写操作。rd_mem_by_ch365和Wr_mem_by_ch365分别是CH365对双口RAM的读写使能信号。Write_enable是Avalon总线的对双口RAM的写使能信号。

2 FPGA中双口RAM的分类

图2将FPGA内的存储器做了一个清晰的分类。

图2 FPGA内的存储器

Altera公司开发的Cyclone IV EP4CE6E22C8N这款FPGA芯片具有嵌入式存储器结构,这一特点满足了该型号的FPGA对片上存储器的需求。嵌入式存储器的结构由一系列M9K存储器模块构成,对这些M9K存储器模块进行一定的配置,即可以实现各种各样的存储器功能,例如RAM、移位寄存器、ROM以及FIFO缓冲器。M9K存储器具有很多特性,例如存储器的每一个端口都具有独立的读使能和写使能信号,在Packed模式下,M9K存储器模块可被分成两个4.5K单端口RAM,同时具有可变端口配置模式等。存储器根据读写端口的个数可以被配置成简单双端口和真双端口模式。

简单双端口模式: 这种模式下的存储器一边只有一个读端口和另一边只有一个写端口,即这种模式支持不同位置的同时读写操作。

简单双端口RAM在读的这一端口只有与读相关的所有信号,例如读地址信号wraddress[],读使能信号wren,读时钟和读使能时钟。同理,在写的这一端口只有与写相关的所有信号。在此模式下,M9K存储器模块支持独立读写使能信号rden和wren。在没有进行读写操作时,一般讲rden信号保持在低电平(无效状态),从而降低功耗。相同地址上的Read-during-write操作能够在相应的位置上输出“New Data”数据,或者输出“Old Data”数据。

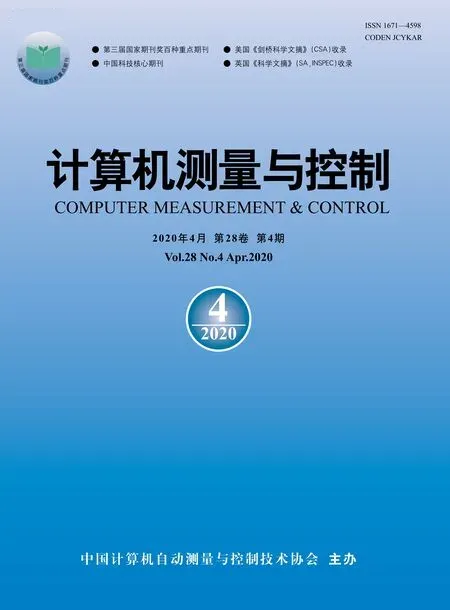

图3 简单双端口RAM

真双端口模式:这种模式下的存储器具有两个独立的写端口和两个独立的读端口,这种模式支持双端口操作的任何组合,例如在两个不同时钟频率上的两个读操作,两个写操作,或者一个端口的读操作和另一个端口的写操作[5]。

图4 真双端口RAM

相比于简单双端口模式,真双端口模式下的RAM两端口既有读信号也有写信号,因此在此模式下的RAM可以对存储器某一端口任意独立地进行读写操作,而不是固定哪个端口只能读或者只能写操作。对于存储器的操作更加灵活。当存储器两个端口对存储器同一位置进行读写操作时,可能会出现冲突,此时需要外部的冲裁电路来解决。

除此之外根据双端口RAM的时钟个数又可以细分为单时钟简单双端口RAM、双时钟简单双端口RAM、单时钟真双端口RAM和双时钟真双口RAM。时钟是一个系统的脉搏,在所有系统中扮演着非常重要的角色,系统有条不紊的运行离不开时钟。存储器也一样,对存储器进行正确地读写操作离不开时标信号。观察IDT7130双端口静态RAM芯片的读写时序图,我们发现IDT7130芯片没有时钟信号,仔细阅读它的内部功能电路你会发现有I/O控制单元,地址译码器,存储器阵列以及仲裁逻辑控制的电路,在这些电路的基础上IDT7130采用中断方式交换信令的方法以及有效操作BUSY信号获得时标信号,从而对其进行高效有序的读写。FPGA内部的存储器是直接采用时钟信号的形式来完成对存储器正确有序的读写操作,时钟信号控制着操作的先后次序,达到了数据交换的准确性和高效性。

根据图1,该项目中的双端口共享存储器RAM只有一个时钟。基于该项目的需求,本文主要设计的是只有一个时钟的真双端口RAM。

3 双口RAM在FPGA中的实现

本文采用自上而下的设计思想设计了共享存储器双口RAM[6]。选择用Altera公司研发的的Cyclone IV E系列EP4CE6E22C8N FPGA器件,该系列器件具有6K的逻辑单元、270 Kbits的嵌入式存储器、2个通用的PLL,最大用户I/O可以达到179个、其中Nios II的最高频率可以达到170 MHz。该器件具有低成本高性价比的特性,被广泛使用。本文在这款FPGA器件内实现了256字节存储容量的单时钟真双端口RAM共享存储器。主要通过Verilog HDL语言来进行设计。首先我们选择的硬件开发环境是QuartusII第11.0(64位)版本,该软件主要通过硬件描述语言Verilog HDL实现FPGA的资源的分配利用[7],Verilog HDL编写.V文件,然后对其编译、综合,最后下载到FPGA内即可实现对FPGA资源的使用。该开发环境还可以对所设计的模型的时序进行分析,从而检测该模型是否符合设计需求[8]。选择NiosII的第11.0版本为软件开发环境。SOPC的配置文件(后缀名.sopcinfo)是连接软件和硬件资源的重要文件[9]。在开发环境QuartusII内部其实有很多FPGA内部资源的例程代码供参考,本文开发的单时钟真双端口RAM就是参考QuartusII内部的RAM例程来完成的。

本文采用模块化的程序设计,设计了两个模块,即两个.V文件。一个是QuartusII内部的单时钟真双端口RAM文件,另一个是根据项目中共享存储器两端口总线的特点设计了一个将Avalon总线和CH365接口总线连接起来的文件。对于第一个文件首先将QuartusII内部的单时钟真双端口RAM例程调出来,然后对其修改,具体步骤是:在QuartusII开发环境中新建一个Verilog HDL File文件,回到主界面点击菜单栏中的Edit下拉菜单中有一项是Insert Template,出现的对话框有语言例程的分类,包括AHDL语言、VHDL语言和Verilog HDL语言等,本文选择Verilog HDL,里面包括Full Design、Logic、Synthesis Attributes等,本文选择Full Design,内部包括RAMs and ROMs,选中会发现有很多例程,根据本项目需求选择True Dual Port RAM(single clock),将其例程代码导入到最初建立的Verilog HDL File文件中,对其做了一点修改,这样单时钟真双端口RAM的内部基本结构获得了,但是该基本结构缺少端口信号的具体设计。联系实际情况本文设计了第二个Verilog HDL File文件。

图5 QuartusⅡ内部的单时钟真双端口RAM例程

在对第二个.V文件设计的时候,考虑到FPGA中的SOPC系统各个模块之间数据交换的总线标准是Avalon总线,本文设计的单时钟真双端口RAM最终要嵌入进SOPC系统中,而CH365接口总线的读写数据线和Avalon总线的读写数据线存在差异,CH365接口总线的读写操作公用一条数据总线,Avalon总线具有单独的读数据线和单独的些数据线。考虑到这一点,我们来设计第二个.V文件[10],主要解决第一个.V文件没有解决的问题以及配置CH365接口的读写数据总线。首先配置第一个.V文件定义的双口RAM的各个端口信号,主要包括系统时钟信号clk,两端地址总线,数据总线的定义和读写使能信号的定义。然后合并CH365接口总线这边的数据线,实现的方法是程序中自定义了一个CH365数据总线输入输出控制信号dir_ch365,在系统时钟有效地前提下,当365的写双口RAM的写使能信号有效的时候控制信号dir_ch365置1,此时CH365的数据总线作为输出,向双口RAM写数据。反之,在系统时钟有效的前提下,当365的读双口RAM的读使能信号有效的时候控制信号dir_ch365置0,此时数据CH365的数据总线作为输入,读取双口RAM中的数据。

图6 CH365接口数据总线处理部分代码

4 将双口RAM封装成IP核

将自定基于Avalon总线的单时钟真双端口RAM模块封装成IP核嵌入到SOPC系统中需要在工具SOPC Builder中完成。首先在菜单栏Project中新建自定义组件点击New component,出现图7的对话框。首先是组件编辑(component editor)的简介。第二步硬件描述语言文件(HDL Files)的加载,之前写好的两个.V文件就是要从这里加载进去,加载的同时系统会自动编译。第三步.V文件中自定义的端口信号与双口RAM内部信号之间一一对应的配置了,主要包括信号类型、信号宽度以及信号的方向。第四步信号线参数以及时序的配置。第五步数据总线和地址总线位宽的配置,数据总线和地址总线本在设计的都是8位。最后给配置完的IP核和命名,以及它属于的IP核组,方便使用者找到并使用。点击Finish后,系统首先进行编译最后生成自定义的IP核组件。这个IP核可以供使用者使用,同时还可以根据设计者的需求对其进行修改,方便灵活。

图7 单时钟真双端口RAM

前文说过,双口RAM作为数据交换的共享存储器也有其不足之处。当两端的系统同时对双口RAM的同一单元读数据或者写数据的时候,会出现错读的现象,读到的数据不是使用者所需要的数据。针对这一现象,本文采用奇偶交换页的思想来访问双口RAM。双口RAM的每16个字节单元为一页,分为奇数页和偶数页,偶数页作为双口RAM的起始页[1]。当某一系统往奇数页写完或者读完数据后,将奇数页的标志位置1。当系统操作完偶数页时,偶数页的标志位置0。系统再次访问这些单元的时候先访问奇偶标志位,判断完成以后再访问存储单元里面的数据。这样的访问存储单元的思想有效地避免了数据错读的显小,提高了双口RAM双向通信的效率。

5 双口RAM的功能测试

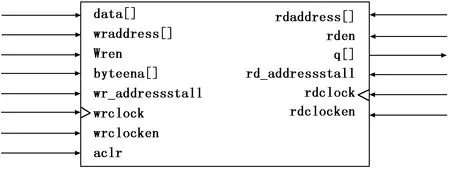

为了验证本文设计的单时钟真双端口RAM的正确与否,本文首先在硬件开发环境QuartusII 11.0中设计设计硬件原理图构成SOPC硬件系统,然后在软件开发环境NiosII 11.0中编写测试双口RAM的代码。方法是向已经嵌入到SOPC中的双口RAM写入简单的数据,然后读出双口RAM中的数据,最终在显示终端打印出来。其测试结果如图8所示。为了验证本文设计的双口RAM是否可以通过PCI总线和上位机进行数据交换,本文还在LINUX环境下建立PCI字符设备,对所建立的PCI字符设备读写操作,测试双口RAM的功能,其测试结果如图9所示。最后在NiosII中编写软件将项目中设计的同步时钟采集卡通过CPS接收机采集到的时标信息传送到台式机,测试双口RAM能否在FPGA和上位机之间实现数据正确高效的双向传输。其结果如图9所示。

图8 双口RAM与NiosII之间的通信测试结果

说明:图8的结果显示了数据可以正确地在双口RAM和NiosII之前传输,说明本文所设计的单时钟真双端口RAM是可用的。图9的结果表明本文所设计的单时钟真双端口RAM 可以通过PCI总线和上位机有效通信。图10是GPS接收机接收到的时标信息通过NiosII处理器处理之后的信息,NiosII处理器将其存放在本文所设计的双口RAM中,上位机在LINUX操作系统中将双口RAM中的数据读取出来,然后在上位机上显示的结果,此结果证明了FPGA和计算机的通信是可行的,本文所设计的单时钟真双端口RAM是成功的。

图9 双口RAM与上位机之间的通信测试结果

图10 NiosII通过双口RAM与上位机之间通信测试结果

6 结论

共享存储器作为数据交换的桥梁,在数据通信系统中起着至关重要的作用,在图像处理等数据量比较大的领域,实现数据高效实时地传输是一个难点,也是一个重点,为了缓解数据传输的压力[7],数据共享存储器获得了越来越多的青睐。本文以GPS同步数据采集卡项目为应用实例,充分利用现场可编程门阵列FPGA的片上存储器的资源,成功地开发了基于Avalon总线的单时钟真双端口模式的RAM共享存储器,本文所设计的双口RAM存储容量有256字节,由于PCI总线接口芯片的数据和地址都是固定的8位,本文设计的双口RAM固定了数据线和地址线为8位。为了避免数据在高速传输的时候出现丢包现象,本文提出了奇偶页交换数据的思想,由于要传输的报文信息的长度是12字节,本文以16字节为一页,分为奇偶页,数据轮流交换。实现了12字节报文信息在FPGA和上位机之间高效且不丢包的实时传输。