基于FPGA的软件定义协议无关解析器

苗力心,刘勤让,汪欣

基于FPGA的软件定义协议无关解析器

苗力心,刘勤让,汪欣

(国家数字交换系统工程技术研究中心,河南 郑州 450002)

随着信息技术的繁荣发展,各种功能的异构网络层出不穷,异构融合网络成为下一代网络发展的必然趋势。实现异构网络之间的通信,网络转发设备必不可少。传统的转发设备仅支持固定的协议配置,缺乏可扩展性,无法支持新的网络协议。针对这种情况,提出了一种基于FPGA的软件定义协议无关解析器,通过软件定义解析流程,给予解析器灵活可编程的特性,无须对硬件设备进行更改即可完成对多种协议数据包的解析并提取出数据包转发所需的关键信息。通过高性能FPGA平台对解析器进行了实现,并进行了硬件资源开销和性能的评估。实验结果表明,可以完成多种异构网络协议的快速解析,得到完整的解析数据。

FPGA;软件定义;解析器;协议无关

1 引言

随着现代网络和信息技术的飞速发展,信息的交换与传输频繁地发生在各式各样的网络设备之间,一切皆可互联成为必然趋势。各种功能的异构网络系统层出不穷,如支持嵌入式系统的RapidIO网络[1]、应用于航空电子环境中的FC-AE网络[2]、传统的以太网网络等。人们对互联的需求促使了异构融合网络的诞生,支持不同协议类型的网络设备共同应用在同一个网络系统中,使信息的互联交换变得更为通畅。与此同时,多样的网络系统也带来了更加丰富的新型网络协议,异构网络之间的融合要求网络转发设备必须同时支持各种不同的新型协议,这为网络转发设备的可编程性和可扩展性带来了严峻的挑战。为了更好地实现信息互联以及异构协议网络设备之间数据的流畅通信,网络转发设备的升级更新成为急需解决的问题。

在通信网络系统中,不同设备之间的通信都是依靠数据包来完成的,数据包由包头和payload负载内容组成,识别和提取包头中相关字段的过程称为解析[3]。在高速的网络转发设备中,对数据包的包头信息的解析、识别和提取的效率影响着整个系统的吞吐率,是整个系统性能的关键所在。由于包头格式的复杂性,包解析成为限制高速网络性能和速率的一个关键瓶颈。数据包的长度和包头格式因网络和数据包的不同而不同,因此需要提取的标识字段与关键字段也不相同,而随着夹层协议MPLS、基于EoMPLS的多层MPLS和802.1Q等的加入,包头格式变得更为复杂,很难解析。而传统的报文解析器仅支持固定的协议类型,一般使用ASIC(application specific integrated circuits)实现,存在缺乏可扩展性、灵活性差的缺点,无法灵活处理新的复杂协议类型。在异构融合网络中,如果使用ASIC设备,那么在添加新的网络设备,即添加新的协议类型时,需要对转发设备进行重新设计,这无疑将带来极大的设备开销,因此对具备支持多种网络协议类型解析的具有可编程性、可扩展性的解析器的探索势在必行。

软件定义网络(SDN,software defined network)[4]实现了网络控制平面与转发平面的分离,打破了原先一体化的硬件设施,将基础硬件虚拟化并提供标准化的基本功能,然后通过管控软件,控制其基本功能,提供更加开放、灵活、智能的管控服务。本文将软件定义的概念应用于新型协议无关解析器的设计中,同时在数据包的包头解析的流程中,本文提出了一种基于协议解析描述符生成的解析流程,描述符可以依据数据包协议类型生成解析所需要的控制流信息从而达到对任意协议的支持,即协议无关。不同的协议有不同的描述符结构,这些结构信息以流表的形式存储在存储单元中。用户可以通过对控制寄存器进行简单配置来选择当前解析器支持的协议类型,即当用户选择某个协议时,系统将相对应的描述符结构信息以下流表的方式配置到解析器的RAM中,此时解析器便可以解析这一协议类型的数据包。通过这种方式,可以实现控制平面与转发平面的分离,用户不需要关心底层硬件设备的情况,只添加解析器支持的协议类型即可。

2 相关工作

包头信息的解析对于网络转发设备来说是必不可少的一个环节。通过对包头信息的解析,可以得知数据包的传输路径,并且可以有效对数据包进行分类处理,不同类型的包具有不同的功能以及不同的响应方式。数据包的包头解析实现途径主要分为软件实现方式和硬件实现方式。使用软件实现数据包的解析具有灵活性高、周期短的特点,用户可以直接修改软件代码来实现新协议的扩展,但软件实现由于处理速度相对较低,不适用于高速网络。硬件实现虽然具有高速稳定的优点,但由于硬件本身固化,导致硬件实现可重构性差,灵活性较低[5]。软硬件协同的包解析将是兼具两者之长的一种完美的解析方式。

SDN实现了控制平面与数据平面的解耦分离,抽象了数据平面网络资源,是实现高速动态可编程网络的理想架构。OpenFlow协议作为最普遍的分离控制平面和数据平面的南向接口,依靠增加匹配域实现对新协议的支持,但随着新协议越来越多,匹配域变得难以扩展,灵活性受到极大的限制。Yazdinejad等[6]提出了一种OpenFlow V1.3交换机架构,该架构除了提高匹配表的速度和增加处理管道之外,解析器还支持40个包头解析并且可以通过重写进行扩展。但这并不能完美解决OpenFlow的局限性,依旧无法支持更多的协议类型。Liu[7]在FPGA上实现了SDN开关,避免了NetFPGA的延迟,但解析器是固定的,不具备支持新协议类型的可配置性和灵活性,需要重新写解析器的VHDL程序。

现场可编程门阵列(FPGA,field programmable gate array)由于具有低功耗、高性能、可重构性,被广泛应用于网络设备的设计,是解决硬件解析架构灵活性差的良好平台。王孝龙等[8]提出了一种支持异构协议解析的可配置解析器设计,通过配置用户定义模块实时更新解析树以及TCAM和RAM存储状态转移表实现对新型网络协议的支持,并提出了一种基于节点压缩的优化算法。杨惠等[9]提出了一种基于FPGA的并行多发可编程解析器,将数据包解析过程抽象化3个协议无关的中间操作(识别、匹配、提取),并针对这些操作分别进行了一系列的优化加速,更关注解析器的性能优化问题,无法达到协议无关。Bitar等[10]提出了一种基于FPGA的数据包解析器结构,通过在FPGA上嵌入NoC(network-on-chip)达到400 Gbit/s至800 Gbit/s的吞吐率。此设计通过一个处理模块和嵌入NoC的FPGA的多重互连来识别协议类型。但将NoC嵌入FPGA在当前是很复杂和困难的,暂时不具备实用性。

可编程协议无关数据包处理语言[11](P4,programming protocol-independent packet processors)是Nick教授等提出的一种用于数据平面的高级编程语言,具有协议无关、目标无关以及可重构特性。Silva等[12]利用P4描述在SDN之中开发了一种基于FPGA的开源数据包解析器架构,他们直接从包处理的描述中生成高速低延迟的包解析器。这种体系结构采用流水线结构并使用C++框架进行设计,但增加了逻辑资源的消耗。Benácek等[13]利用P4的思想对解析器生成器进行设计,将P4的解析图转换为适合FPGA实现的可合成的VHDL代码,可以自动生成解析速率为100 Gbit/s的可编程解析器。但相比于手工编写的VHDL代码,这个自动生成的解析器延迟和资源开销更大。

本文提出了一种基于FPGA的软件定义协议无关解析器设计,通过在解析过程中使用生成协议解析描述符的方式,用户只需要对解析器支持的协议类型进行选择,解析器即可完成对不同协议的数据包解析。通过对描述符格式进行设计,解析器可以解析各种依靠数据包进行通信的传输协议,如TCP/IP、SRIO协议、FC光纤通信协议、以太网802.1协议、HTTP协议等。数据包主要由“目的IP地址/目的MAC”“源IP地址/源MAC”“净载负荷”等部分构成,包括包头和包体,包头根据协议不同而长度不同,包含的具体信息也不尽相同。在包头信息解析的过程中,解析器会根据当前协议类型生成初始描述符(MF)。在包头信息解析状态的跳转过程中,描述符会进行不断的修改与添加,描述符中的控制流信息可以将包头中的关键信息key值提取到描述符末端的关键字段中并在后续的匹配以及操作模块使用这些信息,从而实现协议无关的解析操作。

3 解析器结构设计

数据包解析的过程就是对包头协议的识别以及关键数据信息的提取,基于此,本文提出基于FPGA的软件定义协议无关解析器(SDPIP,software defined protocol independent parser based on FPGA),设计目标是实现用户软件定义以及达到协议无关。软件定义可以将解析器的控制层集中,方便用户对设备进行编程以及更改,提高解析器的灵活性。在异构融合网络之中,协议无关的解析器为转发设备提供了强大的适用性,无须考虑对接设备支持的协议类型即可对数据包进行快速解析转发,减少了网络系统更新时转发设备的开销,便于设备架构部署,符合异构融合网络的发展。

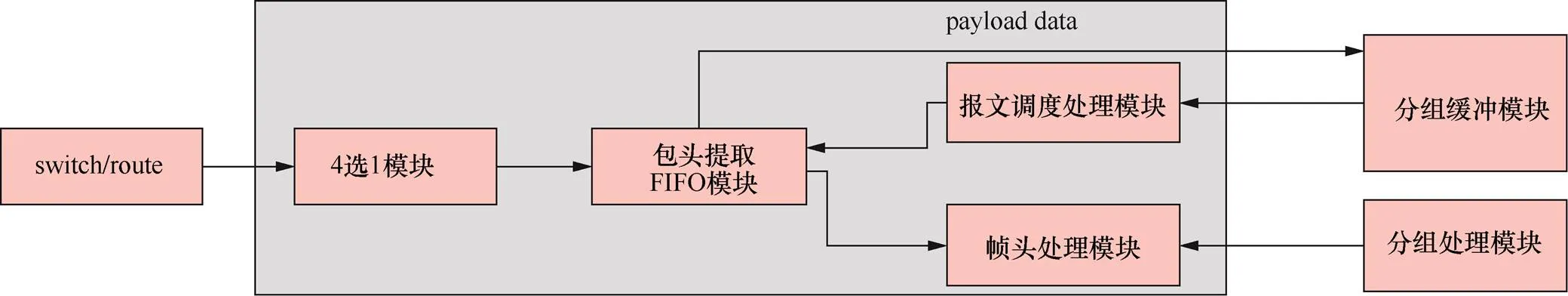

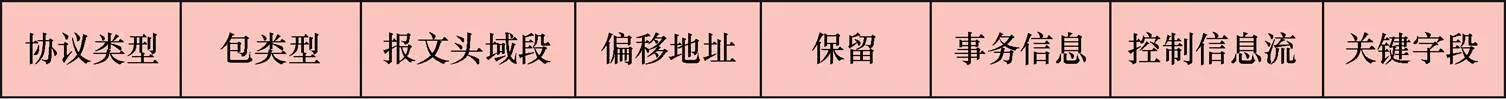

解析器的解析流程如图1所示,SDPIP解析器共有4个接收端口,由4选1模块、包头提取FIFO模块、报文调度处理模块、帧头处理模块、包缓存模块以及包处理模块组成。通过光纤接口接收到的来自交换机或者路由器的数据包首先经过4选1模块进入包头提取FIFO模块,在此模块完成包头信息与payload负载内容的分离,同时payload数据被发送至包缓存模块保存。包头提取FIFO模块包含状态跟踪逻辑和缓存区,首先对包头信息进行协议类型信息的提取匹配,根据匹配结果生成对应协议的初始MF。初始MF由用户根据各个协议类型的解析过程软件定义,如图2所示。其中包含数据包的协议类型、包类型、报文头域段、payload数据在缓存区的偏移地址、保留字段、事务信息、各类控制流信息、关键字段。

图1 解析器流程

Figure 1 Parser flow

图2 描述符结构简图

Figure 2 MF structure diagram

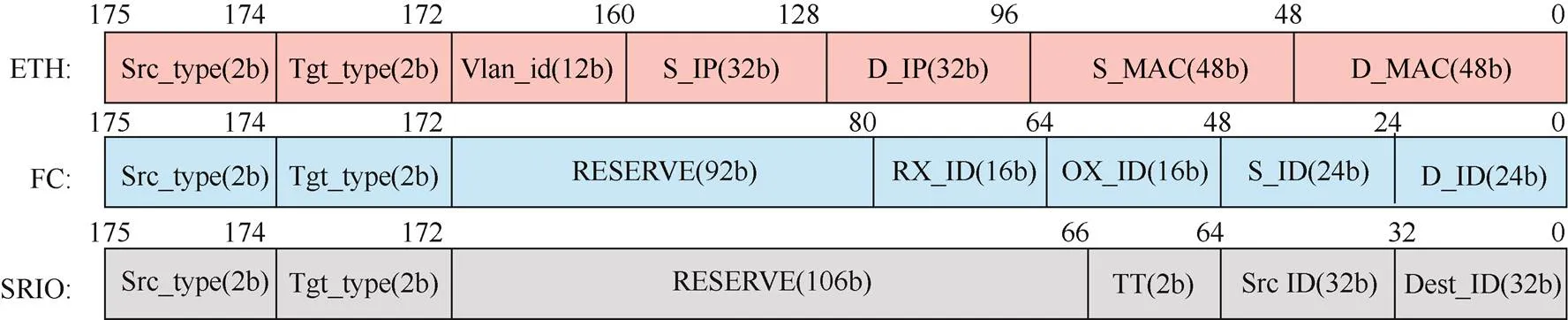

图3 3种协议的关键字段信息

Figure 3 Key data of three protocols

数据包的包头信息中包含类型域字段和匹配域字段,类型域中的信息表示包头的协议类型,匹配域表明当前包头类型需要匹配提取的字段。包头包含多种协议类型时,需要根据当前头类型以及状态信息进行向下一层协议头类型域的跳转。根据初始MF提供的信息,可以由首段头类型以及头状态对下一个报头类型以及偏移进行判断并更新包头解析状态转移信息,根据当前头状态以及头类型还可以进行关键信息的匹配与提取,匹配的规则存储在RAM(random access memory)中。提取到的关键信息字段被添加到MF的关键字段域,通过状态的跳转迭代进而不断地对关键信息进行提取,最终形成包含所有关键信息字段的MF。

图3为ETH协议、SRIO协议以及FC协议这3种常见协议提取出的关键字段信息,ETH协议的关键字段信息有源MAC目的MAC、源IP目的IP、VLAN_ID以及包类型;FC协议的关键字段信息有源ID目的ID、RX_ID以及OX_ID;SRIO协议的关键字段信息有TT字段、源ID和目的ID。由于各协议的关键字段信息数量并不相同,域的位宽设置为协议中最长的以太网协议所需要的位宽176 bit,未使用的位宽将会被保留。

帧头处理模块依据生成的描述符中的包控制流信息进行包的复制和切分,同时对切分的包进行新的MF的生成,内容包括总切片数量、总长度、各类包的源地址、目的地址以及各类控制信号等。

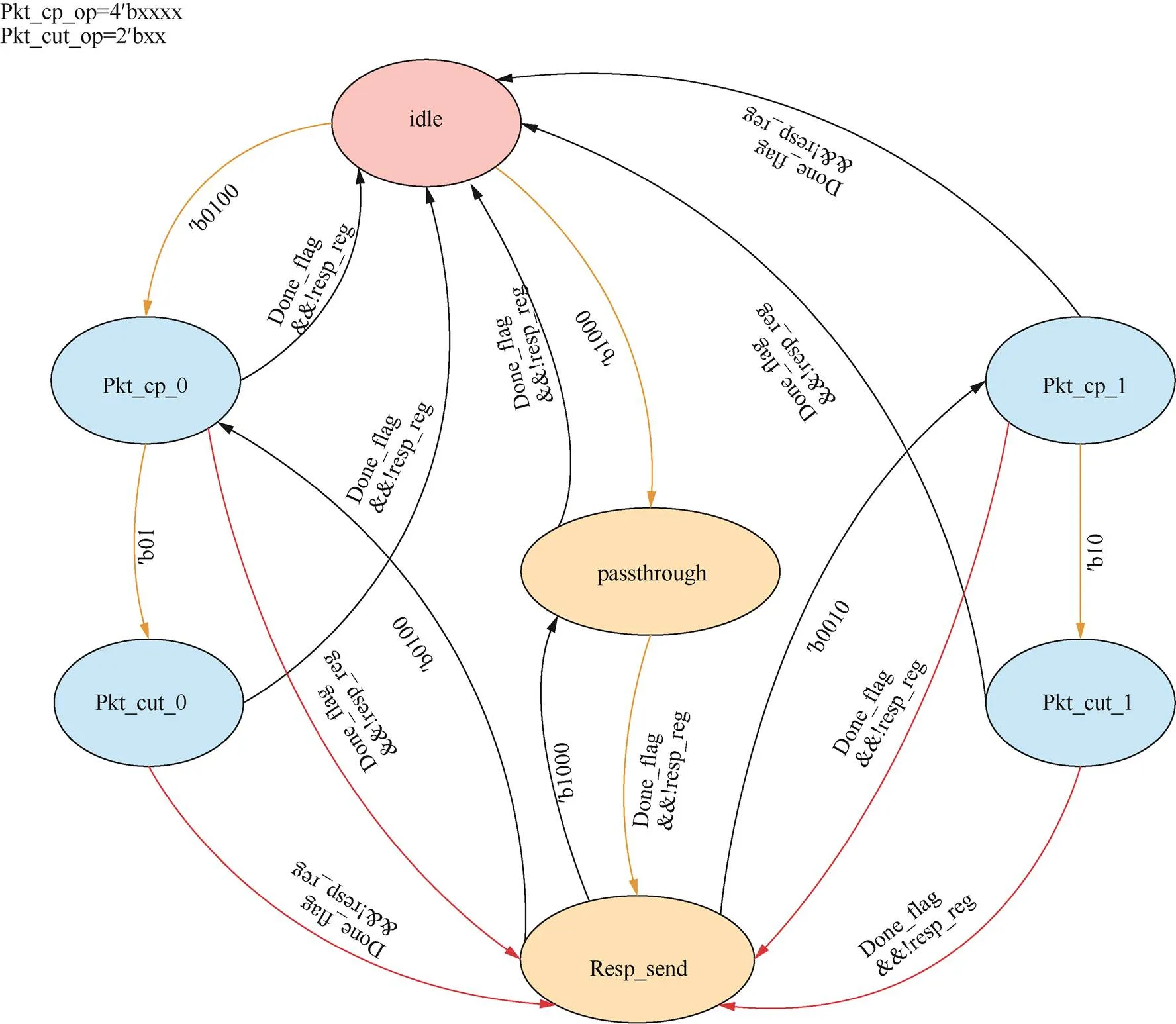

图4为报文调度模块的状态转移图,通过提取MF中的相应控制字段信息,在各个阶段对帧头处理模块进行相应的操作,包括报文透传(pass through)、复制报文的帧头复制(Pkt_cp)、拆包(Prt_cut)、插入response报文(resp_send)等。首先报文进入模块后,根据Pkt_cp_op字段判断是否为透传或复制并进行状态转移,再根据Pkt_cut_op字段决定是否需要切包,所有状态都需要根据数据包的事务类型对是否产生响应包进行判断,同时,跳转至响应包状态。响应包状态也同样需要进行是否发生透传复制以及切包的判断。

图4 帧头处理模块状态转移图

Figure 4 State transition diagram of frame header processing module

最终由帧头处理模块送往slice的内容为MF+payload的组合,slice将payload负载内容送往目的端口并提取MF中的原始报文头域段拼接成完整的数据包。

4 实验结果分析

本文在Xilinx UltraScal+ XCVU13P 开发板卡上成功完成了软件定义协议无关解析器的设计与实现,并通过Vivado仿真平台,以Virtex 7vx980tffg1930-2L为核心芯片,完成了解析器的资源开销分析与性能仿真。

在实际设计中,笔者为解析器设计了4个并行通道,同时对应4个通信端口0、1、2、3,提供4x、2x2x、2x1x1x、1x1x1x1x4个模式,用户可以通过直接配置相应的寄存器来选择对应的模式。4x模式时,只开启端口0,一个端口同时使用4个并行通道,提升单端口解析速率;2x2x模式时,开启0、1两个端口,每个端口使用两个并行通道;2x1x1x时,开启0、1、2这3个端口,端口0使用两个并行通道,其他端口各使用一个通道;1x1x1x1x模式时,则4个端口分别使用一个并行通道。每个端口都可以通过配置来选择支持解析的协议类型,即解析器在开启多个端口时可以同时支持多种协议的并行解析。

4.1 硬件资源开销

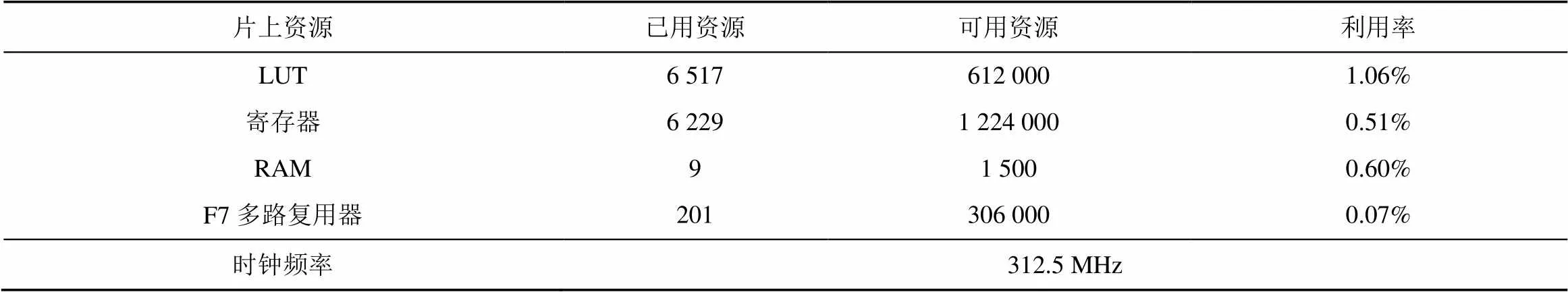

表1中给出了硬件资源使用情况,时钟频率为312.5 MHz,其余内容包括片LUT的数量、片寄存器的数量、块RAM的数量以及多路复用器的数量。

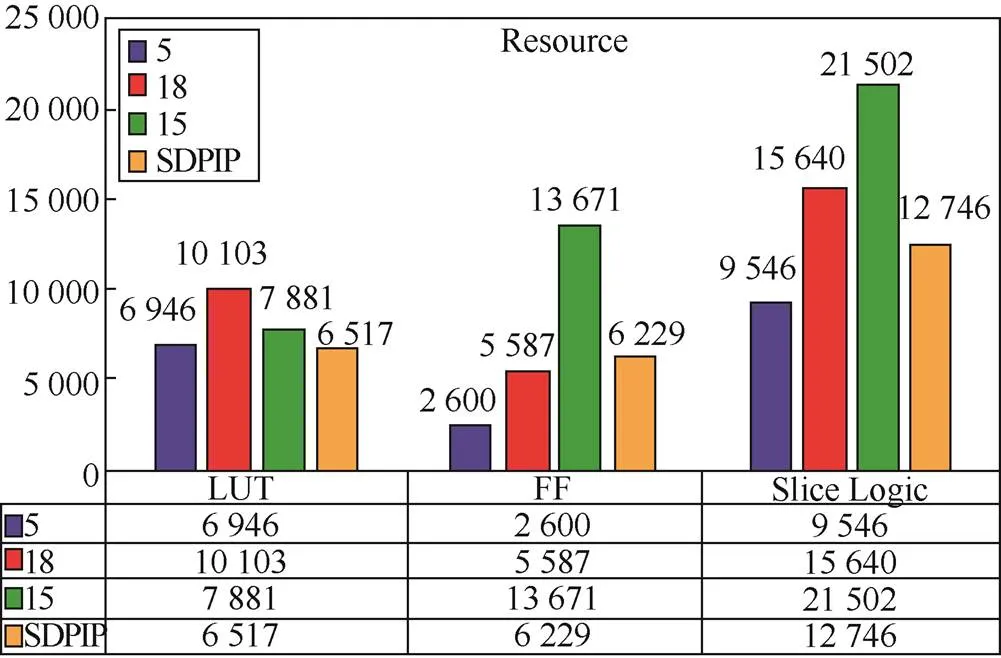

本文将SDPIP的资源使用情况与其他解析器进行了比较,如图5所示,可以看出,本文提出的软件定义协议无关解析器使用的资源相对较少。

表1 硬件资源使用情况

图5 硬件资源开销对比

Figure 5 Comparison of hardware resource overhead

4.2 解析性能评估

本文提出的软件定义解析器设计,其数据总线位宽为256 bit,时钟频率为312.5 MHz,表明可以达到80 Gbit/s的解析速率。通过软件定义完成了解析器对ETH协议、SRIO协议以及FC协议的支持,并通过思博伦SPT-N4U标准以太网流量测试仪、FC流量测试仪以及SRIO流量发生器[14]产生标准数据包,对解析器的多协议数据包解析性能进行了验证与评估,实验结果证明本解析器可以正确地解析数据包,并达到80 Gbit/s的解析速率。

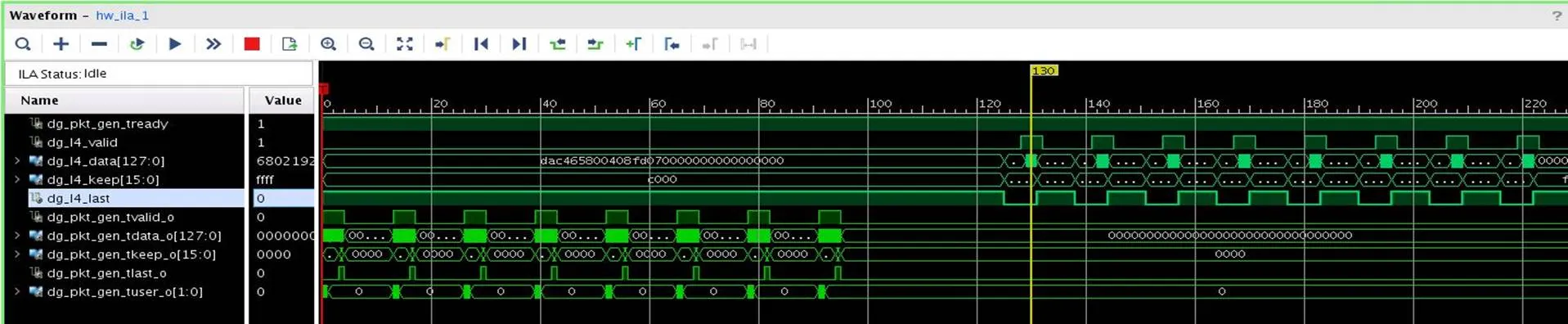

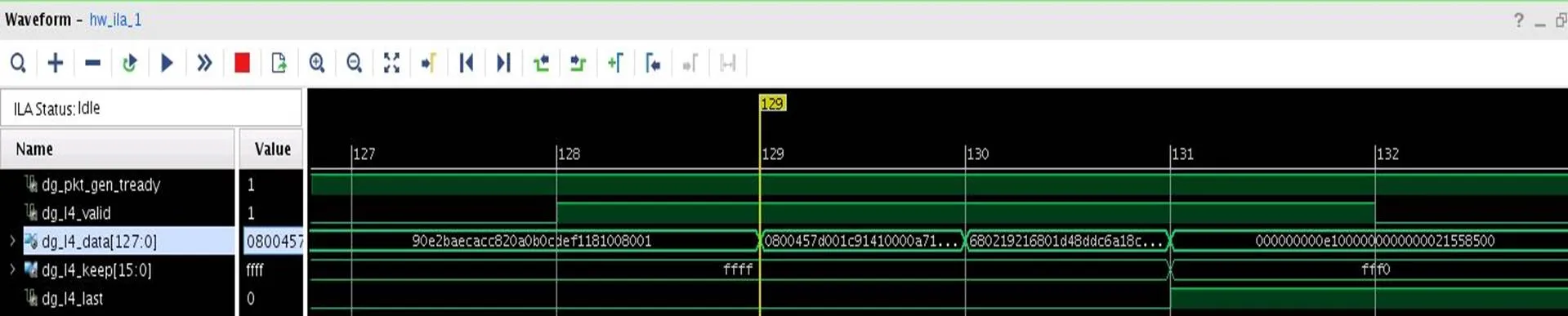

图6是解析器接收标准以太网流量测试仪发送数据包时的波形,共发送8个payload为64 byte的以太网数据包,解析器全部收到。图7中是接收到的数据包的包头结构,经过验证符合以太网协议标准,证明本解析器可以正确解析以太网数据包。同理,本文还对标准SRIO数据包和FC数据包进行了验证,并且进行了长时间的拷机测试,各解析器性能对比如图8所示。结果均表明可以正确解析不同协议的数据包。

图6 以太网接收数据包波形

Figure 6 Ethernet receives packet waveforms

图7 以太网包头数据

Figure 7 Ethernet packet header data

从图6可以看出,SDPIP的资源开销比文献[7]中解析器少40.8%,比文献[10]中解析器少18.6%,虽然解析速率降低了20%,但支持软件定义的协议无关解析,可编程性与灵活性更高,具有更广泛的应用前景。

图8 各解析器性能对比

Figure 8 Performance comparison between parsers

5 结束语

针对目前异构融合网络飞速发展,转发设备的解析器无法支持多种异构协议的问题,本文通过软件定义的思想,提出了一种基于FPGA的软件定义协议无关解析器,并在FPGA上对该解析器设计进行了实现。实验结果表明,该解析器可以通过软件定义有效地对多种包头结构差异明显的网络协议数据包进行快速解析,实现了协议无关这一功能,在硬件上的开销比一般的解析器有明显降低。因此,该解析器可以更好地支持新协议设备在异构融合网络中的部署,减少网络系统设备开销,符合未来网络发展的需要。

[1] FULLER S. RapidIO: the embedded system interconnect[M] . Piscataway, NJ: Wiley, 2005

[2] LIU B, ZHANG J D, YANG Q M, et al. Modeling and performance analysis of FC-AE-ASM which base on Petri net theory[C]// International Conference on Computational Intelligence and Software Engineering.2011: 1-4.

[3] NGUYN V G, BRUNSTROM A, GRINNEMO K J, et al. SDN/ NFV-based mobile packet core network architectures: a survey[J]. IEEE Communications Surveys & Tutorials, 2017, 19(3): 1567-1602.

[4] KREUTZ D, RAMOS F M, VERISSIMO P E, et al. Software-defined networking: a comprehensive survey[J]. Proceedings of the IEEE, 2015, 103(1): 14-76.

[5] PATI S, NARAYANAN R, MEMIK G, et al. Design and implementation of an FPGA architecture for high-speed network feature extraction[C]//International Conference on Field-Programmable Technology. 2007: 49-56.

[6] YAZDINEJAD A , BOHLOOLI B, JAMSHIDI K. (2018). Efficient design and hardware implementation of the OpenFlow v1. 3 switch on the Virtex-6 FPGA ML605[J]. The Journal of Supercomputing, 2017, 74(3): 1299-1320.

[7] LIU T. Implementing Open flow switch using FPGA based platform[J]. Department of Telematics, 2014.

[8] 王孝龙, 刘勤让, 林森杰. 一种支持异构协议解析的可配置解析器设计[J]. 计算机应用研究, 2018, 35(6): 1830-1833.

WANG X L, LIU Q R, LIN S J. Configurable parser design for heterogeneous protocols[J]. Application Research of Computers, 2018, 35(6): 1830-1833.

[9] 杨惠, 冯振乾, 厉俊男. 基于FPGA的并行多发可编程解析器[J]. 计算机工程与科学, 2019, 41(1): 24-30.

YANG H, FENG Z Q, LI J N. A multi-concurrent programmable parser based on FPGA[J]. Computer Engineering & Science, 2019, 41(1): 24-30.

[10] BITAR A, ABDELFATTAH M S, BETZ V. Bringing programmability to the data plane: packet processing with a NoC-enhanced FPGA[C]//In 2015 International Conference on Field Programmable Technology (FPT). 2015: 24-31.

[11] BOSSHART P, DALY D, GIBB G, et al. P4: Programming protocol-independent packet processors[J]. SIGCOMM Computer Communication Review, 2014, 44(3): 87-95 .

[12] SILVA J S D, BOYER F R, LANGLOIS J M, et al. P4-compatible high-level synthesis of low latency 100 Gbit/s streaming packet parsers in FPGAs[J]. arXiv preprint arXiv:1711.06613, 2017.

[13] BENÁCEK P, PU V, KUBÁTOVÁ H. P4-to-VHDL: automatic generation of 100 Gbit/s packet parsers.[C]//2016 IEEE 24th Annual International Symposium on Field-Programmable Custom Computing Machines (FCCM). 2016: 148-155.

[14] 吕平, 董春雷, 刘冬培, 等. 基于FPGA的软件定义流量发生器[J]. 通信学报, 2018, 39(S2): 70-75.

LYU P, DONG C L, LIU D P, et al. Implementation of software defined traffic generator based on FPGA[J]. Journal on Communications, 2018, 39(S2): 70-75.

Software-defined protocol independent parser based on FPGA

MIAO Lixin, LIU Qinrang, WANG Xin

National Digital Switching System Engineering and Technological Research Center, Zhengzhou 450002, China

With the boom of information technology, heterogeneous networks with various functions emerge in endlessly, heterogeneous fusion network has become the inevitable trend of the development of the next generation network. To realize communication between heterogeneous networks, network forwarding equipment is essential. Traditional forwarding devices only support fixed protocol configuration and lack scalability, so they cannot support new network protocols. In view of this situation, a software defined protocol independent parser based on FPGA was proposed. The software defined the parsing process, giving the parser flexible and programmable features. It can analyze multiple protocol packets and extract key information needed for protocol conversion without changing hardware devices. The parser through a high-performance FPGA platform were implemented and hardware resource overhead and performance were evaluated. Experimental results show that it can complete the fast parsing of various heterogeneous network protocols and obtain complete analytical data.

FPGA, software define, parser, protocol independent

The National Science Technology Major Program of China (No.2016X01012101)

TP393

A

10.11959/j.issn.2096−109x.2020013

苗力心(1995− ),男,辽宁丹东人,国家数字交换系统工程技术研究中心硕士生,主要研究方向为软件定义互连、FPGA。

刘勤让(1975− ),男,河南商丘人,国家数字交换系统工程技术研究中心研究员,主要研究方向为宽带信息网络、片上网络设计。

汪欣(1986-),男,河南周口人,硕士,主要研究方向为系统结构。

2019−04−22;

2019−06−28

苗力心,352192875@qq.com

国家科技重大专项基金资助项目(No.2016X01012101)

论文引用格式:苗力心, 刘勤让, 汪欣. 基于FPGA的软件定义协议无关解析器[J]. 网络与信息安全学报, 2020, 6(1): 70-76.

MIAO L X, LIU Q R, WANG X. Software-defined protocol independent parser based on FPGA[J]. Chinese Journal of Network and Information Security, 2020, 6(1): 70-76.