一种新型亚阈值SRAM单元设计

孔得斌,乔树山,袁甲

中国科学院微电子研究所,北京100029

随着近年来市场对低功耗电子设备需求的激增,功耗已取代高性能成为大部分电路设计的重点关注对象[1]。由于静态随机存储器(SRAM)在片上系统(SoC)功耗中的占比较大,低功耗的SRAM设计是必要且有吸引力的。降低电源电压能够成平方倍地减小动态功耗、线性地降低漏电功耗,因此将电源电压降低到近阈值或亚阈值区一直是低功耗逻辑电路和SRAM电路的研究重点[2]。在近阈值或亚阈值区,随机掺杂涨落和线边缘粗糙加剧工艺偏差和器件失配[3],并且工艺电压温度PVT偏差对金属氧化物半导体(MOS)管的驱动电流具有指数级的影响,此外显著减小的MOS 管开关电流比使读操作时访问单元的正常放电电流和非访问单元的积累漏电流之间的界限模糊,这会造成更慢甚至错误的读操作。管子尺寸方面,传统6T 单元的写能力和读稳定性对管子尺寸具有不一致的需求,并且低压下由于阈值偏差带来的影响加剧,依靠管子尺寸调节来获得充足读稳定性和写能力的方式不再奏效。以上所有因素决定了传统6T单元不能工作在近阈值或亚阈值区。

为了获得低压SRAM,一方面不同的写辅助或读辅助策略被用来降低6T SRAM 的工作电压,字线电压抬升技术[4]、电源电压降低技术[5]和位线负偏压技术[6]是提升6T单元写能力的主要技术手段,但是字线电压抬升技术会降低同一行上半选单元的读稳定性,电源电压降低技术会降低同一电源线上半选单元的保持稳定性,位线负偏压技术采用的大电容会牺牲面积和功耗。读辅助方面,参考文献[7]采用字线电压抑制的方式牺牲读速度换取读稳定性;参考文献[8]采用位线电压抑制的方式提升读稳定性,但过低的位线电压同样会降低单元的读稳定性,产生期望的中间电压比较困难。

另一方面各种新单元被提出以解决6T单元面临的挑战。读写端口分离的8T单元[9,10]和10T单元[11]通过将存储节点与读位线隔离使单元的读噪声容限(RSNM)等于保持噪声容限(HSNM)从而大大提升了自身读稳定性。随着电压的降低SRAM发生软错误的概率增大[12],有必要基于位交织结构实施检错纠错方案[13]。不幸的是读写端口分离的单元不适用于位交织结构,否则同一行上的半选单元在写操作时会受到读干扰[14],并且8T和10T单元结构的单端读特性会使访问速度降低,此外额外的读位线增加了漏电功耗。

总之考虑到稳定性、软错误、访问速度和功耗等因素,差分读取、抗噪声干扰并具有位交织能力的单元的设计对于低电压SRAM设计来说是有竞争力和吸引力的。

1 对比单元

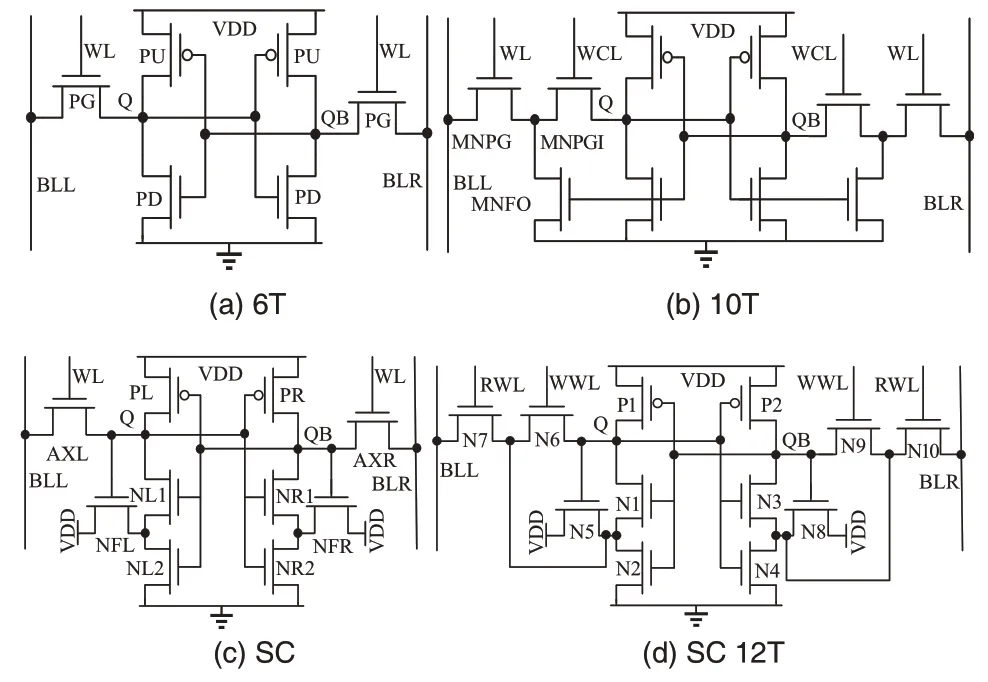

经典6T 单元结构如图1(a)所示,该单元由上拉管PU、下拉管PD 和访问管PG 三部分组成,由于写操作时同一行上的半选单元存在读干扰,位交织的6T SRAM不能采用字线电压抬升和电源电压降低的写辅助策略。差分10T单元如图1(b)所示[15],该10T单元读稳定性较高并且适用于位交织结构,但是低压下受存储数据模式和PVT偏差的影响,差分10T 单元的读速度降低甚至会出现读错,这限制了其工作电压的降低。参考文献[16]提出了如图1(c)所示的施密特结构单元SC,得益于内部的反馈机制,SC单元的噪声容限和写能力相比于6T单元都有所提升,但放电路径上堆叠的NMOS导致读速度降低并且同一行上的半选单元同样存在稳定性问题。参考文献[17]提出了如图1(d)所示的SC 12T 单元,该单元的读稳定性相较于SC 单元进一步提升,为了改善写能力,SC 12T 单元采用混合阈值设计方法,N7和N10为低阈值管,其余部分为常规阈值管,这种混合阈值设计降低了RSNM、增加了位线漏电。

图1 对比单元Fig.1 Previous bitcells

2 新型12T单元

为了弥补6T、差分10T、SC 和SC 12T 单元的不足,本文设计了一种稳定的、适用于位交织结构的新型亚阈值12T单元,如图2所示。12T单元由4部分组成,分别为对称的访问部分(NAL1,NAL2,NAR1,NAR2)、背靠背反相器部分(PL1,NL1,PR1,NR1)、读操作放电管部分(NLD1,NRD1)和位线漏电补偿BLLC 部分(PLD1,PRD1)。新型12T 单元中堆叠的写访问管降低了单元写能力、额外的漏电路径增加了静态功耗,本文采用混合阈值的设计方法解决这两个问题。读放电路径上NAL1、NLD1、NAR1 和NRD1 采用常规阈值管以均衡读速度和位线漏电流;为了提升写能力降低单元漏电,NAL2和NAR2采用低阈值管而PL1、PR1、NL1和NR1采用高阈值管;考虑到对位线的漏电补偿能力,将PLD1和PRD1设置为常规阈值管。需要注意的是BLLC 的使用会削弱单元保持1 的能力,因此HSNM降低,此外更多的管子和多阈值技术的使用增加了单元的面积。

图2 多阈值12T单元Fig.2 Multi-vth 12T bitcell

3 仿真对比

基于中芯国际SMIC 55nmLL 低漏电工艺,采取HSPICE 仿真的方式,本节给出了几种单元在读稳定性、写能力、漏电功耗、访问速度、漏电补偿等方面的详细对比,充分证明了本文设计单元在低压下的优势。

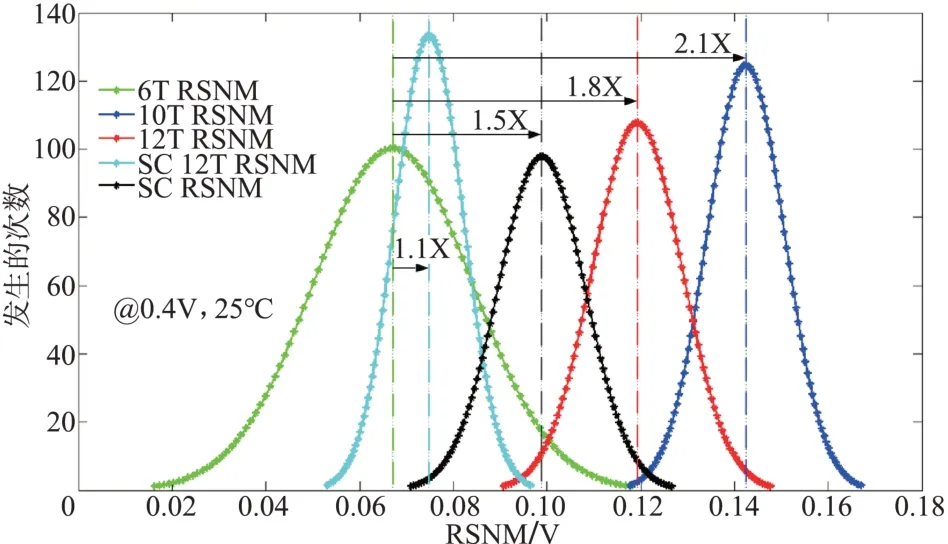

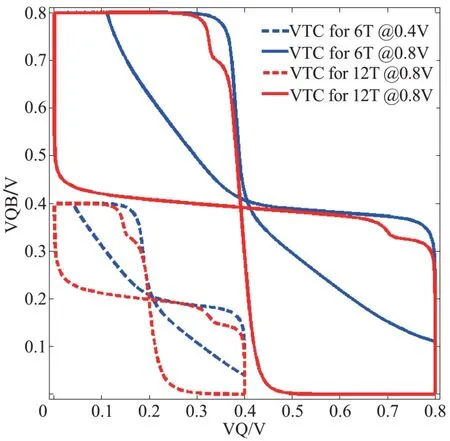

3.1 保持噪声容限HSNM

在0.4V 25℃条件下对5 种单元的做1000 次蒙特卡罗仿真得到的保持噪声容限正态分布拟合曲线如图3 所示,曲线越瘦高则噪声容限偏差越小,越靠近右侧噪声容限均值越大、稳定性越好。图4 给出了6T 和12T 单元的电压传输特性曲线,即蝶形曲线,曲线所夹正方形的面积越小表明单元抗噪声能力越差、稳定性越差,相应的在图3中曲线越靠左,噪声容限越小、稳定性越差。可以看出相比于6T 单元,12T单元的HSNM减小了14%,这种保持稳定性损失是可以接受的,因为HSNM 不是限制单元低压工作的关键因素。

图3 保持噪声容限正态分布拟合曲线Fig.3 HSNM normal distribution fitting curve

图4 保持状态电压传输特性曲线Fig.4 Voltage transfer curve at hold state

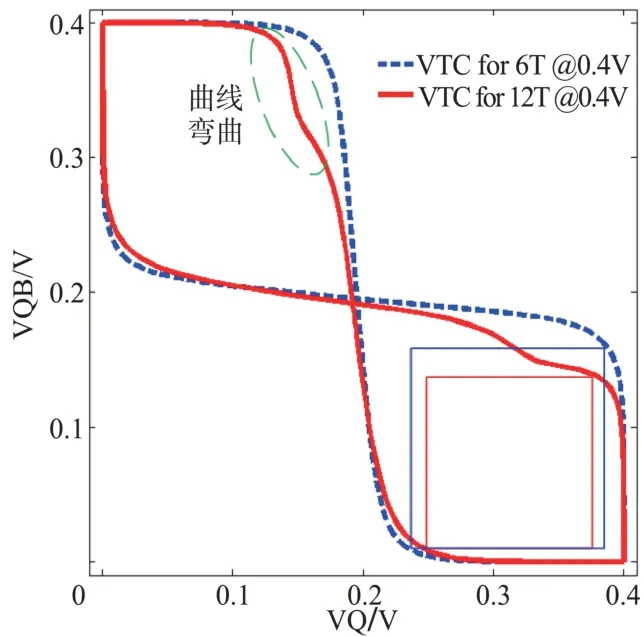

3.2 读噪声容限RSNM

在0.4V 25℃条件下对5 种单元的做1000 次蒙特卡罗仿真得到的读噪声容限正态分布拟合曲线如图5所示。图6给出了读操作的电压传输特性曲线。

图5 读噪声容限正态分布拟合曲线Fig.5 RSNM normal distribution fitting curve

读操作时,12T 单元的WL 打开、WWL 关闭,得益于BLLC 对读噪声的隔离作用,12T 单元的RSNM 相比于6T单元提升80%、相比于SC单元提升20%,读稳定性好。

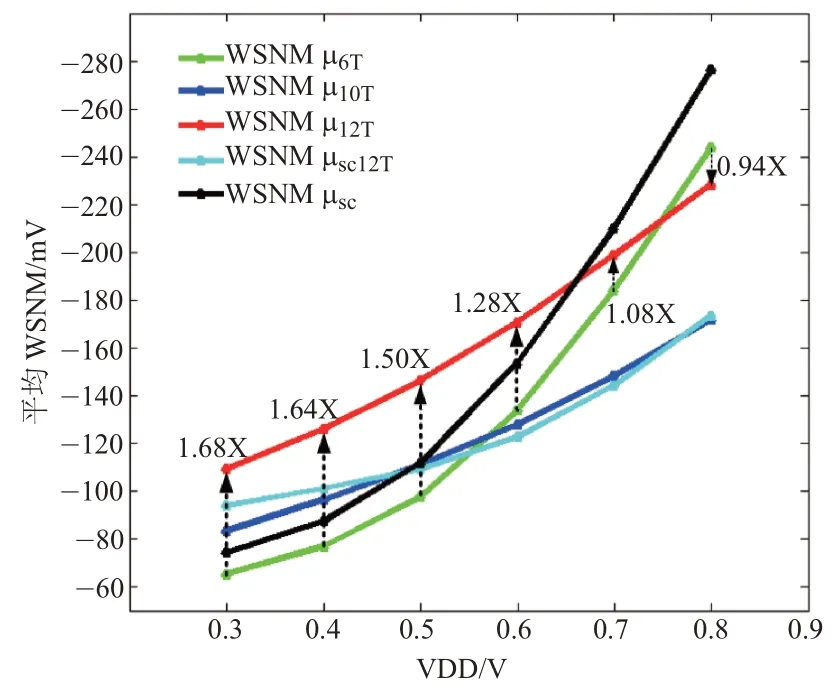

3.3 写噪声容限WSNM与读速度

写操作时12T 单元的WL 和WWL 都使能有效,图7 给出了蒙特卡罗仿真得出的写噪声容限均值WSNM 随VDD的变化,其中WSNM的值越负代表单元的写能力越强。得益于混合阈值的设计技术,12T单元的写1能力和写0能力都变强,在0.6V 及以下电压下12T 单元相比其他4 种单元具有最强的写能力,在0.4V 电压下12T 单元写能力相比于6T单元提升64%。

图6 读操作电压传输特性曲线Fig.6 Voltage transfer curve at read state

图7 WSNM均值随VDD变化Fig.7 Mean WSNM vs VDD

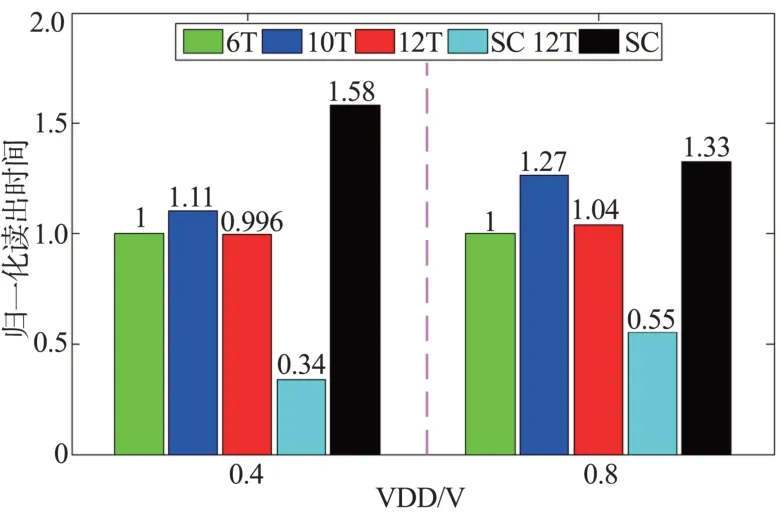

读速度由字线WL打开后位线形成50mV电压差需要的时间表示,位线上的单元数量为64,仿真结果如图8所示,可以看出SC 12T单元因为具有低阈值访问管读速度最快,但牺牲了大量RSNM。SC单元放电路径上堆叠的NMOS管使其访问速度最慢。因同一条位线上非访问单元的漏电,10T 单元的读速度比6T 和12T 单元慢。6T 单元和12T 单元因为都具有位线漏电补偿能力,二者访问速度相当。

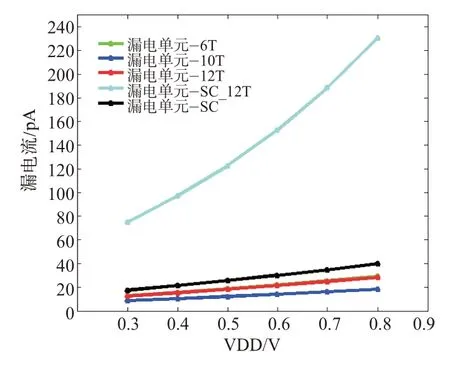

3.4 漏电流与位交织

单元的总漏电包括电源VDD的漏电(latch部分)和经两条位线的漏电,5种单元的漏电流随工作电压的变化关系如图9所示。SC 12T单元中低阈值访问管使其漏电流远大于其他4种单元。由于高阈值管的使用,12T单元的漏电流稍低于6T单元。

图8 归一化读出时间Fig.8 Normalized access time

图9 漏电流与电压关系Fig.9 Leakage current vs VDD

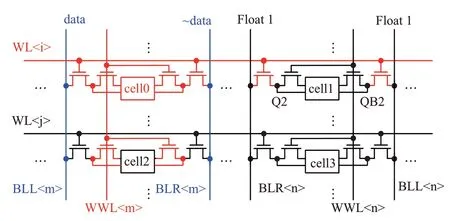

图10 给出了12T 单元写操作时选中单元、半选单元和未选中单元的状态,可以看出同一行上的半选单元cell1和同一列上的半选单元cell 2 的内部存储节点都不会受位线电平的干扰,即12T单元适用于位交织结构。

3.5 位线漏电补偿与面积

图10 写操作时选择单元、半选单元和未选单元Fig.10 Select,half-select and unselect cells during write operation

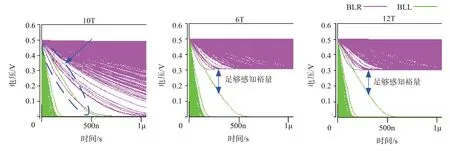

为了说明位线漏电流对读操作的影响,对6T、10T 和12T 三种单元做1000 次蒙特卡罗瞬态仿真,结果如图11所示。对于低压工作的差分10T 单元来说位线上非访问单元的总漏电可能超过正常的开启电流,导致两边位线逻辑0和逻辑1界限模糊,感知裕量的消失使数据读出失败,并且位线漏电流对PVT 变化敏感且受存储数据模式的影响,如果采用外围电路补偿位线漏电则会引入额外的能量消耗和速度损失。因此单元中自适应地漏电补偿功能对于可靠的数据读出是必要的。12T 单元中BLLC 部分PMOS管能够在读操作时自适应地补偿位线漏电,因此感知裕量更大、读速度更快。6T 单元也具有这种漏电补偿能力。

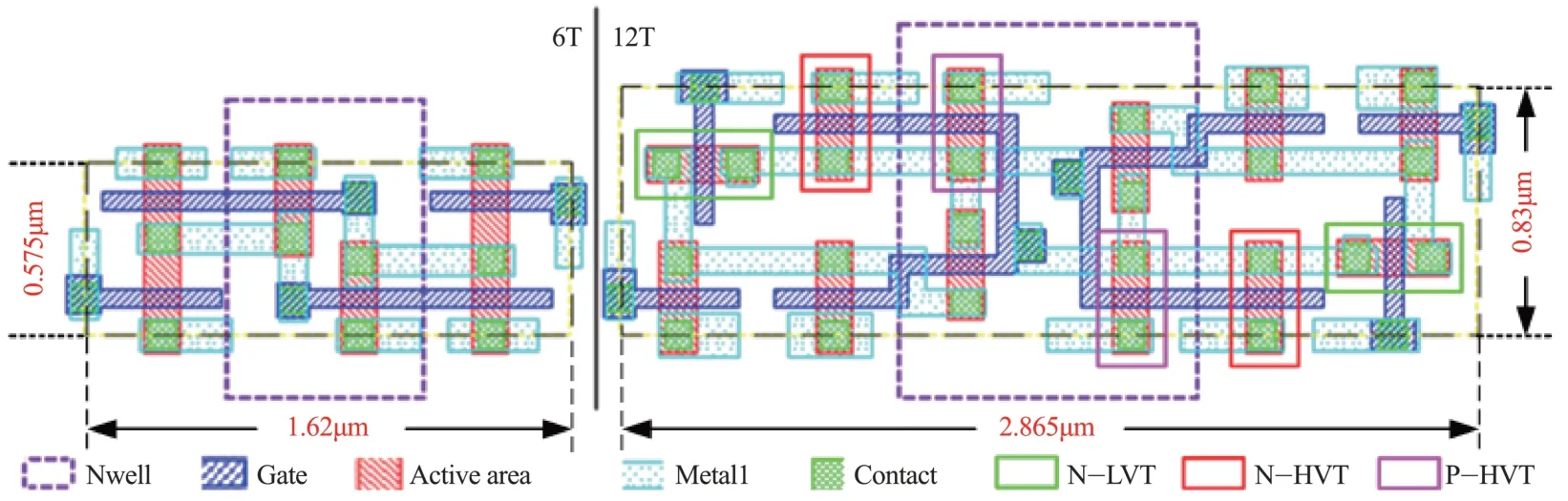

图12 给出了6T 单元和新型12T 单元的版图结构(SMIC 55nmLL工艺,采用普通逻辑电路DRC规则),最终6T单元的面积为1.62μm×0.57μm,12T单元的版图面积为2.865μm×0.83μm,12T 单元的面积为6T 单元面积的2.58倍,面积增大的原因有两个,一是12T单元中MOS管的数量多,二是多阈值的设计方法使部分有源区不能复用。

3.6 对比总结

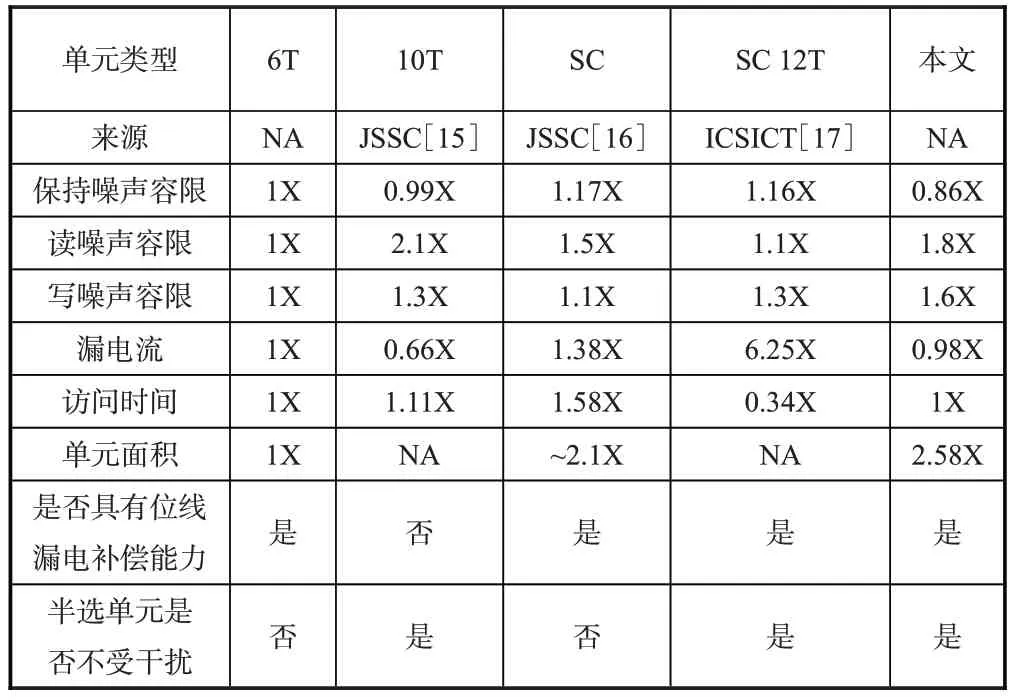

5种单元各种指标的仿真对比总结见表1,可以看出新型12T单元集合了其他4种单元的各种优点,很好地均衡了稳定性、写能力、漏电与访问速度,并且同时具有位线漏电补偿和适用与位交织的特性。

图11 漏电流与电压关系Fig.11 Leakage current vs VDD

图12 6T单元和12T单元版图Fig.12 Layout of 6T cell and 12T cell

表1 对比总结Table 1 Summary comparisions

4 结束语

本文设计了一种读稳定性好、写能力强、静态功耗小、具有位线漏电补偿能力并适用于位交织结构的新型亚阈值12T单元,该12T单元能够工作在更低的工作电压下,因此在低电压SRAM 设计领域更具有竞争力,芯片更低的工作电压有利于降低航空电子设备的功耗。12T单元的缺点是面积较大。