基于兆芯X86 架构处理器的国产化CPCI 主板设计

王浩宇

(四川省绵阳西南自动化研究所, 四川 绵阳 621000)

0 引言

根据统计数据显示自2013 年起集成电路已超过原油成为我国第一大进口商品,至2018 年集成电路进口规模已超3000 亿美元。 其中CPU 及存储器两类占70%份额。 处理器以Intel、AMD 的X86 架构为主。

X86 架构处理器以其强大的性能、友好的人机交互、良好的软硬件生态环境优势被广泛地应用于个人计算机、工业控制、党政办公系统、军用计算机等领域。

随着我国的快速崛起,国际形势也随之变化,而我国对国外以处理器为代表的集成电路的高度依赖, 导致在该领域有随时被“卡脖子”的可能,严重威胁到国家的安全战略。

目前国内通过IP 授权的方式取得X86 处理器研制生产的厂商有两家, 分别是兆芯及海光。 从而实现X86架构处理器国产化。

本文对基于兆芯X86 处理器并搭载外围国产化电路实现全国产化的一款CPCI 工控主板实现方案进行介绍。

1 兆芯处理器介绍

兆芯X86 处理器自2015 年第一款ZX-C 系列处理器量产以来, 经过4 年的积累, 产品迭代, 最新处理器ZX-E 系列已可对标7 代I5 桌面版。

兆芯处理器广泛地应用于安可系统、银行系统、党政办公系统等专用领域。 兆芯公司同时拥有CPU、芯片组及GPU 的IP,其硬件生态比较完整。 昆仑、百敖及AMI 均能对兆芯处理器进行BIOS 支持。

目前兆芯处理器分为开先及开胜两条产品线。 开先应用于PC 机、笔记本、工业控制及嵌入式等领域,开胜主要应用于服务器、存储等领域。 考虑到本主板的应用方向选择了开先处理器。 开先处理器包括ZX-C、ZX-C+、KX-5000 及KX-6000 四大系列。 本文选择功耗、性能较为均衡且支持XP 操作系统的ZX-C+处理器C4701,并搭载桥片ZX100S。

2 主板详细设计

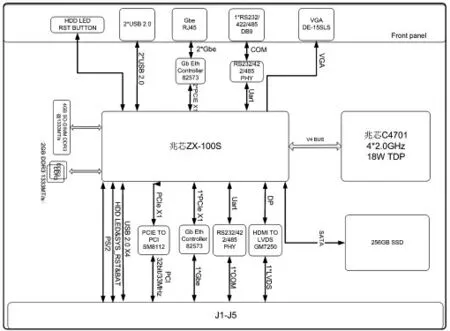

如图1 所示本主板以兆芯处理器C4701 加桥片ZX-100S 搭建最小系统,并在外围搭配接口芯片扩展出以太网接口、串口、USB 接口、VGA 显示等,实现系统间数据交互及人际交互等功能, 通过PCIE to PCI 桥扩展出一路PCI 总线实现系统内部数据传输。

图1 主板系统框图

2.1 电源设计

兆芯平台的电源设计主要包含两个方面, 第一是时序设计、第二是CPU 核电源设计。 下面分别对上述两点进行说明。

2.1.1电源时序设计

本设计中有严格时序要求的是处理器C4701 及桥片ZX-100S。 其中处理器仅3 路电源VCC、VCCA 及VCCP,上电时序要求为VCCA 与VCCP 同时上电,VCCA 与VCCP 在VCC 之前或者一起上电。 在本文中选择VCCP 及VCCA 先于VCC 上电。

ZX-100S 电源多大13 种,上电时序较为复杂,其时序如图2 所示。

图2 ZX-100S 上电时序图

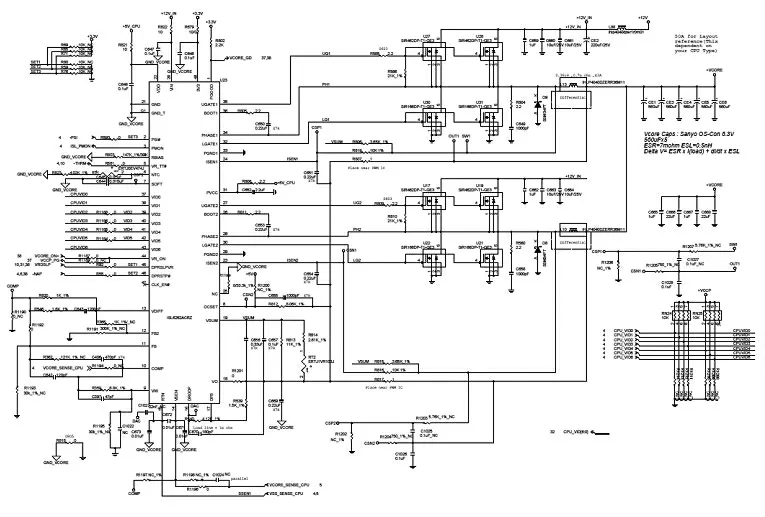

2.1.2 CPU核电源设计

本文设计一片国产PWM 信号调试器PT9528 替换ISL6262。 PT9528 与ISL6262 指标一致, 封装及信号定义PIN TO PIN 兼容。在外围电路存在差别,具体如图3 所示。

2.2 内存设计

ZX-100S 集成两个64bit DDR3 控制器,最高带宽可达1600MT/s。 本文通过其中一路通道扩展2GB 板载内存颗粒,另一通道引出一路SO-DIMM 内存接口。

图3 处理器核电源电路图

内存设计中较为重要的是时序控制及阻抗控制。 其约束条件如下:

表1

2.3 PCIE 接口设计

ZX-100S 集成了19 条高速收发LAN,最高可配置为6 个PCIE 端口。 该配置在BIOS 中实现。 本文中配置出3路X1 PCIE 接口加1 路X2 PCIE 接口扩展出1 路PCI 总线及3 路10/100/1000M 以太网接口。 其中X2 接口可作为1 路X1 接口使用。

本文中选用PCIE TO PCI 桥片SM8122 实现PCI 总线的扩展。 由于SM8112 仅支持4 路仲裁信号,扩展出7路标准PCI 外设则需要增加仲裁信号。 增加仲裁信号有两种方式,第一是通过CPLD 实现外部仲裁器,第二是使用一片PCI TO PCI 桥片SM2050 实现仲裁信号的扩展。本文采用CPLD 实现外部仲裁器的方式扩展仲裁信号。

以太网控制器选择JEM82573。

2.4 串口设计

ZX-100S 集成了4 路UART 接口,本文中使用串口0及串口1 连接RS232 物理芯片SM3232 扩展出两路RS232 接口。串口3 作为调试接口,在调试阶段可在BIOS代码中控制输出调试信息,提高Debug 效率。

3 UEFI BIOS 启动流程介绍

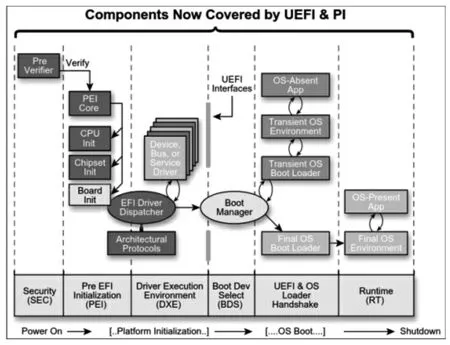

BIOS 在X86 体系中作为软硬件连接的桥梁,其地位无可替代。 图4 是基于UEFI 协议的BIOS启动流程。 UEFI 架构的平台开机由POWERON 开始经历SEC、PEI、DXE、BDS、OS Loader 以及RUNTIME 五个阶段。

图4 BIOS 启动流程图

SEC 阶段:平台开机后即进入SEC Phase,此阶段完成从实模式到保护模式的转换,完成内存的初始化,为后续C 代码的运行提供环境。

PEI 阶段:PEI Phase 会找到BIOS 中所有的PEIM 并根据dependency 来安排调用他们的顺序, 这些PEIM 主要完成PCI 总线, 南北桥设备的基本初始化, 创建一个HobList 传输给DXE Phase。 最后调用DxeIpl 进入DXE Phase。

DXE 阶段:DXE Phase 包含DXE Core,DXE Dispatcher,DXE Driver,DXE Core 会 根 据Dependency 用DXE 调度器安排DXE 驱动的执行顺序。 此阶段用来初始化平台并启动OS 提供一些必要的服务。

BDS 阶段:BDS Phase,即启动设备选择阶段,此阶段会初始化好控制台设备,并且装载所有Driver,并初始化好启动顺序,并选择默认启动项进行启动。

OSLoader: 系统装载器, 主要任务是执行一个Exit-BootServices()的服务,来结束BDS Phase,并把系统控制权交给OS, 此后BootServices 将无效, 只有RuntimeServices 可以使用。

Runtime Phase:OS 掌控整个系统, 此时UEFI OS 将只能使用UEFI 提供的RuntimeSerivices,而不能使用UEFI 的BootServices。

4 结束语

本文中提出一种基于兆芯公司X86 处理器的全国产化CPCI 主板解决方案。 可在工控、军用嵌入式计算机实现对基于INTEL 处理器的CPCI 主板实现软硬件无缝、快速替代。 消除“卡脖子”战略安全隐患。