一种倒装芯片/多层互连结构封装IC的修改方法

林晓玲 章晓文 高汭

(工业和信息化部电子第五研究所 电子元器件可靠性物理及其应用技术重点实验室,广东 广州 510610)

芯片在设计完投片之后,并不能保证投片成功率为百分之百,因此,需要对出问题(即失效)的芯片进行失效分析,以找出导致失效的原因。如果是芯片设计方面的原因导致其失效的,就需要对该芯片进行电路修改,包括对缺失的电路重新连接或者切断多余的金属部位,即利用聚焦离子束(FIB)的电路修改纠错功能修改多层布线结构的器件版图,然后再进行功能验证,确认修改是否成功,如果成功,则纠正设计错误,重新投片[1- 4]。同时,FIB电路修改技术被广泛用于芯片自主研制过程中的失效分析及结构分析中,通过FIB制作剖面结构,找出并观察剖面结构,为确认结构的完整性、工艺缺陷或者物理损伤点的失效机理提供参考依据[5- 8]。结合失效分析技术,FIB电路修改技术被广泛用于失效分析、设计纠错中,对缩短芯片的研制时间、加快芯片的研制过程有重要作用。

晶圆级的测试一般只能实现基本测试功能,完整的电路纠错测试只能在芯片封装之后才能执行。目前,芯片电路修改的主要加工方式为采用FIB在芯片正面进行修改[1- 2],利用FIB的金属沉积功能实现局部互连线重连,或者切割功能实现局部互连线切割。随着半导体工艺制程与封装技术的不断演进,倒装芯片封装成了近年来多功能及高I/O引脚封装,如CPU、FPGA等高端芯片的最佳选择,对倒装芯片进行电路修改和内部节点探测也就成了必不可少的工作。这使传统的FIB电路修改技术面临两大挑战。首先,倒装芯片封装形式的出现成了正面FIB电路修改无法克服的瓶颈之一:倒装芯片的正面朝下,电路置于芯片下方,造成探测电路困难。另外,随着半导体工艺制程的演进,IC所用的金属互连层数增加,用传统方式由芯片正面对底层的金属互连做修改的难度也越来越大,过高纵深比孔成了影响FIB电路修改成功率低的难以逾越的障碍[9- 11]。

针对上述情况,结合倒装芯片封装及多层互连结构集成电路的结构特点,文中提出了结合芯片背面减薄法、基于FIB的深宽广沟槽刻蚀技术、基于动态光栅衍射条纹的沟槽刻蚀终点监测技术、基于二次电子讯号的控制切割制样深度的终点监测技术、聚焦离子束电路修改技术等多种技术相结合的芯片背面电路修改技术,由外观毫无变化的硅芯片的背面入手对晶体管层级的金属互连线进行电路修改,解决倒装芯片正面朝下、电路置于芯片下方而造成探测电路困难的问题;也解决了多层金属互连集成电路由于金属层数太多,从顶层金属入手对最底层MOS晶体管层级的金属互连线进行修改时容易损伤中间互连线的问题。

1 芯片背面电路修改技术原理

1.1 芯片背面减薄技术

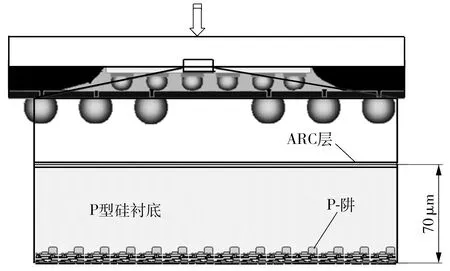

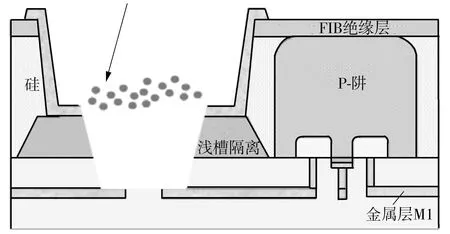

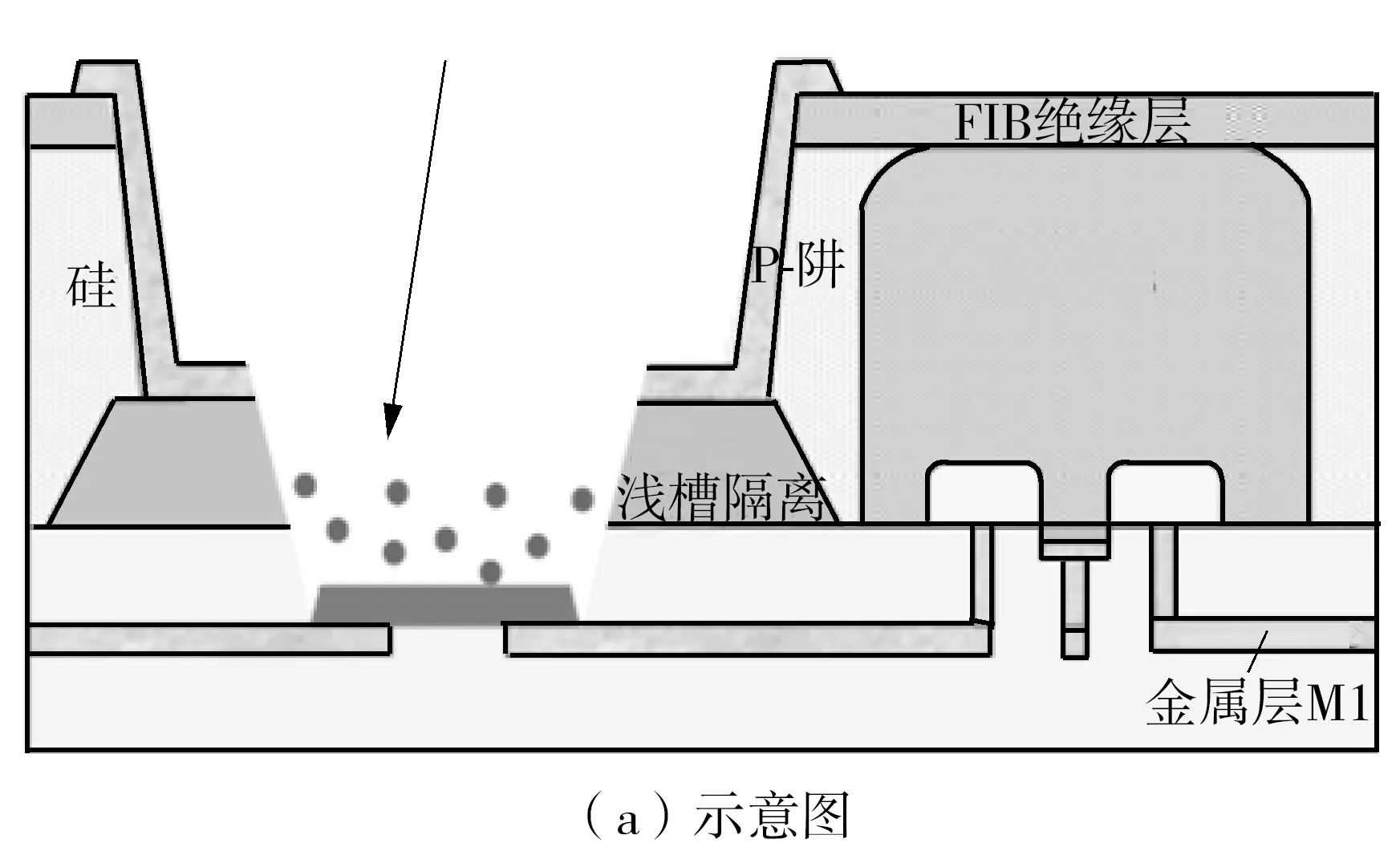

从倒装芯片背面进行电路修改,首先必须打开样品的封装以显露出倒装芯片的背面,接着将原始厚度(约500~700 μm)的倒装芯片减薄、抛光,实现芯片薄化(如图1所示)。芯片经背面薄化至约70 μm之后,停止机械减薄而改为用FIB来进行芯片背面的减薄,以减少机械冲击力对薄化后的芯片造成冲击损伤,使其更加接近所要修改的目标电路位置。

图1 芯片减薄技术示意图Fig.1 Schematic diagram of chip thinning technique

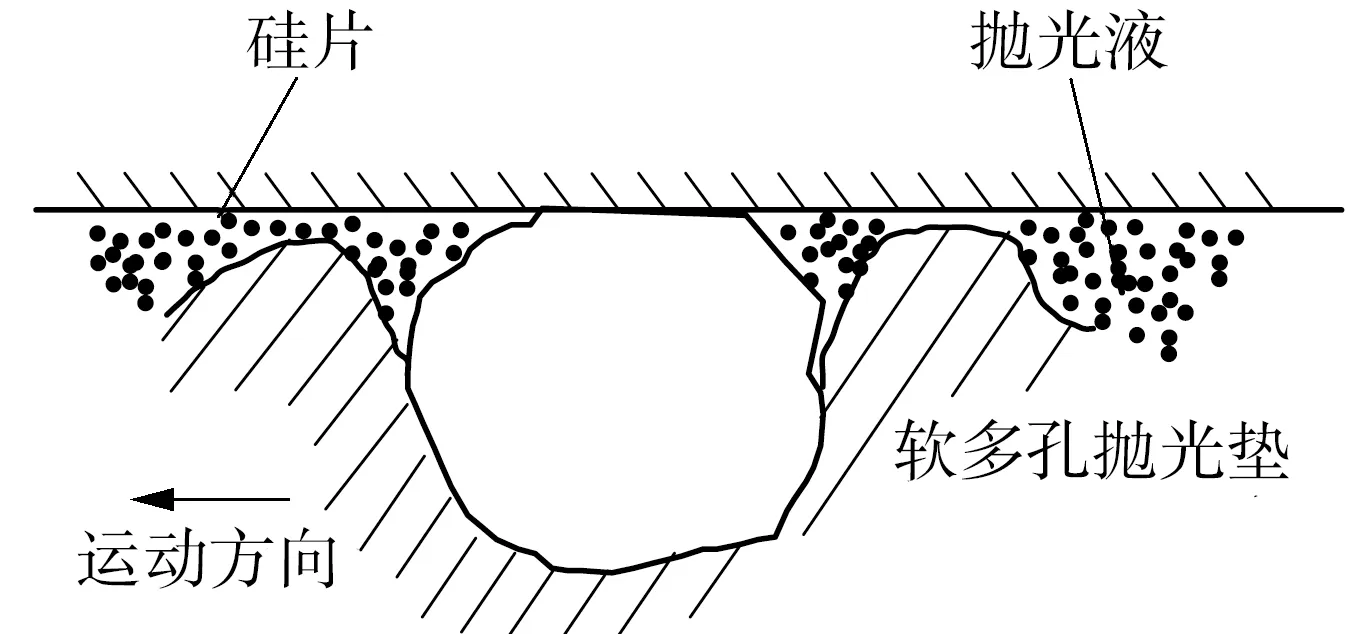

采用全局抛光减薄法进行芯片减薄过程中,芯片减薄时,抛光头自动旋转,以一定的压力将样品压在旋转工作台的抛光垫上。在芯片减薄的过程中,抛光头的转速需很好地控制。转速太快,会使研磨粗糙,且有可能导致过度的抛光;转速太慢,则耗时过长。减薄过程中所加的抛光液由金刚砂加上去离子水组成,两者混合成粘糊状,由抛光液供给系统,以均匀的速率将其注入到抛光头和抛光垫之间流动,抛光液中的化学成分与硅片表面产生化学反应,将不溶物质转化为易溶物质,然后通过磨粒和抛光垫的微机械摩擦作用去除硅片表面的化学反应产物,溶入流动的液体中带走,即在化学成膜和机械去膜的交替过程中实现超精密表面加工,从而达到平坦化的目的,实现硅片的减薄,如图2所示。芯片减薄之后,需进一步进行抛光,以使芯片表面平坦化,减少毛刺或者研磨过程中残留的微粒。此时,抛光浆料换成由pH值在10.7~11.2之间的NaOH溶液和平均粒径在25~60 nm之间的磨粒组成的抛光液。

图2 磨粒、芯片与抛光垫之间的作用关系示意图

1.2 基于FIB的深宽广沟槽刻蚀技术

利用芯片减薄技术将倒装芯片减薄到约70 μm,为了能从芯片背面进行电路修改,还需要将芯片减薄至几微米的厚度左右。文中主要基于聚焦离子束的深宽广沟槽刻蚀技术来开展进一步的深宽广沟槽刻蚀。

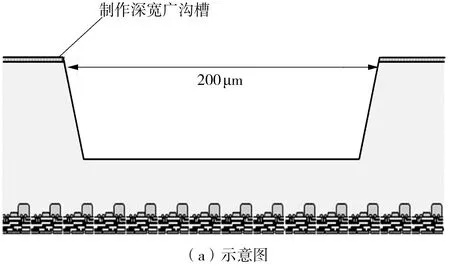

FIB中离子源Ga+的原子量比较大,当荷能离子束轰击样品表面时,能够将固体材料的原子(分子)溅射出表面,这种溅射效应使FIB能利用离子与试片表面的物理撞击与化学反应来带走表面物质,对金属、介质、半导体等材料进行钻孔、切割和剥层等处理。为了提升刻蚀速率或者加强材质的刻蚀选择比,主要采用XeF2辅助气体刻蚀来提升刻蚀深宽广沟槽(如图3所示)速率[12- 14],典型溅射率为0.2 mm3/C时,典型刻蚀增强倍数约为7~12。

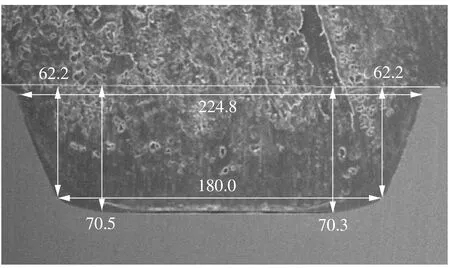

图3 所刻蚀的深宽广沟槽示意图(单位:μm)

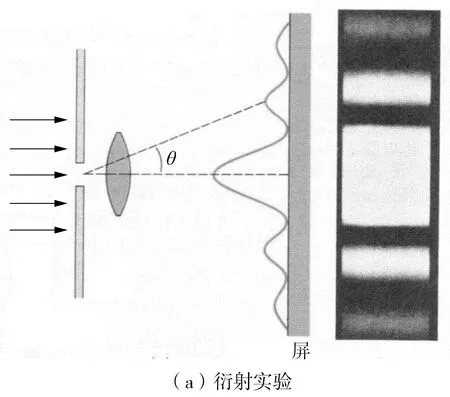

1.3 基于动态光栅衍射条纹的沟槽刻蚀终点监测技术

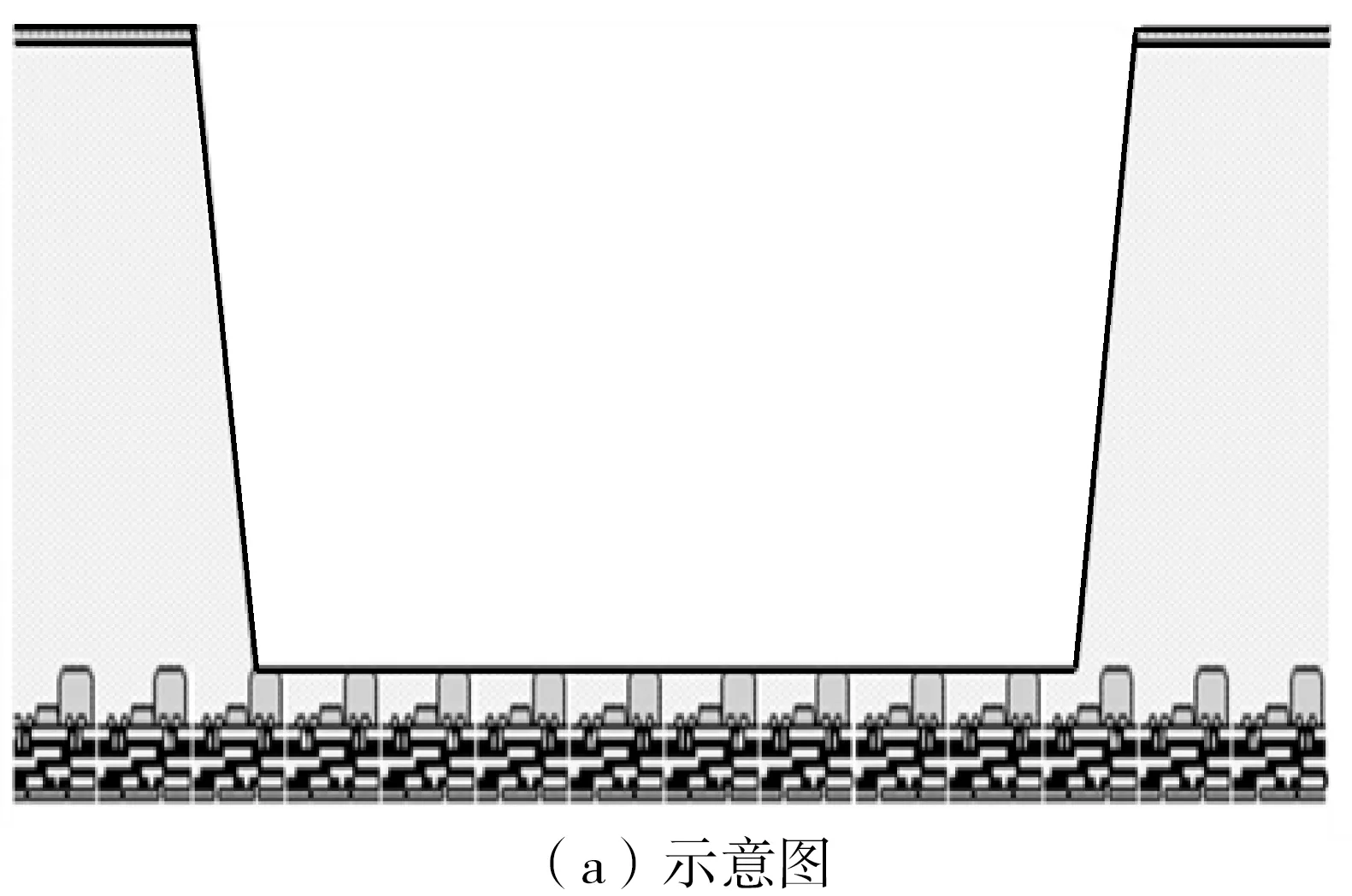

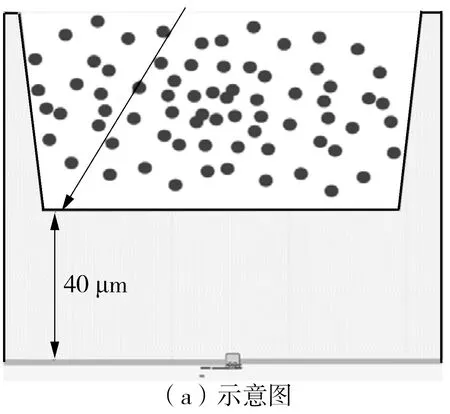

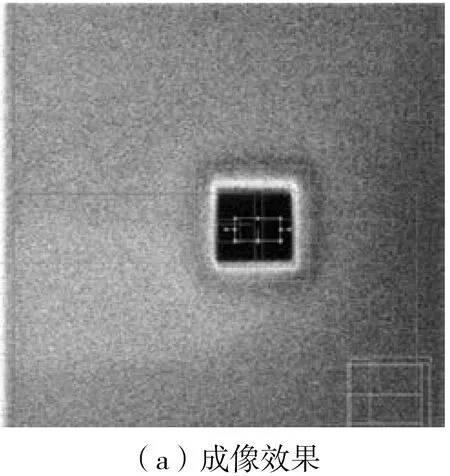

由于硅芯片的背面外观毫无变化,所以利用FIB进行沟槽刻蚀时,无法透过芯片背面直接观察到内部结构。在FIB刻蚀硅芯片形成沟槽时,既要将芯片继续减薄,又需确保不刻蚀过度而损伤芯片内部的电路结构,为解决此问题,文中研究了基于动态光栅衍射条纹的沟槽刻蚀终点监测技术。该技术的原理是:利用光波衍射造成的光程差不同,导致波峰和波谷叠加,使屏上出现明暗相交的条纹,利用该条纹而进行终点监测。依据几何光学,物体上的一个发光点经透镜成像后得到的应是一个几何像点。而由于光的波动性,一个物点经透镜后在像平面上得到的是一个以几何像点为中心的衍斑(见图4)。单缝衍射的明暗位置由缝面上子光源发出光线的衍射角θ来表示,同一衍射角的光线通过透镜汇聚在屏幕上同一位置,并进行相干迭加而形成光的明暗分布,可以通过衍射的明暗条件来确定某级衍射明纹中心或暗纹中心的θ角。当θ角与Δθ(衍射角θ的变化量)趋近于零时,明纹与暗纹皆向中央明纹收缩,以致分辨不清,形成单一明纹,于是衍射消失了,光呈现直线传播。利用硅衬底对红外、近红外光波的穿透性,采用不同波长范围的滤波镜(相当于单缝衍射)进行光波衍射条纹捕捉。硅衬底厚度的不断减薄使所形成的衍射条纹逐渐变得清晰。通过对透过硅衬底成像的衍射条纹的捕捉及分析,来判断深宽广沟槽刻蚀的停止时间。图5是芯片刻蚀到厚度为40 μm时的示意图及芯片的形貌图,结果显示衍射条纹模糊;而图6为芯片刻蚀到厚度为10 μm时的示意图及形貌图,表明衍射条纹更为清晰。

1.4 聚焦离子束电路修改技术

在芯片减薄到足够薄的前提下,透过芯片背面在芯片中选取3个结构清晰、明确的位置作为参考点,并与IC设计布局图资料(GDSII)上的相同位置一一关联,实现将布局图与实际线路重叠并直接关联对准,建立点对点的相应关系及两者的同步关系。通过版图的清晰布线,直接在版图上定位好位置,再通过同步关系对芯片表面也进行相应的定位操作[15- 19]。位置确定好后便可以进行电路修改。文中利用FIB的沉积和切割功能进行电路修改,包括切断多余的金属互连线或搭接缺失的金属互连线。

1.5 基于二次电子讯号的控制切割制样深度的终点监测技术

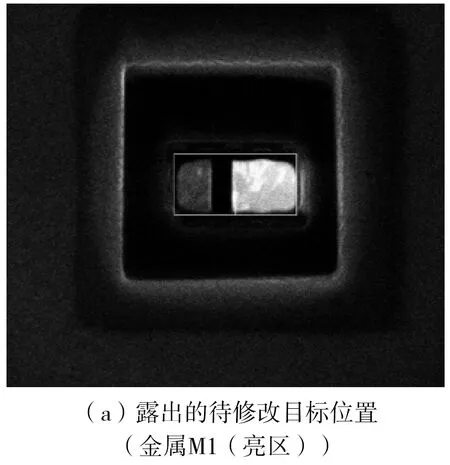

为了确保电路修改时的过程可控,防止切割过度或者沉积不足,基于二次电子讯号法对制样深度进行终点监测。终点监测技术(EPD)的原理为:离子束成像为二次离子像,离子束在被测芯片表面扫描,接收到的二次离子的数量与芯片表面的结构有关。导电部位(如金属)发出大量的二次离子,该区显示为亮区;非导电部位则显示为暗区。通过二次电子像的对比来判断离子束所作用的对象是金属或是其他材质。

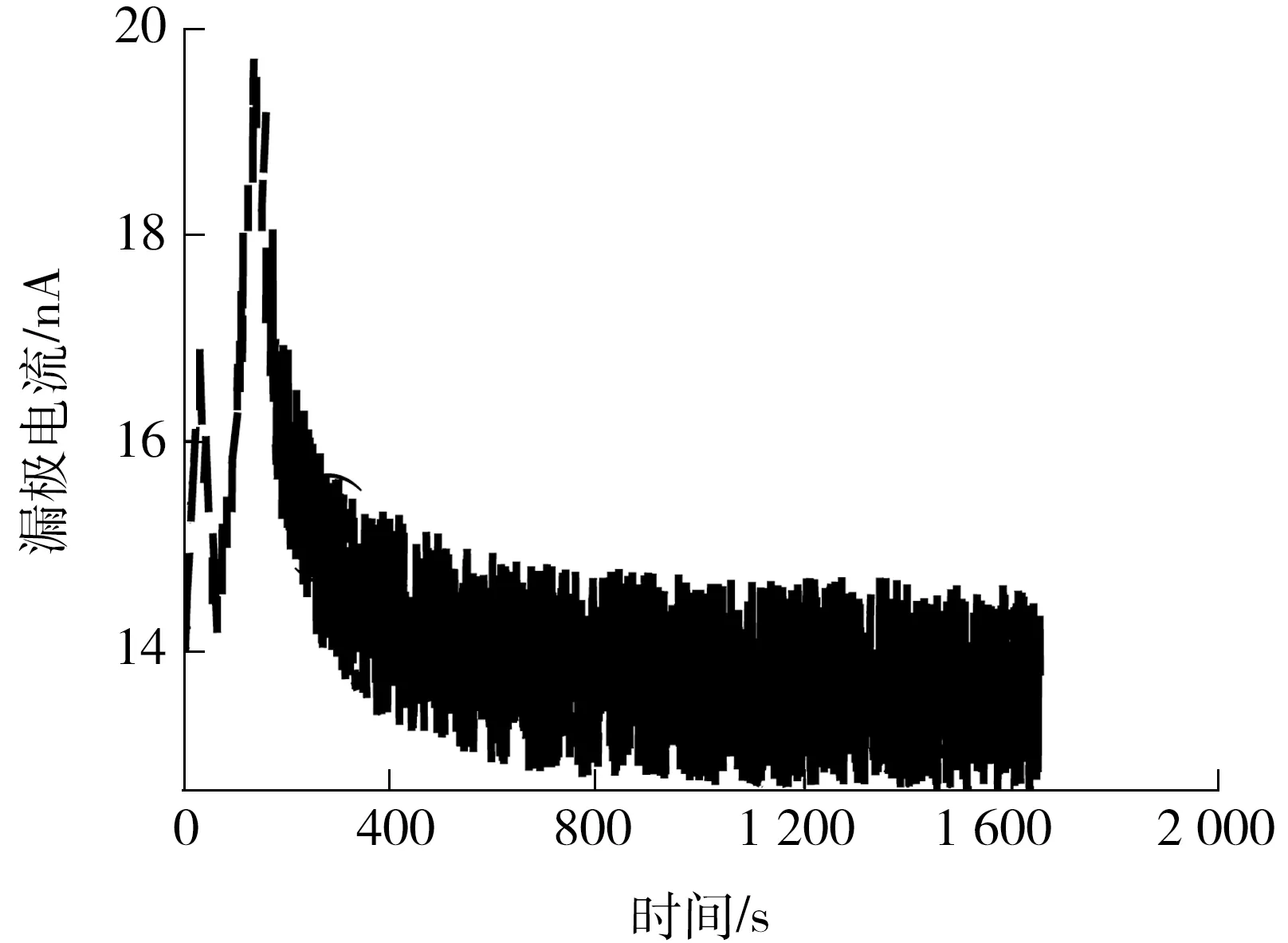

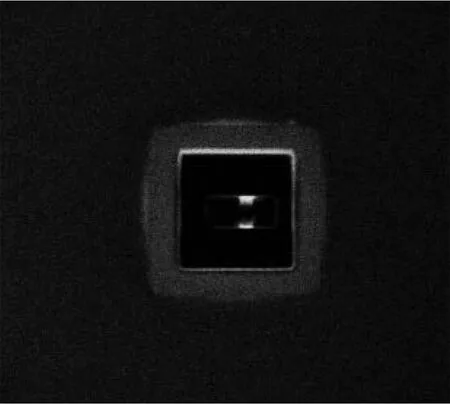

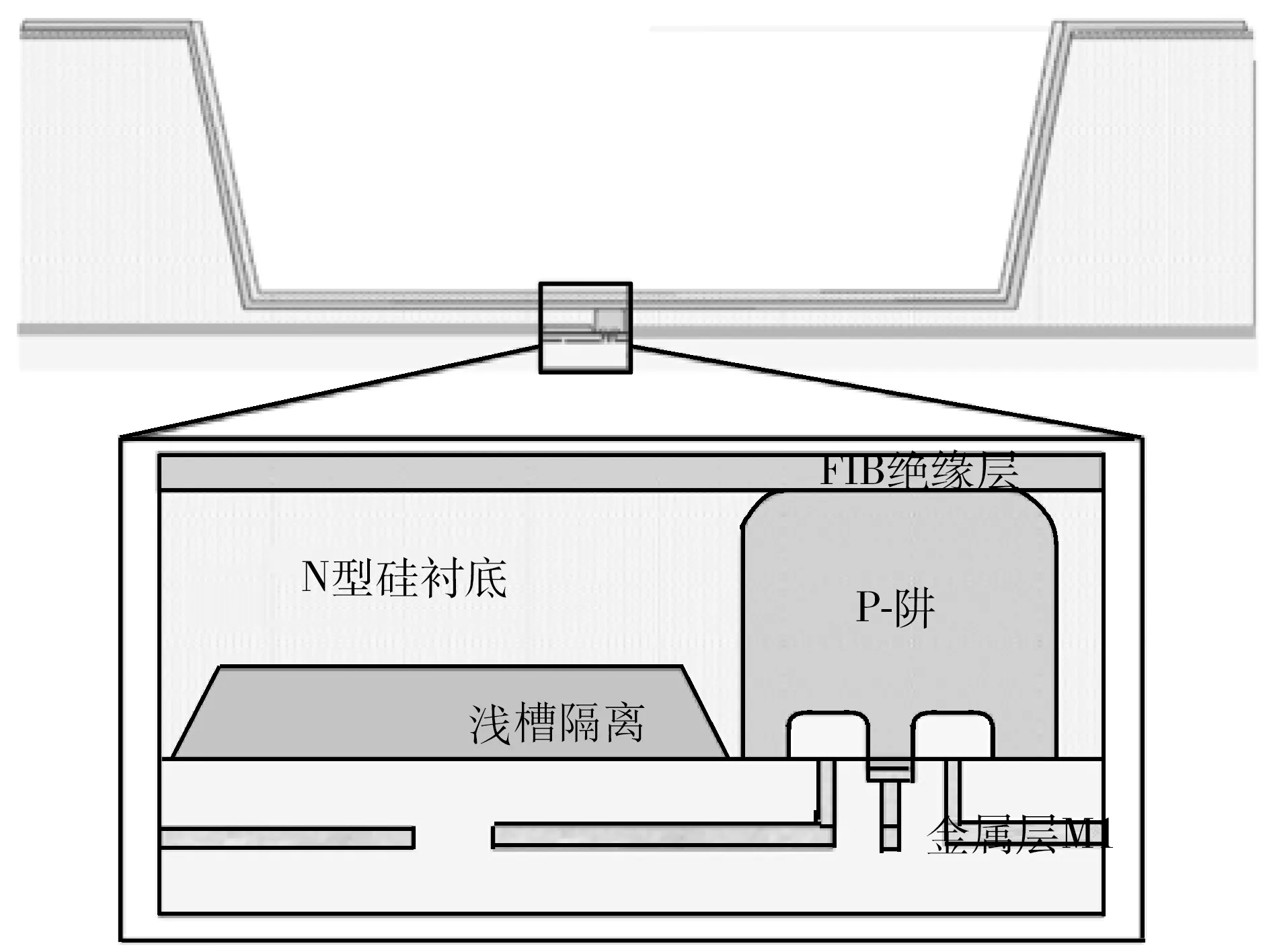

在某种材料被刻蚀的过程中,经过不同材料的边界时,因材料的差异会产生不等量的二次电子讯号,收集此材料表面所发出的电流,通过监测讯号的强弱变化来监测刻蚀深度,控制切割动作至所要求的电路层并停止。经研究,刻蚀到导电材料时,产生的二次电子讯号电流比较大;而当刻蚀到的是介质材料时,产生的二次电子讯号电流比较小。在两者之间的交界处,则会产生电流的跳变。如图7所示,EPD监测到电流突然向上跳变,意味着从导电材料刻蚀到了导电性能较弱的材料了。图8为二次离子图像显示的电压衬度像中金属M1由暗变亮,意味着浅槽隔离(STI)及介质层已经去除完毕,暴露出M1;而图9所示则是EPD监测到电流突然向下跳变,意味着从导电材料刻蚀到了导电性较弱的材料了。电压衬度像中金属M1由亮变暗,意味着切割完成(见图10)。

图7 刻蚀到金属层后电流的变化Fig.7 Change of current when the metal layer is etched

图8 STI及介质层去除完毕、暴露出M1时的电压衬度像

图9 刻蚀到导电性能较弱的层时的电流变化

图10 切割完成时金属M1层的电压衬度像

2 实验验证

实验样品为0.13 μm CMOS工艺的6层金属芯片。芯片尺寸是2.4 mm×2.4 mm,芯片原始厚度为300 μm,金属为Cu,共6层。芯片的底层金属M1中有一个MOS管漏极开路需要修改。由于M1在最底层,如果从芯片正面进行修改,将需要穿过M2-M6,成功率极低,所以采用背面电路修改技术进行电路修改。文中对漏极开路的MOS管进行线路连接。

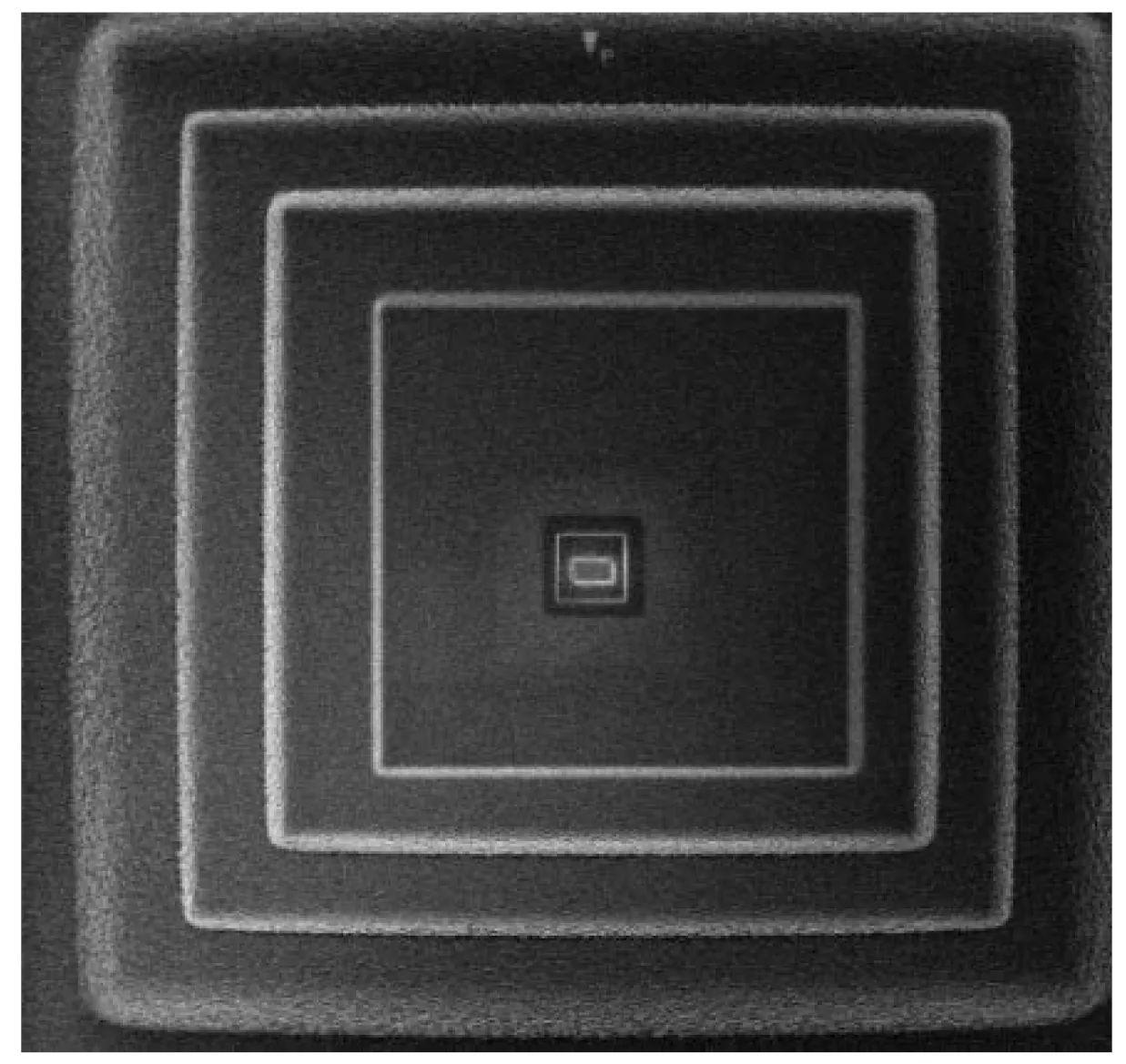

根据问题MOS管的位置,经版图分析排查,确定了需要修改的位置。Cut_M1:1 635.81 μm,1 349.86 μm;Connect_M1:301.55 μm,1 374.24 μm。拟修改的部位如图11所示,目标修改位置至芯片背面沟槽底部的结构示意图如图12所示。利用芯片薄化技术将芯片减薄至70 μm左右;用不同的束流制作不同深宽沟槽,进一步减薄芯片,同时用不同波长的滤镜观察芯片背面的光斑干涉条纹情况,以精确监测芯片减薄的进展情况。

图11 芯片中需要连接的MOS管(漏极开路)

图12 目标修改位置至芯片背面沟槽底部的剖面示意图

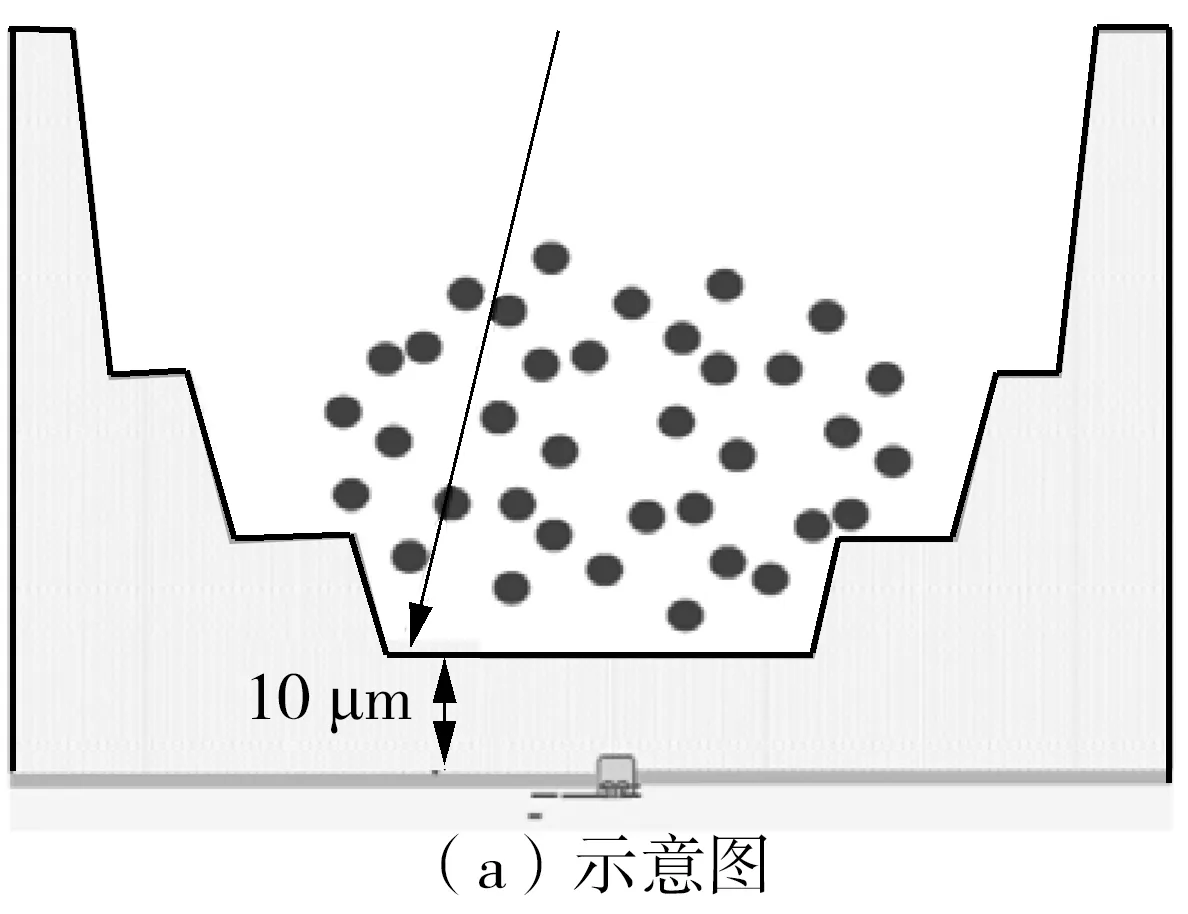

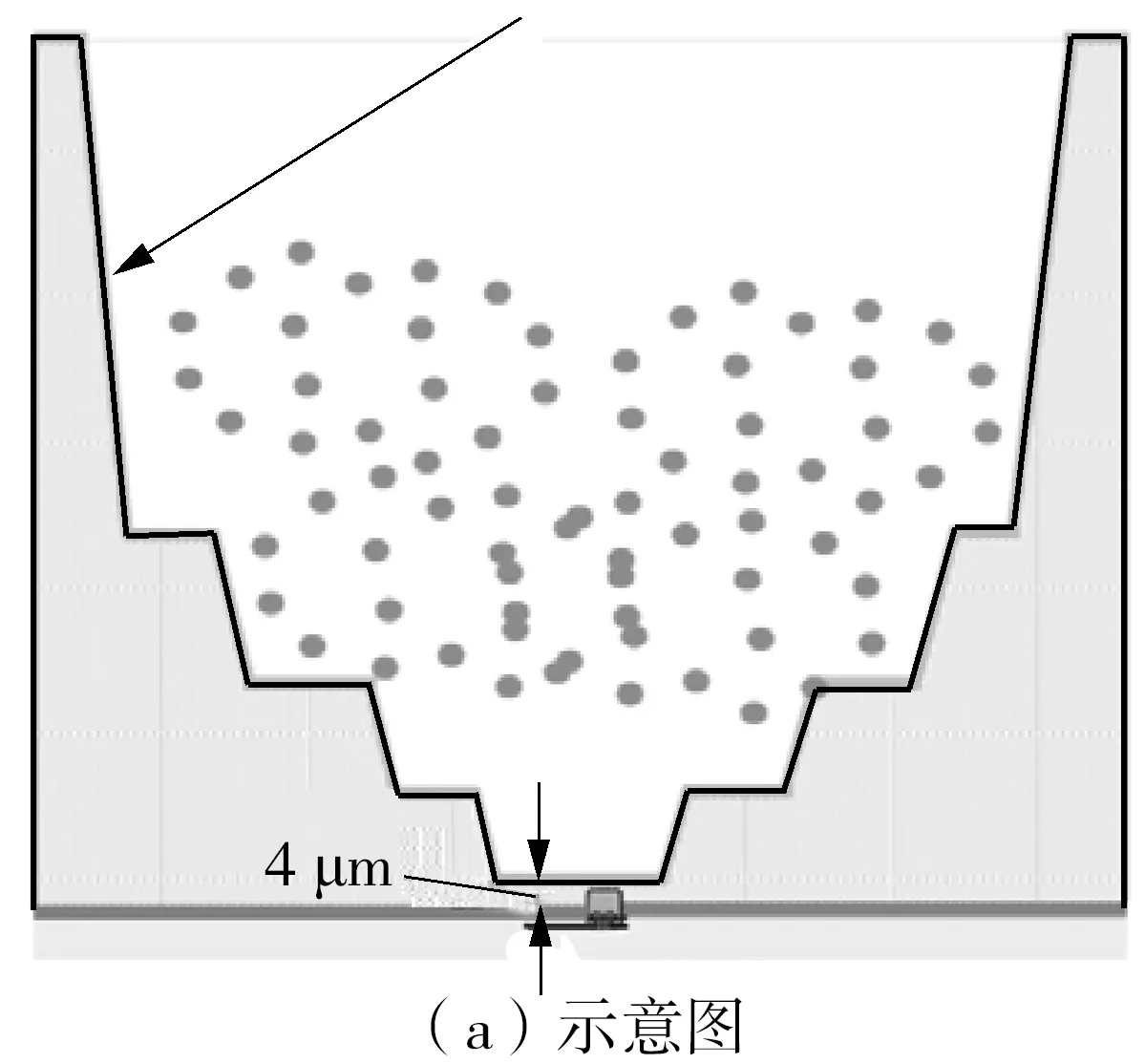

首先用高束流XeF2、20 nA的FIB束流进行40 min的刻蚀,制作200 μm ×200 μm的沟槽,使芯片厚度约剩40 μm(滤镜波长=1 000 nm),如图13所示。接着,用普通束流XeF2、6 nA的束流进行4 min的刻蚀,制作125 μm×125 μm的沟槽,芯片厚度约剩10 μm(滤镜波长=850 nm),如图14所示。

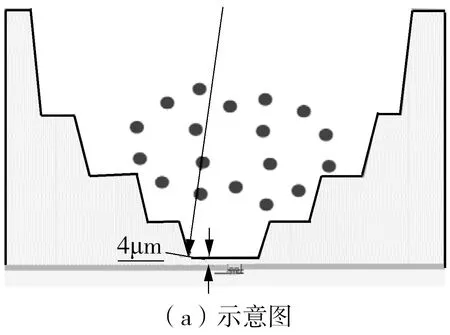

用普通束流XeF2、6 nA的束流进行2 min的刻蚀,制作75 μm×75 μm的沟槽,芯片厚度约剩4 μm(滤镜波长=700 nm),此时已经观察到较为明显的衍射条纹,停止刻蚀,如图15所示。

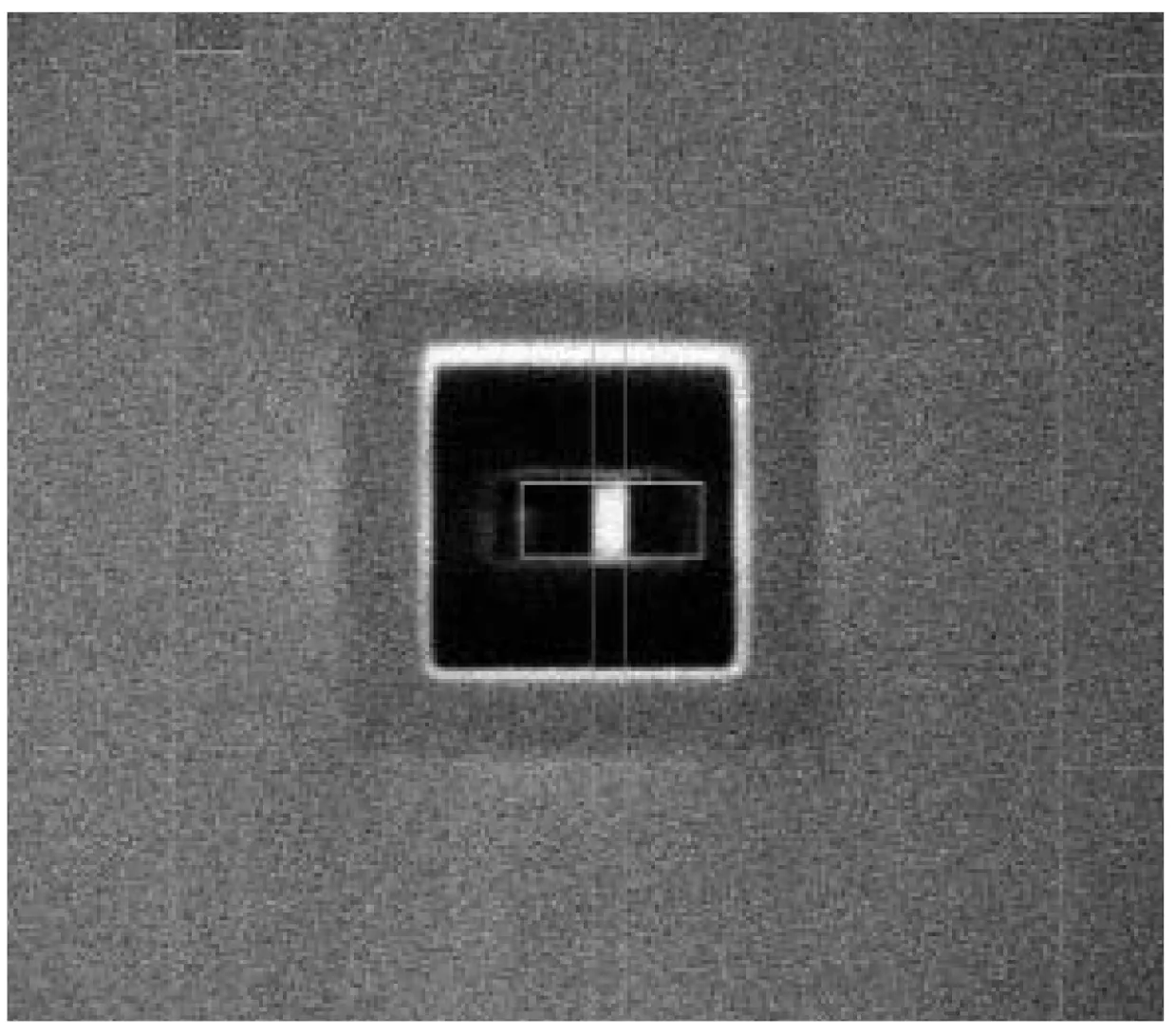

当目标位置确定完了之后,需要首先淀积一层STI以保护硅槽的侧壁。此处,用4 nA、6 kV的束流淀积一层保护层,如图16所示。

结合芯片的GDS版图文件,将芯片的版图与芯片表面成像重叠关联,并结合目标位置的版图文件信息,确认目标位置下方(即目标位置与芯片背面之间)的电路结构,如硅衬底、STI、介质层等。同时利用束流大小为1 nA的FIB制作10 μm×10 μm的沟槽,以去除目标修改部位上方的STI材质,露出目标修改位置(见图17)。再利用束流大小为1 nA的FIB在已刻沟槽上淀积一层保护层(12 μm×12 μm),保护STI侧壁(见图18)。用束流为250 pA的FIB,结合XeF2,制作大小为6 μm×3 μm的区间,露出待修改的金属M1中开路部位。

图18 为了保护STI侧壁在沟槽上淀积的一层保护层

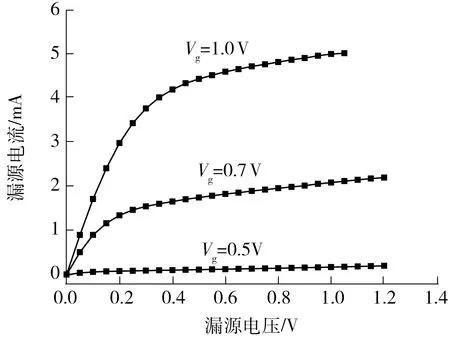

将版图文件与芯片关联(见图19),采用Pt作为淀积材料,束流大小为250 pA,制作连接金属M1(301.55 μm,1 374.24 μm),连接区域大小为6 μm×3 μm,如图20所示。电路修改连接完成后的FIB图像如图21所示。MOS管漏极开路部位经电路修改连接后,测得了正常的电流-电压曲线,如图22所示,从而验证了背面电路修改的有效性。其中,Vg为栅极电压。

图21 电路修改连接完成后的FIB图像

图22 MOS管漏极开路部位连接后测得的输出特性曲线

由本案例的实施过程可以看出,背面FIB电路修改技术是在传统的正面FIB电路修改技术基础上,融入创新的芯片背面减薄技术及基于动态光栅衍射条纹的沟槽刻蚀终点监测技术,通过全局抛光减薄法,由大到小将多种FIB束流刻蚀相结合,以减薄硅衬底,使其逐渐减薄至能够从芯片背面进行观察的厚度,使人们能够从外观毫无变化的硅芯片的背面入手对晶体管层级的金属互连线进行电路修改,成功解决了倒装芯片正面朝下、电路置于芯片下方,无法直接从芯片正面入手去进行电路修改的难题。

3 结论

文中结合芯片背面减薄技术、基于FIB的深宽广沟槽刻蚀技术、基于动态光栅衍射条纹的沟槽刻蚀终点监测技术、聚焦离子束电路修改技术,实现了倒装芯片/多层互连结构封装集成电路的电路修改。实验结果表明,该方法可以有效地实现倒装芯片/多层互连结构封装集成电路中开路或者短路的电路修改,为电路设计验证提供了技术手段。三维多芯片叠层封装集成电路的出现对FIB电路修改技术又提出了新的挑战,将是下一步的研发重点。