小数分频锁相环杂散抑制技术研究和应用

冯跃辉

(中国电子科技集团公司第七研究所 广东省广州市 510310)

1 概述

随着无线通信系统的发展,宽频段和高跳速成为软件无线电发展的主要方向,这对频率合成器的无杂散频率覆盖、锁定时间、功耗等提出了更苛刻的需求。小数分频锁相环可以在不改变参考时钟频率的前提下,增加输出信号频率范围和分辨率,在对频率步进和噪声水平要求较高的应用中可以大大简化系统设计。小数杂散是小数分频锁相环应用中的主要问题,有用信号频带内的杂散会直接影响接收机灵敏度和发射机杂散性能。

本文在详细分析小数环杂散产生机理的基础上,提出了一种宽频段覆盖、快速频率切换的杂散抑制方法,并设计了硬件电路和杂散抑制算法,经实测验证达到了良好的实用效果。

2 实现原理

2.1 小数环工作原理

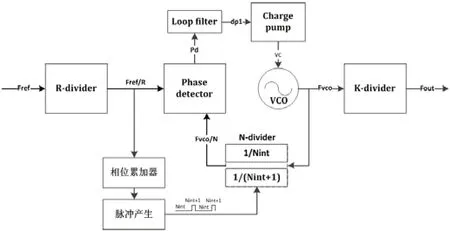

小数环功能框图如图1 所示。参考时钟Fref 经R 分频器后,产生鉴相器参考信号Fpd=Fref/R,VCO 输出信号经N 分频器后产生鉴相器输入信号Fp=Fvco/N,鉴相器输出Fpf 和Fp 的累加相位差Pd,Pd 经环路滤波后驱动电荷泵产生VCO 控制电压vc,VCO 在控制电压vc 的驱动下调整输出频率直至F1=F2。当环路锁定时,Pd 为0,锁相环输出频率Fout 和参考时钟Fref 关系为Fout×K/N=Fref/R。小数锁相环的N 由整数部分和小数部分组成,即N=Ninteger+Nfractional。

N 分频器由双模整数分频器、相位累加器和脉冲扣除电路组成。分频值为N=Nint+Frac,Nint 为整数部分,Nfrac=Num/Den 为小数部分,其中Num 为小数分子,Den 为小数部分分母。小数分频器的实现过程如下。N 分频器构建一个Nint 分频器和Nint+1 分频器。初始状态时,分频器工作在Nint分频器状态下,相位累加器的值为0。然后每个鉴相周期Tpd 将累加器的值与Num/Den 做一次累加,当累加器溢出时产生一个持续时间为Tpd 的脉冲,此脉冲被用作双模整数分频器的切换开关。这样在前Den-num 个鉴相周期内NCO 输出的频率为Fvco=Fpd*Nint,在后Num 个鉴相周期内NCO 输出的频率为Fvco=Fpd*(Nint+1),在Den 个鉴相周期内VCO 输出的平均频率为Fvco=Fpd*(Nint+Num/Den)=Fpd*N。

2.2 小数分频锁相环的杂散

小数环的杂散主要包括参考杂散和小数杂散。参考杂散是锁相环中最常见的杂散信号。参考杂散是由于电荷泵的UP/DOWN 电流失配造成的。当锁相环接近锁定状态的时候,鉴相器输入两个频率非常相近的时钟信号,输出的电流脉冲Icp 时间很短,可能会无法打开电荷泵而进入死区。可以通过在复位电路中加入延时单元来避免进入死区,但这导致锁相环在锁定状态下会产生宽度相同的UP和DOWN 电流脉冲。如果电荷泵的UP 和DOWN 电流完全匹配则不会有杂散输出。但实际上由于模拟器件的差异性,UP 和DOWN电流无法完全匹配,从而导致锁相环在锁定状态下,电荷泵产生与鉴相频率相同的交替变换的正负脉冲。这些脉冲通过环路滤波器后调制VCO 产生分布在鉴相频率Fpd 和其谐波N*Fpd 上的杂散[1]。

小数杂散又叫整数边界杂散,是小数环特有的杂散。小数杂散的产生是锁相环VCO 频率和参考频率小数倍校准的结果。由小数环的工作原理可知,当脉冲产生电路进行脉冲扣除时,VCO 输出频率会在脉冲边沿前后产生相差,这个相差会随周期积累,在脉冲扣除时减小,在Den 个周期中扣除Num 个脉冲时清零,然后继续积累。这种相位累积会在鉴相器输出端产生周期性的阶梯电压波形,这个阶梯波形通过滤波器阻抗响应,驱动电荷泵输出,最终在VCO 中调制输出,形成杂散。因为这种杂散周期是鉴相周期的Den 倍,分布在较低频率的位置上,环路滤波器对其抑制效果十分有限。如果进一步减小环路滤波器带宽对其进行抑制,会明显牺牲锁相环锁定时间,而对于近端杂散并没有抑制效果。环路锁定时间如下公式(1)所示,式中BW 为环路滤波带宽,ftol为可以容忍的频率误差,fjump为频率跳变量[2]。

由以上原理可知,小数杂散分布以Fpd/Den 为单位,与小数分频器的分子Num 相关。分频器为整数(Num=0)时杂散能量为零;在整数边界处,杂散强度最大;在远离整数边界处,杂散强度减小。小数杂散具体分布规律如下。

(1)一阶杂散。最大杂散为Fpd*(1/Den)和Fpd*((Den-1)/Den);次大杂散为Fpd*( [DEN/2]/Den) 和Fpd*((DEN- [DEN/2])/Den);第三大杂散为Fpd*( [DEN/3]/Den)和Fpd*((DEN- [DEN/3])/Den);依次类推,杂散强度依次减小。如果DEN /M 正好为整数,则此处杂散为0。([]为向下取整运算符)

(2)二阶杂散。最大杂散为Fpd*(2/Den)和Fpd*((Den-2)/Den)。

(3)n 阶 杂 散。最 大 杂 散 为Fpd*(n/Den) 和Fpd*((Den-n)/Den)。

图1:小数环功能框图

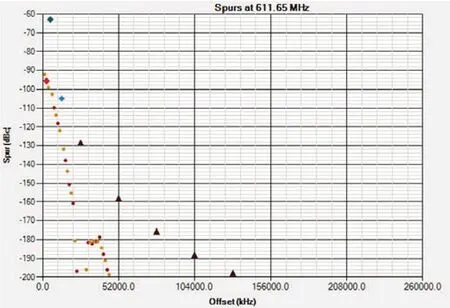

图2:LMX2571 杂散分布示意图

低阶杂散分布比较靠近载波频率,并且能量相对较大,特别是一阶杂散中的最大杂散幅度往往在-70dBc 以上,必须予以消除。图2 是TI 的低功耗小数锁相环LMX2571 工作在Fpd=Fosc=26MHz,Fvco=4893.2MHz,Fout=611.65MHz时的杂散分布图。图中黑色三角表示参考杂散,红色圆点表示小数杂散。由测试结果可知其杂散基本符合上述分布规律。

调整分频器N 的值,使其在整数边界附近变化,可发现明显的杂散分布变化。如图3 所示,左图是Nfrac=0 时的杂散分布,中间图是Nfrac=0.0027 时的杂散分布,右图是Nfrac=0.27 时的杂散分布。可以看到N 值在边界附近的调整对杂散影响巨大。

2.3 小数环杂散的消除

参考杂散以鉴相频率为间隔分布,可以通过提高鉴相频率,使得参考杂散落在环路带宽以外,然后用环路滤波器予以消除。相比整数环,小数环可以使用更高的工作鉴相频率,所以参考杂散一般都能很好的得到抑制。

小数杂散是小数环特有的杂散,小数环本身无法消除。由小数环杂散分布特性可知,可以通过选取适当的小数环参数,使小数分频器N 的小数分量避开整数边界,从而达到杂散规避的目的。下面将讨论一种满足宽频段和快速频率切换特性的小数环杂散消除方法。

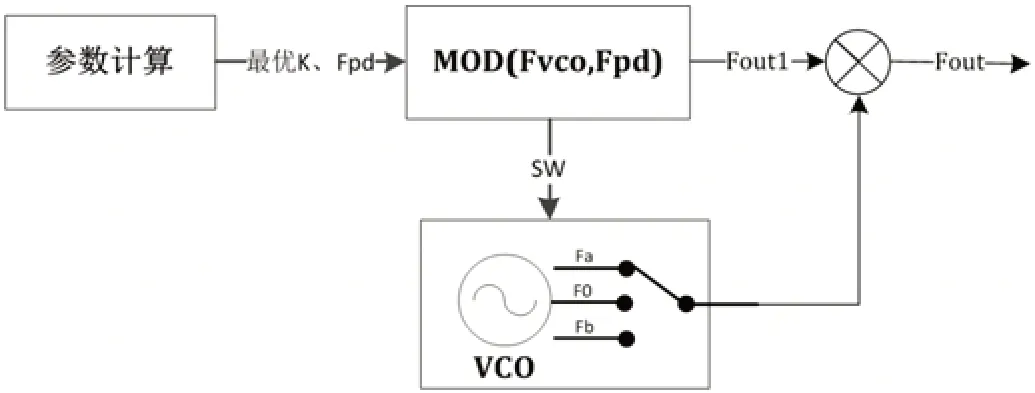

本设计由参数计算模块、杂散判决模块和频率补偿模块三部分组成。功能框图如图4 所示。

参数计算模块根据所需频率计算出最优的K 和Fpd 等锁相环参数,使得每套所选参数能够覆盖最大的无杂散频率范围输出。杂散判决模块通过计算Fvco 和Fpd 的模值,判断Fvco 是否位于整数边界范围之内,如果位于边界之内则对Fvco 进行修正,如果位于整数上边界之内则进行正修正,如果位于整数下边界之内则进行负修正。后级的频率补偿模块,根据杂散分布位置对修正过的Fout进行反向补偿。频率补偿模块由工作在F0、Fa 和Fb 频率下的频率源和切换开关组成,其中Fa-Fo=Fo-Fb=ΔF。处理流程如下。

图3:边界杂散变化示意图

图4:小数杂散处理功能框图

图5:杂散抑制效果

(1)参数计算模块根据所需要的频率Fout,选取最优的K值。选取的原则是Fvco=Fout/K 应在VCO 输出范围之内,如果有多个K 值满足条件则计算每个K 值下Fvco 与鉴相频率Fpd 的余数M(K),选择其中与整数偏差最大的值M(K1),对应的K 值作为优选参数K1,对应的VCO 频率为Fvco1。

(2)根据信道带宽选取合适的保护间隔PB,在载波频率±PB范围内要避免超过允许幅度的杂散干扰。若M(K1)

(3)频率补偿模块根据杂散边界类型对Fout1 进行补偿来消除ΔF 偏差。最终得到无杂散输出Fout。

3 验证效果和结论

按上述方法设计杂散抑制电路,并在FPGA 中对杂散消除算法进行设计,经测试验证在20MHz~1300MHz 范围内的杂散抑制在达到-70dBc 以下。其中一个示例频点的杂散抑制效果如图5 所示。左图中显现在偏离载波400KHz 和-400KHz 处出现幅度为-59dBc的小数杂散,右图为经杂散抑制之后400KHz 处的小数杂散完全消除,载波频率左右1M 范围内没有杂散分布。

频率补偿模块会引入额外的锁定时间,解决方法是选取跨度较小的补偿频率。例如选取ΔF=2MHz 时,在满足杂散抑制要求的前提下,整个电路的换频时间在10us 以内。

4 小结

小数锁相环的杂散会对射频指标产生严重影响,本文讨论了一种适合宽频带、快速频率切换应用的小数环杂散抑制方法,经验证杂散得到明显抑制。