基于FPGA的图像疵点处理设计与实现

文/吴海游 孙艳娜 左弟俊

1 引言

现场可编程逻辑器件(Field Programmable Gate Array ,FPGA)具有显著的灵活性和可再编写性等独特的技术优势。目前,基于计算机软件的图像处理理论与后处理技术已经非常成熟,但其不利于系统的实时化。相比于图像采集的后处理、FPGA 不但能够对图像进行实时处理、还能减小数据上传压力,具有非常重大的意义。

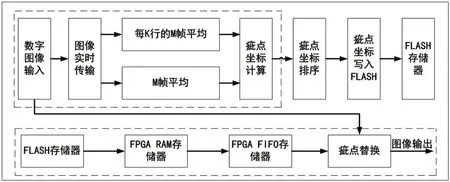

图1:成像系统疵点处理原理框图

在成像与跟踪识别系统中,过多疵点不仅严重影响成像系统的成像质量,而且还会引起对有效目标的错误跟踪与识别,因此非常有必要对图像的疵点进行处理。传统方法是计算机软件处理图像疵点,整个过程需要开发计算机软件,增加额外的数字图像采集设备,而且该方法不适用于模拟成像系统。因此本文提出一种利用FPGA 在线处理疵点的方法,主要包括子图划分、疵点坐标分时计算、排序与存储、疵点流水线补偿等过程。

2 原理设计

在成像系统中,针对不同的需求,图像疵点判断标准有细微的差别。但其主要思想和依据为:强光照条件下,将灰度偏离图像平均灰度X1 的像素判定为疵点,在无光条件下,灰度高于平均灰度X2 的像素判定为疵点。一般来说,采用二维平面坐标系来表示每个像素在图像中的位置,即(x,y)来表示每个像素的位置。

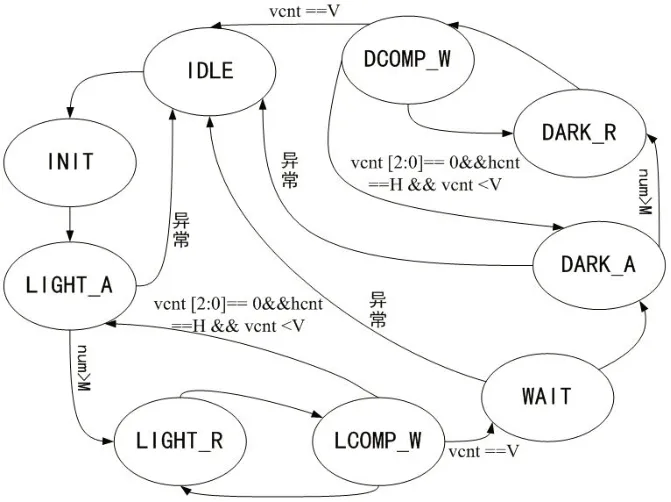

图2:疵点坐标计算状态转换图

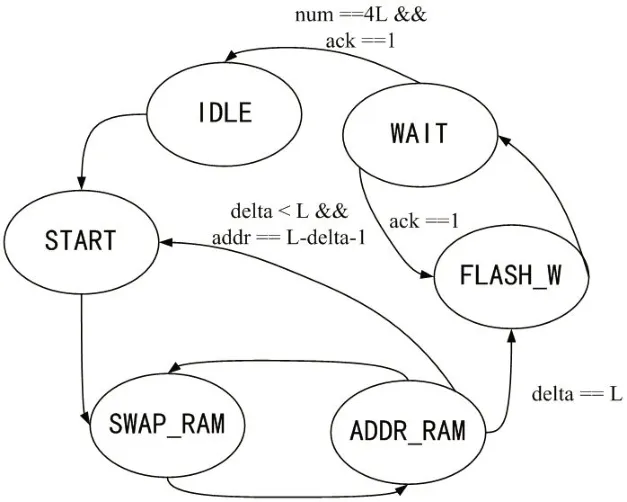

图3:疵点坐标排序与存储状态转换图

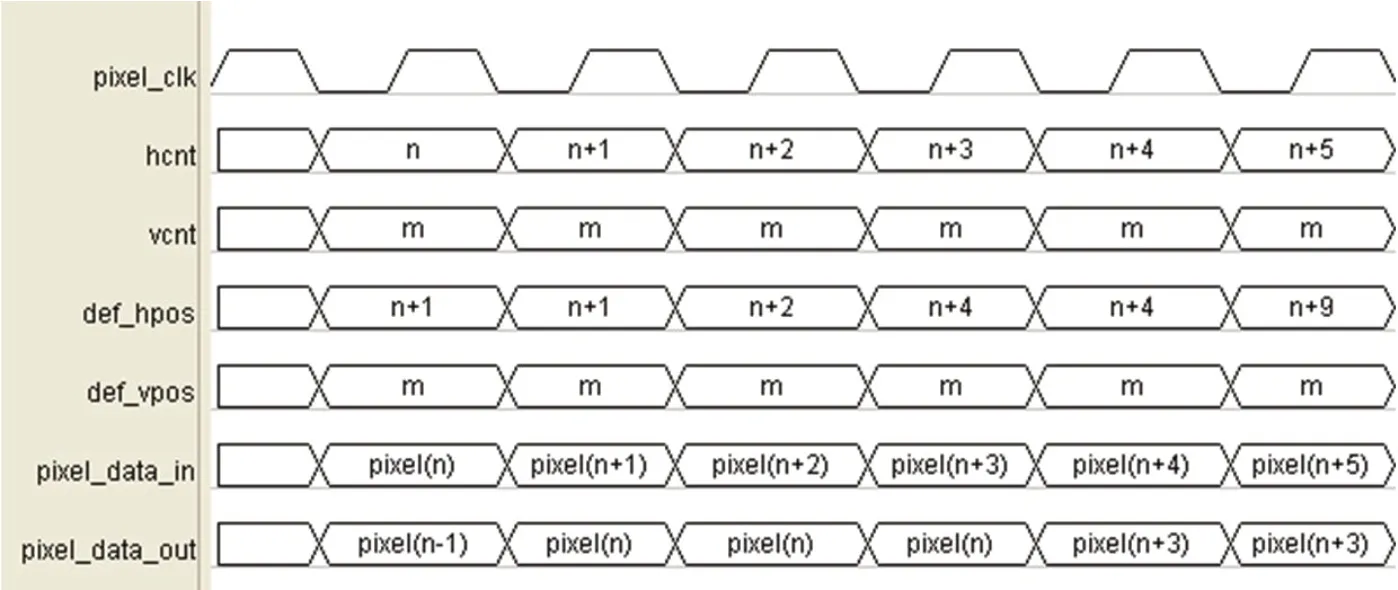

图4:图像疵点补偿时序图

相对于计算机,FPGA 存储资源有效,无法完整存储一幅及以上的高分辨率图像数据,因此将分辨率为H x V 的图像划分为V/K 个子图。每次计算出K 行图像的疵点坐标值并存储至FPGA 片上的RAM1 中,直至计算出整幅图像的疵点坐标。然后将疵点坐标顺序存储至RAM2 中,最后将所有疵点坐标再存储至FLASH 中,此时完成图像疵点坐标的计算、排序与存储。成像系统每次上电启动时,将FLASH 中存储的疵点坐标顺序读取至FPGA片上的RAM3 中,然后对图像进行实时处理,其原理框图如图1所示。

3 具体实现

3.1 疵点坐标计算

在疵点计算时,当接收到疵点计算触发开始指令后,将第一帧图像的前K 行数据依次写入RAM1 内。当第2 帧图像的前K 行到来时,依次读出RAM1 中的数据加上第2 帧图像对应位置的像素灰度,并存储至RAM1中,依次类推直至接收完M 帧图像。本设计采用三段式同步有限状态机来完成,其状态转移图如图2所示,主要包括以下9 个状态:

(1)空闲状态(IDLE):若疵点计算开始信号到来,则状态转移至INIT 状态。

(2)初始化状态(INIT):初始化完成后进入LIGHT_A 状态。

(3)计算亮场平均灰度(LIGHT_A):使成像系统置于强光条件下,计算图像平均灰度,状态转移至LIGHT_R 状态。

(4)读出亮场平均灰度(LIGHT_R):生成RAM1 的读使能、读地址信号,同时状态转移至LCOMP_W 状态。

(5)亮场疵点坐标写入RAM(LCOMP_W):若vcnt ==V,则状态转移至WAIT 状态。

(6)等待(WAIT):若暗场疵点计算开始信号到来,则状态转移至DARK_A 状态。

(7)计算暗场场平均灰度(DARK_A):使成像系统置于无光条件下,计算图像平均灰度,状态转移至DARK_R 状态。

(8)读出暗场平均灰度(DARK_R):生成RAM1 的读使能、读地址信号,同时状态转移至DCOMP_W 状态。

(9)暗场疵点坐标写入RAM(DCOMP_W):若vcnt ==V,则状态转移至IDLE 状态,此时疵点坐标信息计算完成。

3.2 疵点坐标排序与存储

当疵点计算完成后,需要对疵点坐标信息按从小到大的顺序进行排序,本设计中采用基于FPGA 的冒泡排序法对疵点坐标信息进行排序,同样采用三段式同步有限状态机来完成。其状态转移图如图3所示,主要包括以下6 个状态:

(1)空闲状态(IDLE):若疵点计算完成信号到来,则状态转移至START 状态。

(2)起始状态(START):初始化RAM2的读地址。

(3)比较后交换写入RAM(SWAP_RAM):比 较RAM2 地 址addr 与addr+1 空间内的数据data0 与data1,同时状态转移至ADDR_RAM 状态。

(4)RAM 读地址(ADDR_RAM):读地址addr 加1,若RAM2 读地址等于L-delta-1,状态转移至START 状态;若delta 等于L,状态转移至FLASH_W 状态;否则转移至SWAP_RAM 状态。

(5)FLASH 写 入(FLASH_W):将RAM2 中的数据分包写入FLASH 中,同时状态转移至WAIT。

(6)等待(WAIT):若RAM2 中数据全部写入FLASH,则进入IDLE 状态。

3.3 图像疵点实时补偿

在实时成像系统中采用流水线操作对疵点像素进行处理。本设计中采用左替换的方法补偿疵点像素,即若坐标位置为(i,j)处像素是疵点像素,则利用坐标(i,j-1)处像素替换该疵点像素,若(i,j-1)也为疵点像素,则利用(i,j-2)处像素替换,依次类推。其操作过程如图4所示。

4 硬件平台验证

本设计的硬件平台主要由ALTERA公司的FPGA 芯片5CEBA4U15I7 和On Semiconductor 公司的图像传感器芯片NOIP1SN1300A 构成。疵点图像得到了有效地补偿处理,从而验证了设计的正确性。

5 结束语

本设计提出关于图像疵点坐标计算、存储与处理设计方法,能够很好地解决图像疵点对成像系统的不良影响,并且此设计在硬件平台上得到充分验证,可靠性高。