数字时钟相位检测在时间同步上的应用

黄华明

(上海诺基亚贝尔股份有限公司,上海 201206)

目前,5G 前传系统中的高精确时钟同步架构通常是由ASIC芯片结合FPGA 实现的,ASIC 芯片利用其专用硬件特性处理时间戳,FPGA 利用其协议修改的灵活性实现PTP 的算法加速和ToD 协议处理等功能。在ASIC 或FPGA 中,各自都需要有一个基准的时间计数器,他们基于各自的时间计数器完成自己内部的各项处理功能。如果要满足目前IEEE 对时间同步系统性能的高精度要求,这两个分别位于ASIC 和FPGA 内时间计数器必须要达到非常高的时间同步精度。

本文描述的方法是通过数字电路实现二个时钟的相位差高精度检测,这里就是对ASIC 和FPGA 的工作时钟进行相位检测。当ASIC 和FPGA 内时间计数器通过数字方法实现初步同步后,再通过高精度检测的时钟相位差值,对初步同步后的时间计数器进行高精度二次矫正,使得仅通过数字设计方法即可将位于不同芯片内的二个时间计数器的同步达到亚纳秒精度。

1 DDMTD 工作原理

DDMTD 是数字化的DMTD(双混频器时差测量法),DDMTD 可以测量具有相同标称频率的两个时钟信号的相位差。使用公共偏移时钟clkddmtd,DDMTD 先执行公共偏移时钟和两个输入时钟的混频,再经过低通滤波之后,所得到的信号可用于估计两个时钟信号之间的相位差。

在DDMTD 中,使用D 触发器实现时钟信号混频及低通滤波,实现电路如下:

图1 DDMTD实现电路

我们可以通过测量图1中低频时钟clk1ddmtd和clk2ddmtd的相位差δtclkddmtd来计算出输入时钟clk1和clk2之间的相位差。具体计算推导可见参考文献。

电路中cntddmtd 计数的基本原理是:当时钟clkddmtd检测到clk1ddmtd上升沿时,将cntddmtd计数器清零。当时钟clkddmtd 检测到clk2ddmtd上升沿时,输出计数器cntddmtd的当前值m。也即可得到在clk2ddmtd上升沿时刻,此时输入时钟clk1和clk2之间的相位差。因为cntddmtd计数器每次是在检测到clk2ddmtd上升沿时输出,所以cntddmtd计数器输出更新的周期与clk2ddmtd时钟周期一致,为1/fbeat。即电路对输入时钟相位差检测的周期为1/fbeat,因为clk1和clk2具有稳定的相位弧度差Φ,所以每个测量周期输出的测量值基本为一个固定值,通过该固定值可以计算出输入时钟clk1和clk2的相位差。

此方法优点是利用数字方法检测两个同频时钟的相位,从后端仿真和实际应用情况看,精确度非常高,可控制在亚纳秒级以内的测量误差。

2 基于DDMTD 测量和高精度补偿的实现方法。

本文关注的重点是如何在当前设计的基础上,增加DDMTD数字高精度时钟相位检测技术,对数字时间戳计数器进行高精度的二次矫正。使用简单的低成本的数字逻辑设计方案即可实现高精度的时间同步。

2.1 当前设计

图2 当前同步设计方案(不包括蓝色方框模块)

如图2所示,设计的目标是将ASIC 内的时间计数器asic_cnt和FPGA 内的时间计数器fpga_cnt 同步起来,并且有同步精度的性能要求。为描述方便,下面所述二个时间计数器即指asic_cnt和fpga_cnt。

图中ASIC 为商用芯片,FPGA 为我们设计所使用的现场可编程逻辑阵列芯片。

时钟clk1和时钟clk2源自相同的参考时钟源,所以clk1和clk2具有相同的时钟频率。但由于clk1和clk2在设计版图上的走线长度不同,以及进入ASIC 和FPGA 芯片内部的走线延迟不同,最终导致驱动二个时间计数器的时钟源会有个固定的相位差,并且不同的FPGA 实现版本和环境温度等条件的变化,驱动二个时间计数器时钟源的固定的相位差也会发生变化。但驱动这二个时间计数器的时钟源频率是一致的,也就是说二个时间计数器前进的步伐是一致的。

ASIC 和FPGA 所在板卡上电后,二个芯片由于上电顺序和电路实现等原因,二个时间计数器开始计数的起始时刻点是不同的,这样上电后,分别位于ASIC 和FPGA 内部的二个时间计数器存在一定的计数相位偏差。在系统应用上,需要将二个时间计数器同步起来,并且在新的高精度同步系统上,要求具备亚纳秒级的同步精度。

当前二个时间计数器的同步,是通过数字方法实现的。如图2所示,ASIC 内的数字串行化模块将asic_cnt 时间计数器值按固定间隔定时取出并进行串行化数字编码,通过单根信号线串行化发送到FPGA。同时,clk1时钟也和串行时钟信息随路发出。也就是使用源同步串行传送的方式将ASIC 内的时间计数器asic_cnt 定时发送到对端的FPGA。

FPGA 收到串行时间信息编码后,数据解串模块使用随路过来的clk1时钟进行串行时间信息解码。解码后的并行时间信息发送到数据时钟转换器,该模块将clk1时钟域下解码后的并行时间信息切换到clk2时钟域。切换时钟域后的并行时间信息再送给时间同步控制器,时间同步控制器将该并行时间信息通过一定的延迟补偿后,设置更新FPGA 内的时间计数器fpga_cnt,使得二个时间计数器同步对齐。

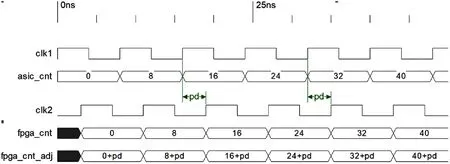

如何测量验证二个时间计数器是否同步对齐,是通过图2所示下方的二个测试1PPS 配合示波器测试来实现的。应用中clk1和clk2为同频的时钟,其步进周期为8纳秒,当asic_cnt 计数到一个整秒时,通过数字电路产生一个时钟周期宽度的1PPS 脉冲输出。当fpga_cnt 计数到一个整秒时,也通过数字电路产生一个时钟周期宽度的1PPS 脉冲输出。所以我们使用示波器的二个通道同时监视这二个1PPS 信号的相位,即可判断这两个时间计数器是否同步上了。同步后二个时间计数器的运行时序图如下图所示。

图3 同步误差时序示意图

图3所示时序,我们可以看出,由于驱动二个时间计数器的时钟源clk1和clk2具有一定的固定相位差pd,所以二个时间计数器并不能完全对齐,从示波器测试的表现看,二个1PPS 输出的相位还是存在数纳秒的差。并且这个固定相位差pd 在不同的电路设计上和不同的环境条件下,会是不同的值。所以我们无法通过固定的补偿方法来调整fpga_cnt,使得二个时间计数器最终能够严格对齐。所以该设计在当前工作时钟的情况下,二个时间计数器的偏差最大会达到8个纳秒,无法满足高精度同步系统的性能要求。

2.2 采用DDMTD 改进型设计

改进型设计是增加图2中所示深色模块的数字时钟相位检测器,该数字时钟相位检测器是基于上述DDMTD 的基本原理而工作的,为图1所示的纯数字逻辑设计,没有使用额外的FPGA 专用逻辑资源。所以实现的成本低,逻辑简单。

将clk1和clk2时钟送入数字时钟相位检测器,它将二个时钟的相位差精确的检测出来,其检测误差精度非常高。在后仿真和实际应用上,相位差的检测误差小于100个皮秒。我们得到二个时钟高精度的相位差检测值pd 后,将该检测值pd 送入时间同步控制器。时间同步控制器在设置更新时间计数器fpga_cnt 时,将pd 值考虑进去进行调整补偿。最后在原始fpga_cnt 产生得到一个调整后的时间计数器fpga_cnt_adj,其工作时序如图3所示。

从时序图3可以看出,经过调整同步后的时间计数器fpga_cnt_adj,已经将检测出的相位差值pd 考虑进去,所以fpga_cnt_adj 和asic_cnt 时间计数器已经达到非常高的同步精度。

使用同样的方法进行同步对齐验证。当asic_cnt 计数到一个整秒时,通过数字电路产生一个时钟周期宽度的1PPS 脉冲输出。当fpga_cnt_adj 计数到一个整秒时,也通过数字电路产生一个时钟周期宽度的1PPS 脉冲输出。示波器上观测到的二个1PPS 的相位差是严格对齐的,肉眼观察在1纳秒以内的偏差。实际后仿真结果的误差在100皮秒以内,示波器观测时会引入一定的测量误差,所以观测值稍微偏大。

3 结果及分析

本文描述的新的设计方案,是在原有设计的基础上,运用DDMTD 技术,自动检测二个输入时钟的相位偏差,将位于不同芯片内的时间计数器的同步性能提高了一个数量级。

另一方面,改进型设计不改变原有设计,不依赖于FPGA 内的专用逻辑资源,仅通过增加一个数字检测模块来实现。相对于其他的改进型设计方案,降低了系统实现的复杂度,也降低了整个系统的改进硬件成本。

4 结束语

基于FPGA 的实现,本文提出了一种基于DDMTD 的数字时钟相位检测实现方案,该技术实现已被应用到传输网络设备的同步芯片设计中。实际的系统同步测试结果表明,该方案将原来的时间同步误差由原先的8纳秒提高到现在的1纳秒以内,使得系统设计的时间同步性能大大优于现有IEEE 对5G 前传同步定时系统的性能要求。