基于ZYNQ-7000的远距无线时间同步系统的软件设计与实现

胡 庆, 罗孝杰

(成都大学 信息科学与工程学院, 四川 成都 610106)

0 引 言

随着通信技术的发展及需求,对远距离通信设备在信息交互时对时钟同步的精确度提出了更高的要求,以确保收到的信息准确无误.通信过程中若时钟未同步,则会导致接收的信息帧字节错位或接收失败,从而产生严重的后果.时间同步所要解决的就是传输时间标准问题,是保证通信系统可靠工作的一项重要技术措施.系统能否有效且可靠工作,很大程度上取决于是否有良好的同步系统[1].现有的时间同步技术主要有:IRIG-B与DCLS技术、NTP技术、1PPS及串行口ASCII字符串技术、PTP技术等[2-4],可以满足不同精度的时间同步需求.本项目采用1PPS及串行口ASCII字符串技术,用于局内时间传送,并采用人工补偿传输延时,精度达到100 ns量级.同时,使用基于微波的站间双向时间频率同步方法,在9~28 V DC工作电压范围内且两基站相距超过10 km的情况下,实现两基站时间同步,且其精度达到±10 ns.本研究重点探讨了本项目中基于ZYNQ-7000芯片的远距离无线时间同步系统的软件设计与实现部分.

1 软件设计方案

当两站相距较近且可通视情况下,基于微波的站间双向时间频率同步方法是一种较为理想的站间时间频率同步方法,其同步工作原理如图1所示.

图1基于微波的站间双向时间频率同步方法原理图

参与双向时间频率传递的站A、B依据各自的时钟,在同一钟面时刻向对方发送代表时间起始点的1 pps信号脉冲.每个站测量从本地产生1 pps时标信号开始,到收到对方信号且恢复对方发送的1 pps时标信号为止这段时差.站A、B将各自测得的时差信息插入基带数据中通过反向链路相互交换,由数据处理软件对两站测量的时差结果求差,可得到站A、B之间的时间差.

假设站A时钟与站B时钟之间的钟差为δt,时基信号自站B发射到站A接收的传播时延为TBA,自站B发射至站A接收的传播时延为TAB,则由图1可得,

TBA+TA=TAB+TB+2δt

(1)

因此,

(2)

式中,TA和TB作为观测量,可以直接获得;TBA和TAB为信号传播路径上的时延,不能精确测量,只能建立其数学模型.式(2)即为双向时间同步解算公式.

双向信号传播时延的数学模型如式(3)、式(4)所示,

(3)

(4)

由于两站同步信号的几何传输距离相同,因此可得两站时差测量公式为,

(5)

当获取两站的时间差后,则可方便地求出两站相对频率偏差为,

(6)

式(6)中,τ为取样时间,x(0)为两站初始时间差,x(τ)为两站经过取样时间τ后时间差,fA、fB分别为取样时间内站A和站B时钟的平均频率.由于采用扩频体制,时差测量的精度非常高,路径上的误差项大部分可以相互对消,因此双向时间频率传递技术可实现高精度的时间与频率比对.

2 程序设计

2.1 程序架构与运行设计

系统主函数实现结构如图2所示,主要包括日志打印初始化、内存池初始化、状态机初始化、平台初始化、CPU计时器初始化与状态机流程运行等方面.

程序从main函数入口,首先进行日志轮询的初始化、内存池的初始化、软件正常执行所需要的状态机初始化与平台初始化(即,针对ZYNQ-7000系列芯片对各种参数进行初始化,包括基本的ZYNQ-7000系列的系统配置初始化、GPIO初始化、IRQ中断初始化等),然后开始CPU计时器初始化并运行CPU计时器,计时等待20 s后将中断打开,判断是否定义WatchDog.正常情况下,程序定义了WatchDog后就需要进行WatchDog的初始化,防止异常而导致死机.若程序异常,则中断打开,Reboot自动重启,系统启动.通常,系统在调试时不会定义WatchDog,目的是方便调试.然后,系统直接进行状态机流程的工作.

图2系统主函数结构

2.2 功能函数设计

系统软件部分采用C语言编写.C语言具有简洁紧凑、灵活方便、运算符丰富、数据结构丰富、代码量小及运行速度快等优点,尤其在Linux和单片机系统下,可靠性与规范性较强[5].

系统实现的流程为:主、从节点在不同时刻上电,开始时以自己的RTC时间运行,在同一钟面时刻向对面发送代表时间起始点1 pps信号脉冲,即每秒的秒帧头,然后由软件控制可编程逻辑模块(Field-programming gate array,FPGA)捕获跟踪,FPGA将得到的数据上报,软件进行收集、组帧、处理,对两节点的时差(双向路径延时、链路延时、AD9361延时等)进行补偿,从而达到两节点的时间频率同步.两节点精同步后,因为两基站在海上运行且距离是变化的,所以从节点还需要在每秒进行一次微调,确保两基站通信完整.

整个流程中,时间同步分为粗同步和精同步.粗同步保证两节点在200 ms内对齐,能发现接收到数据且打印正确.精同步保证两节点在±10 ns内对齐,通过示波器观察两节点脉冲信号距离相差不超过10 ns,且从节点脉冲信号抖动范围在10 ns左右.

本设计1 s内发送帧排列的步骤为:1 s内5帧交替发送,且3帧为同步,2帧为数据.所以,需要收集3帧(300 bit数据)才能满足收集到的3帧中至少有完整的2帧数据,且在2帧数据中至少有1帧为同步帧,才能满足相关的需求.进行同步时,以主机的RTC时间为准,从机的RTC通过调整与主机的RTC时间对齐.

特别注意,本设计在每次代码编辑完成且上板调试成功后,会使用Git版本管理工具[6]来管理代码,以便在遇到问题时能尽快恢复到之前的代码.

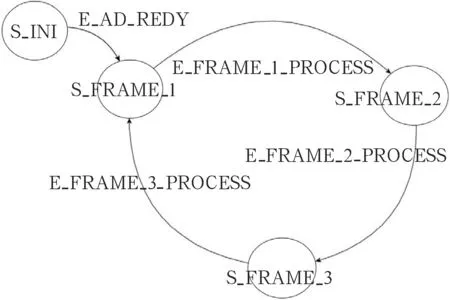

2.3 主从节点状态机跳转流程

主节点状态机流程图如图3所示.在板卡上电后,主机的状态处于S-INI;当CPU中断函数上报E-AD-READY后,执行setup-fpga函数;由S-INI状态跳转到S-FRAME-1状态;当捕获跟踪完成后,再跟踪完成中断上报事件,执行frame-1-process;由S-FRAME-1状态跳转到S-FRAME-2状态,之后跳转依次如图3所示.主机调整同步的目的,只是为保证收到从机发来的数据排列正确且对齐,并不判断收到的数据本身是否正确.

图3主节点状态机流程图

从节点状态机流程图如图4所示,其跳转与主机基本一致,不同之处在于:从机完成同步之后还需要进行精同步微调,才能达到时间偏差在10 ns左右,或者小于10 ns;精同步微调时的函数是将每帧都做出判断与处理,而粗同步每次会处理3帧.

图4 从节点状态机流程图

3 调试结果

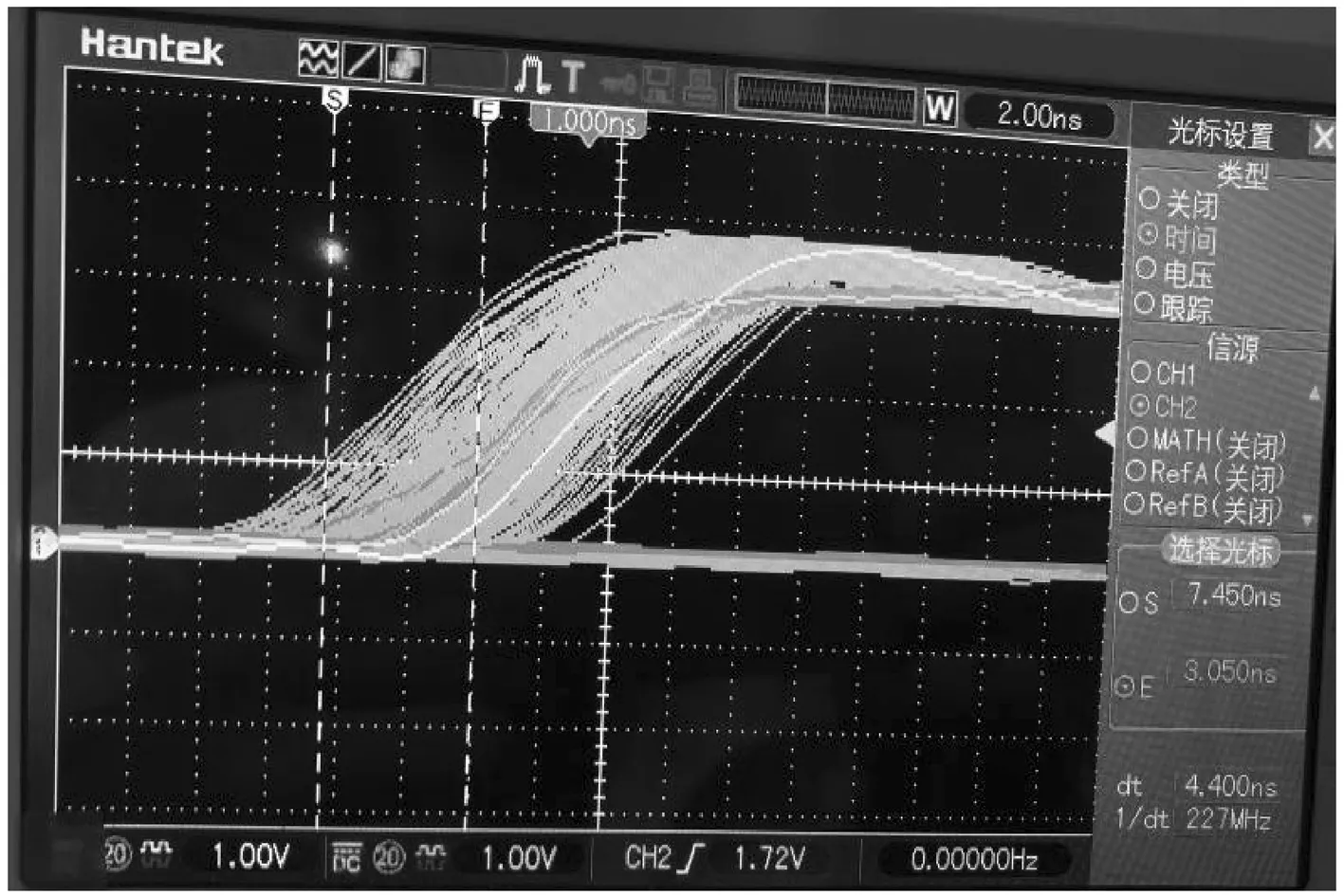

在系统调试时,将FPGA与软件上板联调,通过串口或网口用PUTTY终端连接软件访问,登录进板卡,然后运行日志打印软件,将存好的日志信息打印出来,通过打印信息来确认粗、精同步是否成功.图5为主节点同步后数据打印情况,图6为从节点同步后数据打印情况,精度均达到10 ns内同步要求.接着从系统引出导线连接至示波器,此处导线引出的脉冲信号是秒帧头脉冲信号,主节点引出的脉冲信号基本固定不变.

图5主节点同步后的输出数据

图6从节点同步后的输出数据

图7为主从节点同步后秒帧头最远的差距,如图7所示,其值为4.400 ns.图8为主从节点同步后微调时从节点秒帧头抖动范围,从节点脉冲信号在主节点脉冲信号旁,偏差很小,如图8所示,从节点脉冲信号抖动范围小于10 ns.

图7主从节点同步后秒帧头最远的差距

图8主从节点同步后微调时从节点秒帧头抖动范围

4 结 语

本研究基于微波的站间双向时间频率同步方法实现远距无线时间同步系统的软件设计,由软件控制FPGA捕获跟踪,由FPGA将得到的数据上报,由软件进行收集、组帧与处理,然后对两节点的时差(双向路径延时、链路延时与AD9361延时等)进行补偿,从而达到两节点的时间频率同步,且同步精度可达±10 ns.此远距无线时间同步系统输出的定时同步脉冲可供其他需要精确时钟同步的无线通信设备使用,在实际项目和产品开发中具有一定的参考和实用价值.