超高分辨率光电探测图像预处理系统设计

袁汉钦

(海军驻合肥地区军事代表室,安徽 合肥 230088)

0 引 言

随着现代军事技术的发展,要求航空光电探测系统获取的图像分辨率越来越高。目前,国内最大面阵的CCD分辨率已达到一亿像素。大面阵的CCD为提高拍摄帧频通常采用多通道输出的方式,因此需要在后续处理电路中将这些分通道输出的图像,完整地拼接成一幅图像。如此巨大的数据量对数字图像处理系统以及数据存储系统来说都是一个巨大的挑战。在光电探测系统设计、调试过程中以及在执行任务时,必须对光电探测系统输出的图像进行实时观测,以便判断系统的工作状况以及观察拍摄到的景物图像[1-3]。目前的大部分光电探测系统的图像采集卡对如此巨幅的图像都无法完全采集。对于超高分辨率的图像采集与预处理,目前工程上仅能够通过使用高性能的服务器配合专用采集卡才能实现[4-6]。这给特大面阵的图像实时观测带来困难,而且整个系统体积较为庞大、携带极为不便,不能满足航空军事技术发展需求,因此迫切需要设计一种便携式且能直接显示超高分辨率光电探测获取图像实时显示系统。本文以实际工程需求为牵引,设计了一种满足超高分辨率光电探测系统的图像采集、显示预处理系统。该系统只需配备一个标准接口的显示器即可完成对超高分辨率图像的采集和实时观测,且系统安装调试简单,适合当前航空军事技术对超高分辨光电探测系统的图像预处理需求。

1 系统接口电路设计

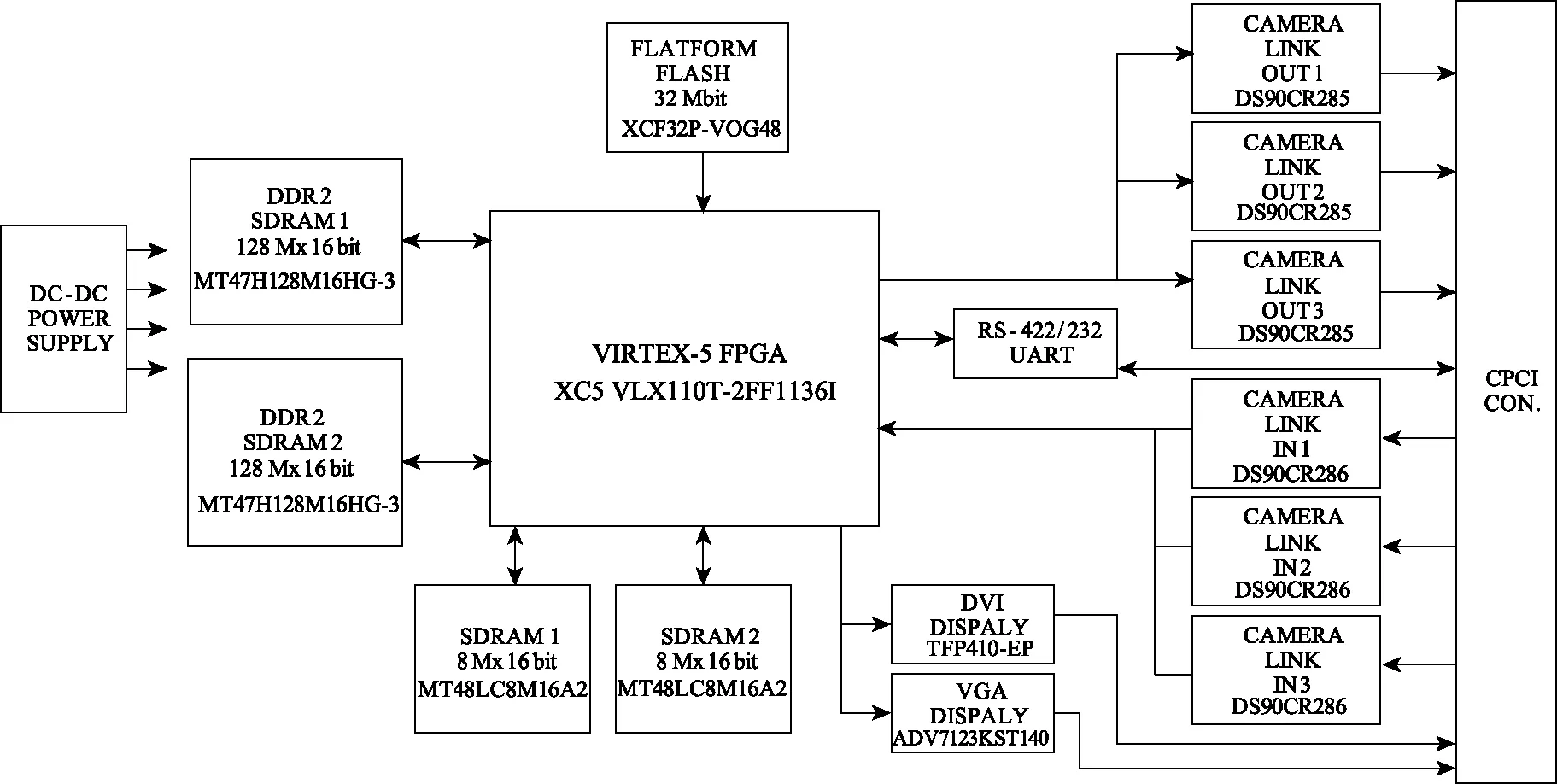

本文所设计的超高分辨率光电探测图像预处理系统接口电路由CameraLink与FPGA的接口电路、DDR2存储器与FPGA的接口电路、SDRAM与FPGA的接口电路、DVI和VGA与FPGA接口电路以及串口与FPGA接口电路组成。CameraLink与FPGA接口电路在设计过程中将超高分辨率光电传感器获取的不同路信号通过3个Base配置的CameraLink接口从传感器输入到显示系统,并通过串并转换芯片DS90CR288将串行数据重新组合成多路并行数据送往FPGA。同时,经过预处理后的图像经过1个CameraLink Base头分2路输出到下一级系统。DDR2存储器与FPGA的接口电路采用两片大容量的DDR2作为高速数据缓存器,通过将5路图像依次缓存到DDR2完成图像的拼接。选用的DDR2存储器容量为128 M×16 bit,足够存储一幅完整的图像。在SDRAM与FPGA的接口电路中,SDRAM存储器主要用于显示图像,图像数据在FPGA中经过拼接、Bin操作后需缓存到SDRAM。由于相机输出的是位深度为12 bits的图像,因此选用两片容量为4 Bank×2M×16 bits的大容量HY57V281620 SDRAM来缓存BIN操作后的图像。DVI和VGA与FPGA接口电路作为显示电路,在显示过程中,FPGA中的逻辑配合VGA和DVI的时序将数据从SDRAM中读出,经过显示芯片编码以后生成显示器能辨认的数据格式进行显示。串口与FPGA接口电路主要用于上位机与FPGA之间的信息交换,如通过设置FPGA内部逻辑的工作方式,设置图像显示窗口的起始坐标,BIN模式的BIN倍率,以及数字增益倍率等。

系统接口电路设计原理图如图1所示。其中,FPGA是主要的逻辑器件,系统的主要逻辑功能都是在FPGA中完成的。为方便控制和协调FPGA中的各个模块,在FPGA中设计了一个MicroBlaze处理器,完成串口通信和FPGA内部寄存器参数设置等功能[7-10]。

图1 系统硬件电路设计原理框图

2 系统功能电路设计

2.1 总体架构设计

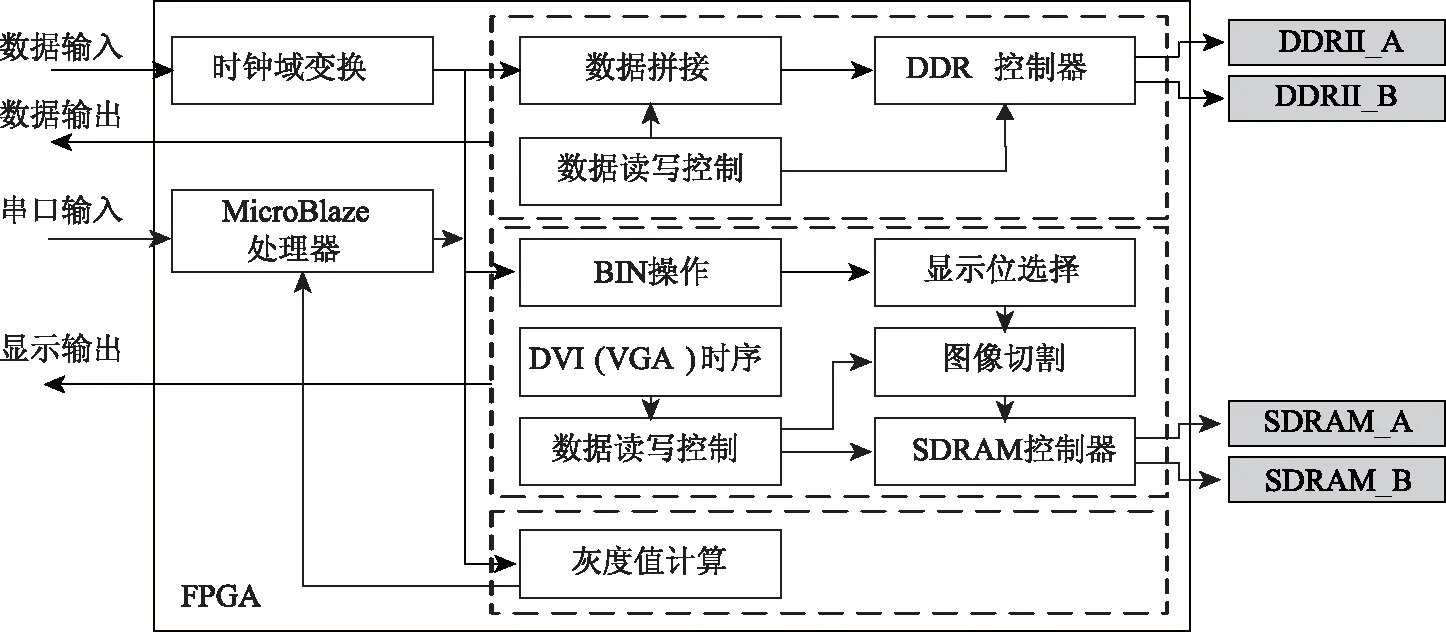

根据系统硬件电路设计原理框图可知,本文所设计的超高分辨率光电探测图像预处理系统是以FPGA为核心管理器件的硬件电路。在FPGA内部共设计了五个功能模块。分别为数据时钟域变换模块,数据拼接缓冲模块,MicroBlaze处理器模块,图像分辨率变换及显示模块以及图像平均灰度值计算模块。系统功能模块设计框图如图2所示。其中MB处理器核、数据拼接缓冲模块以及分辨率变换显示模块是系统的核心模块,也是内部功能模块设计的重点。

图2 系统功能模块设计框图

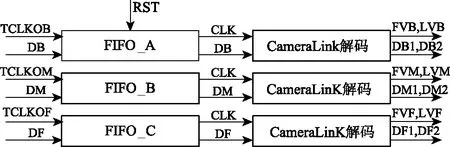

2.2 时钟域变换模块

时钟域变换模块设计是为了保证系统设计的稳定可靠而需要进行时钟域变换,主要功能是将从外部与数据一起输入的时钟域变换到FPGA内部时钟域,从而可以有效解决由于传输过程中导致的时钟信号质量差而使数据不稳定的问题。本系统时钟域变换采用FIFO方式实现,具体实现方式如图3所示。

图3 时钟域变换示意图

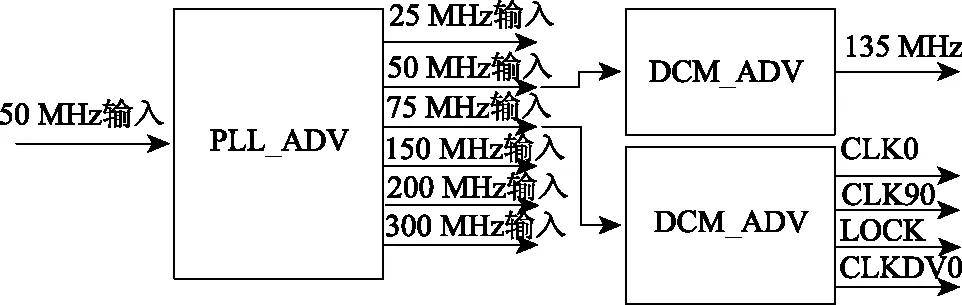

2.3 时钟树设计

在FPGA内部由于需要的时钟种类较多。具体包括数据处理时钟及DDR2控制器专用时钟两大部分。时钟树采用PLL(延迟锁相环)来产生,该IP可由1个时钟产生多个输出时钟。DDR2控制器需要一组特殊的时钟,这组时钟的相位关系以及频率都有严格的要求,采用DCM模块来产生,时钟树设计产生框图如图4所示。

图4 时钟树设计产生框图

2.4 数据缓存及拼接模块

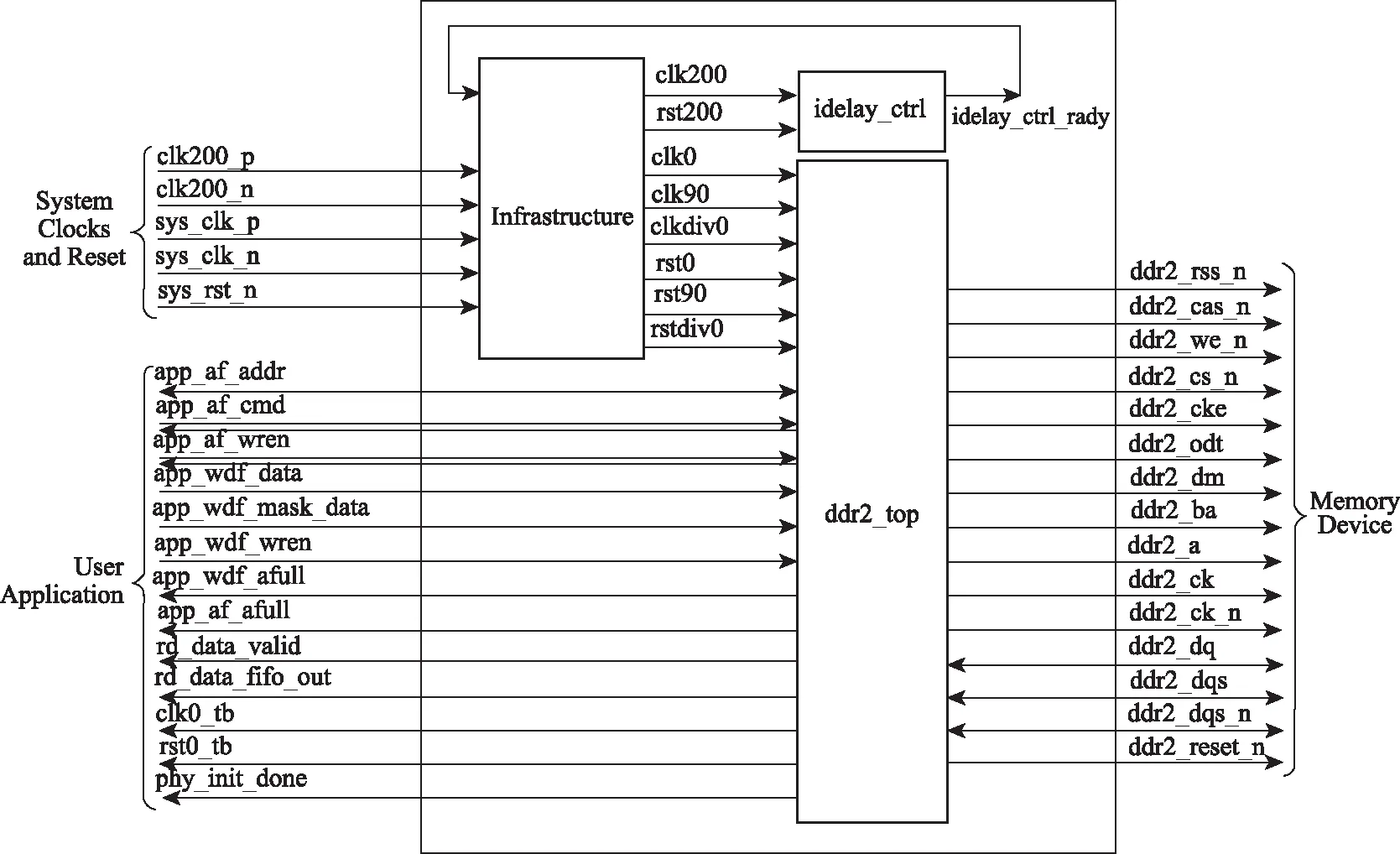

由于图像数据不能直接写入DDR2存储器,而是需要通过DDR2控制器接口来完成将数据写入DDR2的要求。因此,必须首先完成DDR2控制器的设计。通过DDR2控制器可将光电探测设备获取的多路图像数据依次写入DDR2,从而拼接成一幅完整的图像。目前,较高版本的Xilinx FPGA开发软件ISE中都嵌入了成熟的DDR2控制器IP核,使用MIG(Memory Imterface Generator)工具即可根据实际需要完成对DDR2控制器的配置,然后生成一个需要根据实际设计进行修改的DDR2控制器初核。该IP核的接口信号如图5所示,主要分为三类信号分别为系统时钟和复位信号、用户接口信号以及DDR2接口信号。

图5 DDR2控制器接口信号

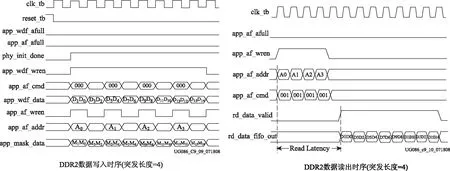

DDR2控制器内部通过基于FIFO来完成数据读写操作,地址/命令FIFO接收数据存储的地址和读写指令;数据/掩膜FIFO接收或读取数据和相应掩码。同时,控制器内部也产生了一些内部状态信号,如app_af_afull和app_wdf_afull两个状态信号,分别表示了两个FIFO的内部数据状态,用户必须在这两个信号均有效的情况下进行DDR2读写,否则会造成数据的丢失或漏读。虽然MIG可生成DDR2控制器的IP核,但生成的IP需要根据实际设计中的管脚分配状况进行参数设置,包括在UCF文件中,根据DDR2管脚的分配状况对需要用到的一些管脚和FPGA内部资源进行约束以及在对ISE工程顶层HDL文件中DR2_DQS_IO_COL和DDR2_DQS_IO_MS参数进行修改。由系统生成的IP核内部代码则不需要进行修改。

DDR2数据操作以时钟的双边沿进行,差分时钟的上升沿、下降沿各进行一个数据的读写操作,这两个边沿的数据被合并在一个两倍于读写数据位宽的数据中送入数据FIFO。同时,在数据写入时必须先发送读写命令及数据操作地址,再发送数据。具体操作时序见图6所示。

图6 DDR2数据读写时序图

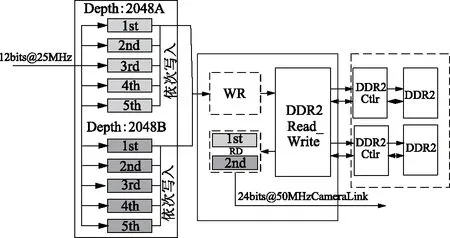

图像拼接策略如图7所示,采用两组FIFO交替进行数据缓存,每一组FIFO由5个输入位宽为16位,输出位宽为32位的FIFO组成。设置两组FIFO的主要是为防止数据操作时行与行之间严格对齐,否则数据写入DDR2后就有可能造成行与行之间数据错位,在每读完一行数据后都对FIFO进行一次数据复位,清空FIFO,迎接下一行数据的到来。

由于采用较高时钟进行数据传输过程中,对系统逻辑架构设计的鲁棒性要求较高,因此本文所示系统在数据输出时采用两路数据12bits@50MHz输出的方法,避免单路输出时钟达到100 MHz造成数据传输错误。

图7 数据拼接示意图

2.5 图像分辨率变换与现实模块

图像分辨率比变换实现如图8所示。图中倍率寄存器主要用于设置BIN操作的合并像素数。在实际应用中采用1×1,2×2,4×4,8×8几种倍率,将超高分辨率图像的分辨率分别降为多种不同的低分辨率进行处理。倍率寄存器是通过MB处理器来设置的。对于N×N BIN,首先将一行像素中相邻的N个像素合并成一个像素,并将BIN后的该行图像存入FIFO;在第二行图像到来时,读出上一行的图像将这两行图像相加,直到完成N行图像的BIN操作。

图8 BIN操作示意图

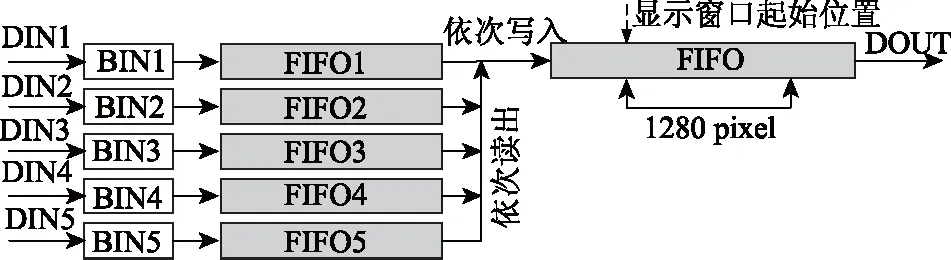

由于需要实时对光电传感器获取的图像进行观测,同时为避免图像在外部存储器中进行缓存后变换带来的帧延时,因此只能对原始图像信息进行直接变换处理。由于传感器同时输出多路路图像,只能对其分别进行BIN操作,然后再进行对BIN后的图像进行拼接。同时,对于分辨率变换后图像依然大于显示器分辨率的情况,需要采用窗口选择的方法,选择一块连续的区域进行显示。为保证显示窗口的位置可连续设置以及显示图像的连续性,在将数据写入外部存储器DDR2中时,将多路数据合成一路的数据送入BIN模块进行BIN操作,此时需要一个FIFO将32bits@150MHz的数据解成12bits@300MHz的数据格式。将多路原始数据分别进行BIN操作后再用不同FIFO缓存起来,在进入SDRAM进行缓存之前将他们拼接起来合成一幅完整的BIN图像。图9是BIN图像拼接及显示窗口位置选择示意图。对传感器输出的5路图像分别进行经过BIN模块进行分辨率变换后形成5路图像,必须将这5路图像拼接在一起才能保证在显示时的数据是连续的。BIN后的数据拼接主要依靠6个FIFO,前5个FIFO分别将5路BIN后的数据进行缓存,然后依次读出存入到第6个FIFO,形成一行连续的、经过BIN操作的图像数据,此后根据显示窗口位置寄存器X方向参数对第6个FIFO中的数据进行截取,存入SDRAM中,等待读出、显示。而对于行方向上的数据截取则采用一个计数器,根据显示窗口位置寄存器中Y方向参数来设置该计数器的起点,完成对图像Y方向上的数据截取。

图9 BIN图像拼接及显示窗口位置选择

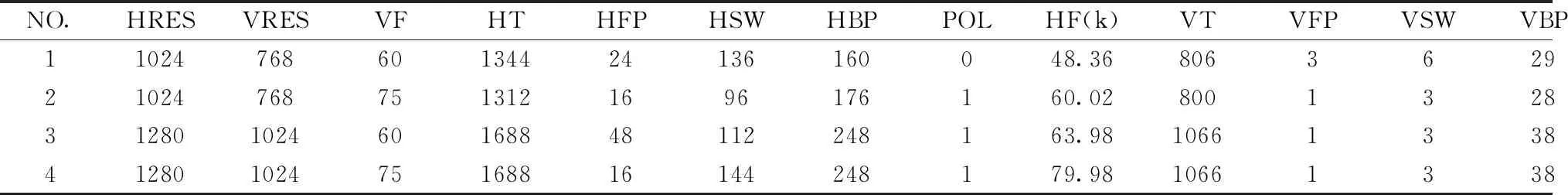

系统设计的图像显示是基于两片SDRAM存储器进行的。经过分辨率变换和图像大小截取后,将图像大小变换为1280×1024分辨率,交替存入这两片SDRAM存储器中,再配合VGA或DVI时序读出SDRAM中的图像数据,输出到视频编码芯片变换成显示器能够识别的图像格式,完成图像的显示。整个过程最重要的是对SDRAM的读写操作和DVI(VGA)显示时序的产生,DVI具体时序参数可见表1。为尽可能显示较大的图像面积,观察较广的图像范围,选用1280×1024分辨率进行显示。由表1可知,当显示图像分辨率为1280×1024,显示帧频为75 Hz时,因此需要的时钟频率高达135 MHz。

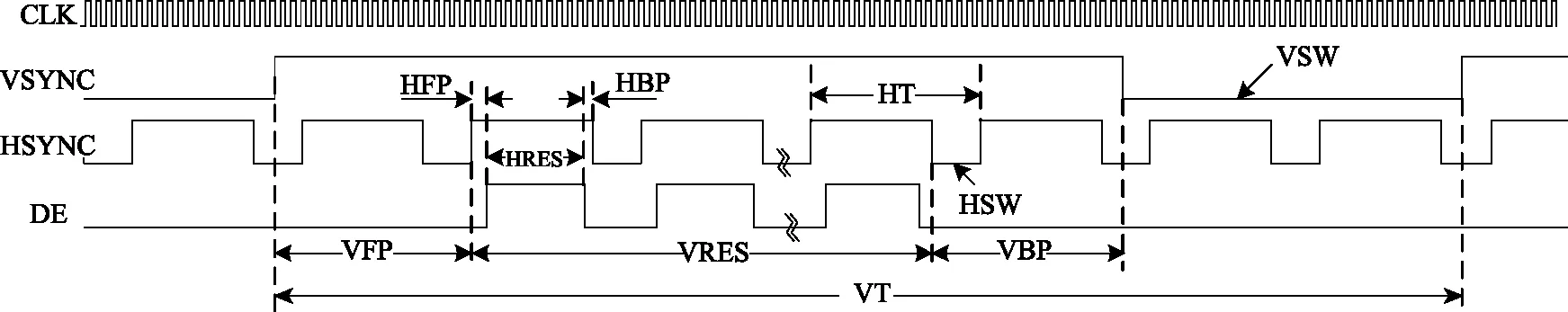

各时序参数的具体含义由图10来表示。根据DVI显示时序图,只要在HRES阶段向DVI数据编码器TFP410送出有效数据即可完成数据的编码。

系统对SDRAM的读写控制也是通过SDRAM控制器来完成[11]。SDRAM操作采用乒乓操作的方式,将图像数据写入第一片SDRAM的同时,以75帧/秒的速率读出另一片SDRAM中的图像数据。

表1 常用DVI显示时序参数表

注:HRES:水平分辨率,VRES:垂直分辨率,VF:垂直刷新率,HT:水平像素总数,HFP:行同步前肩,HSW:行同步信号宽度,HBP:行同步后肩,POL:极性,HF:行频,VT:总行数,VFP:垂直同步前肩,VSW:垂直同步宽度,VBP:垂直同步后肩,PCLK:像素时钟频率。

图10 DVI(VGA)时序图

这样既可以保证显示效果的连续性,也能保证数据不丢帧。在进入DVI时序HRES之前的若干个时钟周期,先将需要显示的图像读出存储在FIFO中,当HRES到来时,直接从该FIFO中读出有效数据,完成数据与时序控制信号之间的无缝衔接。同时,对于图像分辨率小于1280×1024的图像,将该图像显示于显示器的中央,对图像周围无像素的区域进行置零,从而只显示有效的图像区域。

3 结 语

本文以现代航空光电探测系统对超高分辨率图像采集、处理与显示为牵引,以机载超高分辨率图像对实时预处理系统需求为导向,针对基于CameraLink接口CCD光电探测传感器获取的图像不能直接显示的问题,设计了一种图像实时显示系统。首先介绍了系统硬件电路的总体技术架构,详细分析了基于FPGA的核心硬件电路内部主要功能模块的作用以及其具体实现方法。实际工程应用结果表明本文所设计的光电探测图像预处理系统的处理能力能够很好地满足机载超高分辨率光电探测设备对多分辨率,尤其是超高分辨率图像的实时采集处理和增强显示要求。此外,按照本文所设计的系统,通过修改系统核心硬件内部参数,可直接应用到其他基于CameraLink接口的不同面阵大小的CCD中,具有良好的通用性。