一种基于FPGA的高精度定时内插间隔估计方法*

陈 章,安君帅

(南京熊猫汉达科技有限公司,江苏 南京 210001)

0 引 言

数字通信系统的收发信机设计正在向全数字化方向发展。位定时同步作为全数字接收机的关键技术一直备受关注,是各类系统研究的热点问题[1-2],而定时恢复的好坏将直接影响接收机的工作性能。

对于高动态运行的终端,由于其动态特性引入的多普勒变化率较为严重,为获取较高EVM质量的信号,通常采用闭环环路实现位定时同步。一般来讲,位定时过程分为定时误差检测和误差校正两步。经典的误差检测算法包括Gardner算法和平方法,之后的研究提出了许多改进算法,关注点通常集中在定时误差检测和环路滤波器设计的改进上[3-8]。文献[6]对QAM信号给出了改进的Garnder算法,文献[7]通过对信号采样平方做离散FFT提取定时信息,文献[8]针对过采样倍数高、定时抖动大等问题提出了改进算法。误差校正通常通过内插滤波器实现,之后的研究提出了许多内插滤波器设计方法。文献[9]基于Chebyshev最佳一致逼近设计最佳内插滤波器;文献[10]引入线性加权的概念,基于最小均方误差的准则设计高性能滤波器,但只适用于高阶QAM信号;文献[11]对立方插值系数的计算方式与插值时刻进行了改进,需要通过矩阵运算完成,工程实现复杂度高;文献[12]采用频域最优法对样条插值器进行改进。以上改进方法大多数集中于理论研究层面,未充分考虑工程实现的复杂度和通用性,如内插滤波器的改进算法多是从系统角度对内插滤波器逼近,这样在对逼近误差进行滤波后再平均分配到定时输出上,精度严重降低。为提高精度,需采用高阶内插设计,而这大大增加了工程实现复杂度和硬件开销。

为在不增加工程实现复杂度和硬件资源开销的基础上提高内插精度,本文提出了一种基于FPGA的高精度定时恢复内插间隔估计方法,可将内插间隔估计精度提高到FPGA处理主时钟级别,由此降低对内插滤波器的设计要求,可在常规低资源开销的内插滤波器设计基础上仍然取得较高的定时恢复精度。

1 定时同步环模型

本文采用的定时同步环结构如图1所示,包括异步抽样器、内插滤波器、定时误差检测器、环路滤波器以及高精度内插器控制器。

图1 高精度位定时同步环结构

(1)异步抽样器用于获得与所需采样速率接近的采样数据。本文设计采样模块采用异步抽样结构,假设系统基带处理时钟Tm,通过生成一个分频时钟Ts,使其接近系统需要的接收信号采样速率Tr,并用其对接收数据x(t)进行采样得到输出信号x(mTs)=x(m)。本文对基带处理时钟Tm和接收信号采样速率Tr不做整数倍要求,可根据系统精度和处理效率要求任意设定基带处理时钟,无需增加额外的时钟模块产生分数倍的时钟。

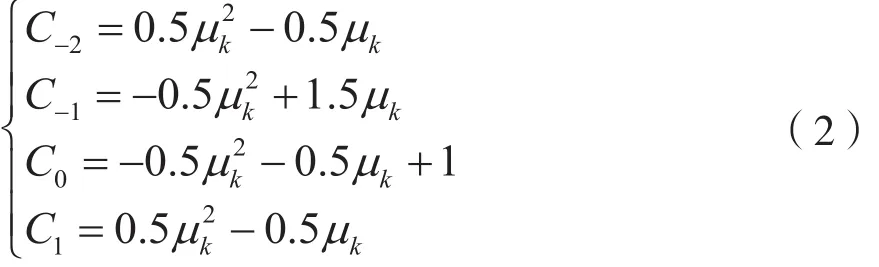

(2)内插滤波器用于在数字域对采样值数据进行修正,得到与发送机时钟频率相等的信号。综合考虑工程实现复杂度、内插精度和硬件资源占用量,本文采用基于Farrow结构的四点分段抛物线内插滤波器,结构如图2所示。Farrow内插滤波器的传递函数满足:

式中,Ci(i=-2,-1,0,1)为滤波器系数,满足:

式中,μk为小数内插间隔,可通过内插控制器估计得到。内插间隔μk的精度决定了内插输出的精度,为获得高精度内插输出,本文提出了一种高精度内插间隔估计方法。

图2 内插器结构

2 高精度内插间隔估计方法

在内插器模块中,通过基准点mk标定当前的I个信号抽样值,通过内插间隔μk标定当前的滤波器抽样值。内插器控制模块可以通过累减NCO实现,本文提出的高精度内插间隔估计方法核心思想如图3所示。

图3 内插间隔估计方法

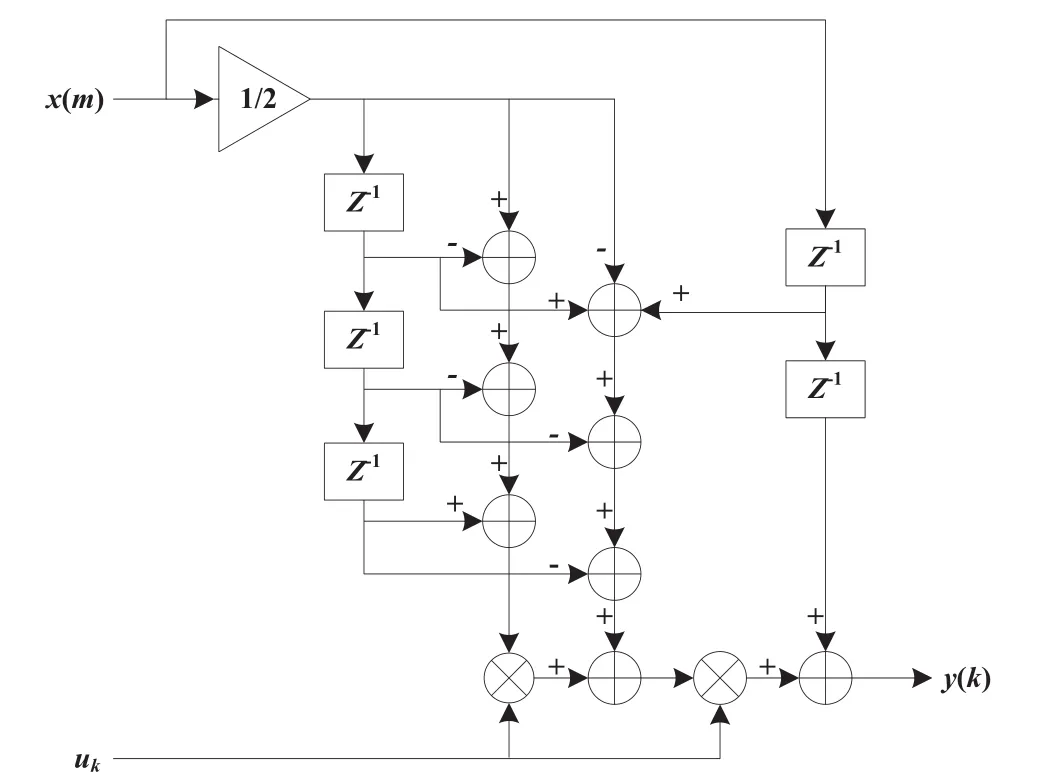

假设位定时误差检测模块输出为e(mTm)=e(m),则第m个时钟时NCO的输入值η(mTm)=η(m)为:

式中,[·]表示取整,N为NCO控制模块的累加精度。NCO寄存器中的瞬时值为φ(m)为:

小数间隔的产生与NCO翻转前的剩余相位有关。假设NCO寄存器的值在t=kTr出现下溢,由三角关系可知 μ=φ(m)/η(m)。定义 δ=2M-NTr/Tm≈1/η(m),M用于规定δ的量化精度,则μ可近似等效为:

内插滤波器所需的内插间隔μk以输入数据速率Ts为参考基准,从图3可以看出:

由于输入数据速率Ts由基带处理时钟Tm整数倍分频得到,假设分频比为S,则可以得到:

通过式即可得到内插间隔的高精度估计。

在常规处理方法中,由于μk为小数间隔,μk的估计误差完全由量化精度决定。本文将小数间隔μk按照基带处理时钟Tm进行切割,估计误差由μ带来,此时得到的估计误差小于Tm。按照上述方法,本文设计的高精度内插间隔估计结构如图4所示。

图4 内插间隔估计结构

3 结果分析

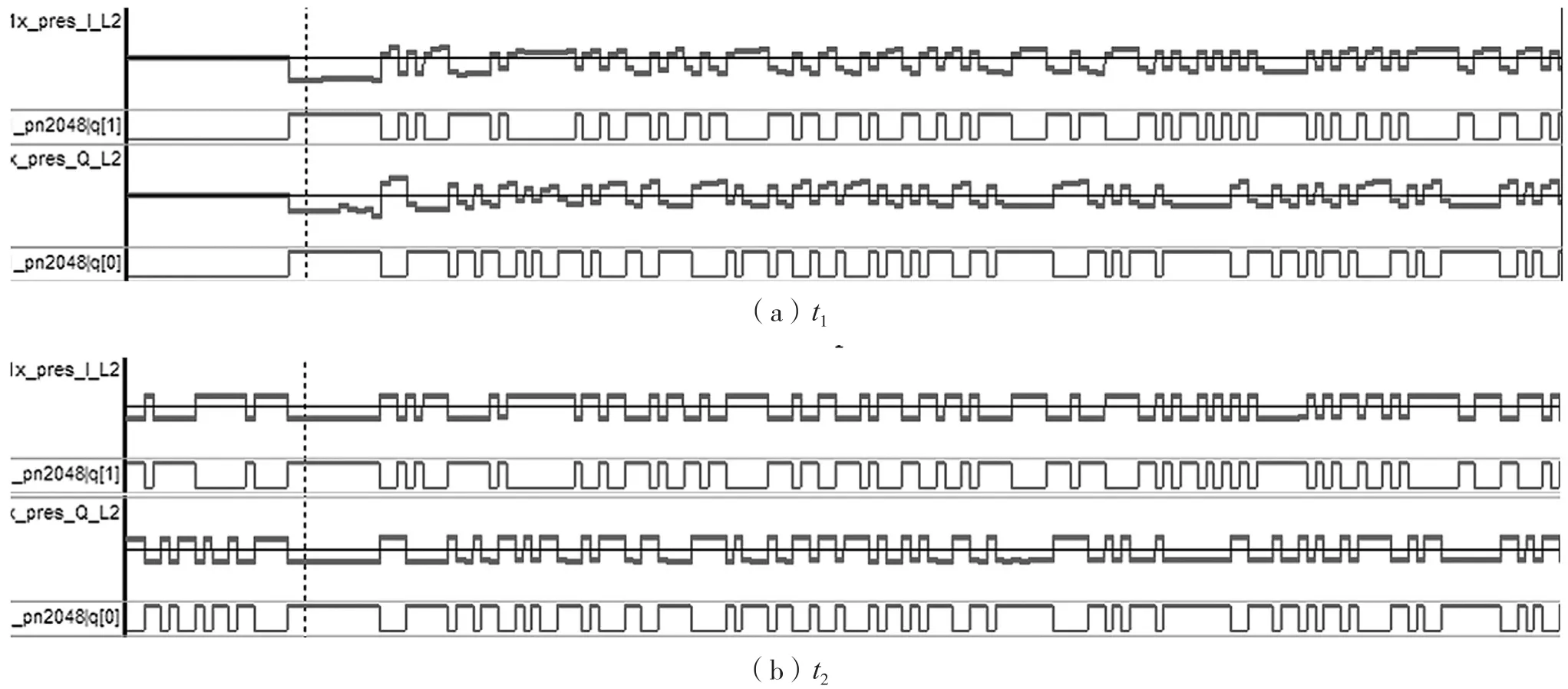

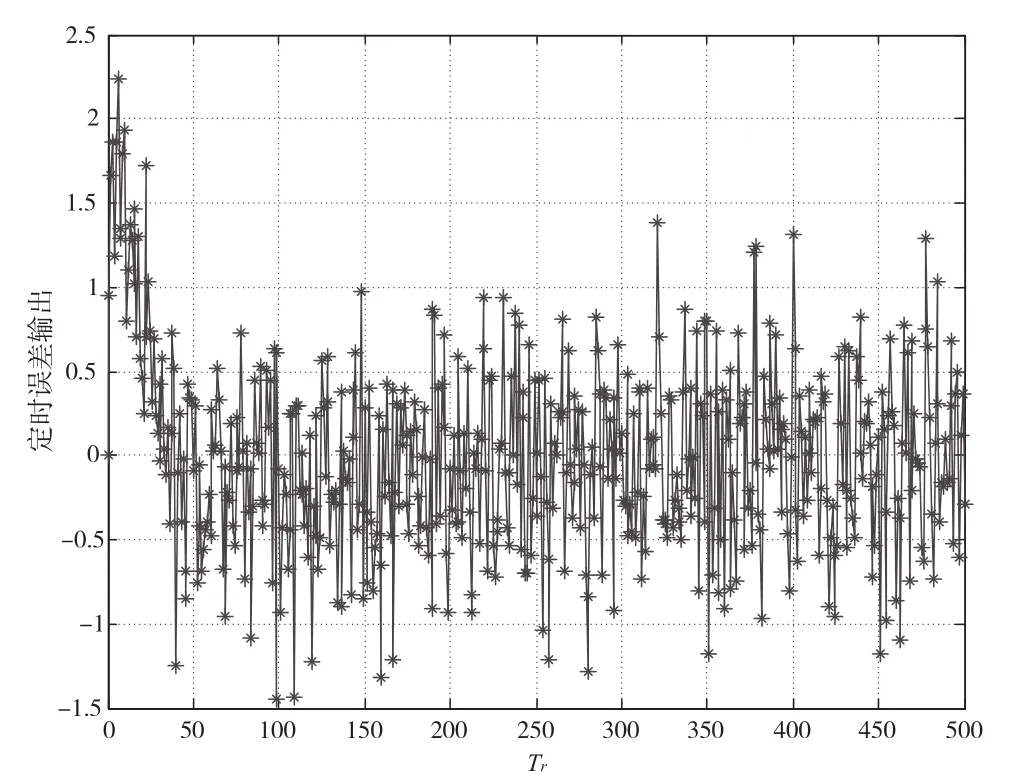

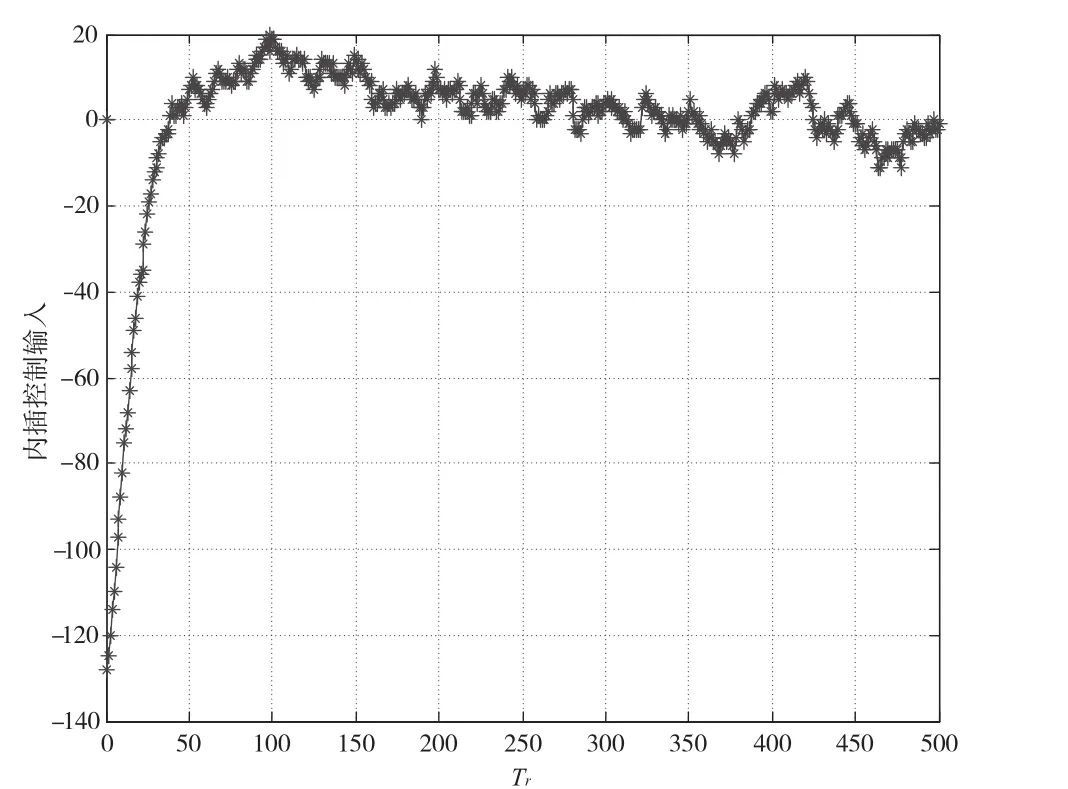

为验证本系统高精度位定时同步环性能,系统预设模型输入Eb/N0=3 dB的信号,同时叠加一定的多普勒残余。位定时同步环的内插滤波器输出收敛过程如图5所示,定时误差检测输出如图6所示,高精度内插控制器输入如图7所示。

图5 定时同步环收敛过程

图6 定时误差检测输出

图7 高精度内插控制器输入

可以看出,基于本文的高精度定时恢复内插间隔估计方法设计的位定时同步环,在系统运行过程中不断收敛于最佳采样位置,可获得低于系统主时钟的恢复精度,相较于内插间隔估计方法环路设计,大大提升了定时恢复精度,且时序逻辑控制简单,工程实现复杂度低,同时占用硬件资源小,对内插滤波器设计的要求低。

4 结 语

针对全数字化接收机位定时技术存在的位定时同步精度低、工程实现复杂度高、硬件开销大等问题,提出了一种基于FPGA的高精度定时恢复内插间隔估计方法。应用该方法设计的定时同步环在不增加内插滤波器设计要求的同时,能够有效提高定时恢复精度,工程实现复杂度低,占用硬件资源小。