一种基于共用存储空间的FPGA的QC-LDPC码并行译码架构

陈章 安君帅 王本庆

摘 要:针对QC-LDPC码并行译码FPGA实现结构复杂、资源消耗大等不足,文章提出一种中间计算变量的共用FPGA存储资源的QC-LDPC码并行译码架构,此架构通过两个交织单元,使得变量更新节点和校验更新节点的结构使用同一个存储资源,该架构具有控制简单、效率高和存储需求量低等优点,适用于高速卫星、地面等通信系统接收机中。

关键词:准循环结构;低密度奇偶校验译码;现场可编程逻辑门阵列;资源共享

准循环结构的低密度奇偶校验码(Quasi Cyclic-Low Density Parity Check Code,QC-LDPC)具有良好的编译码实现特性,被广泛应用于地面移动5G标准、DVB-S2标准(IRA-LDPC)等国际通信标准中。采用QC-LDPC一方面可以提升编码增益,另一方面编码译码时可采用多路并行译码,提升系统的吞吐量。LDPC的通用译码算法是置信度传播(Belief Propagation,BP)算法,是一种迭代的概率译码算法,硬件实现中一般采用最小和算法(Min-Sum Algorithm,MSA)进行近似。MSA包括变量节点更新和校验节点更新两个主要环节,在并行译码算法时两个环节之间的中间计算结果需要进行二维交织和二级缓存[1-8]。本文基于QC-LDPC码的准循环特点,在并行译码时的中间把数据存储到共用存储空间,更新时利用两个交织器,只需要进行列间交织和列内循环移位即可实现二维交织,把二维运算简化为两个一维运算,极大节省了存储空间。

1 QC-LDPC码

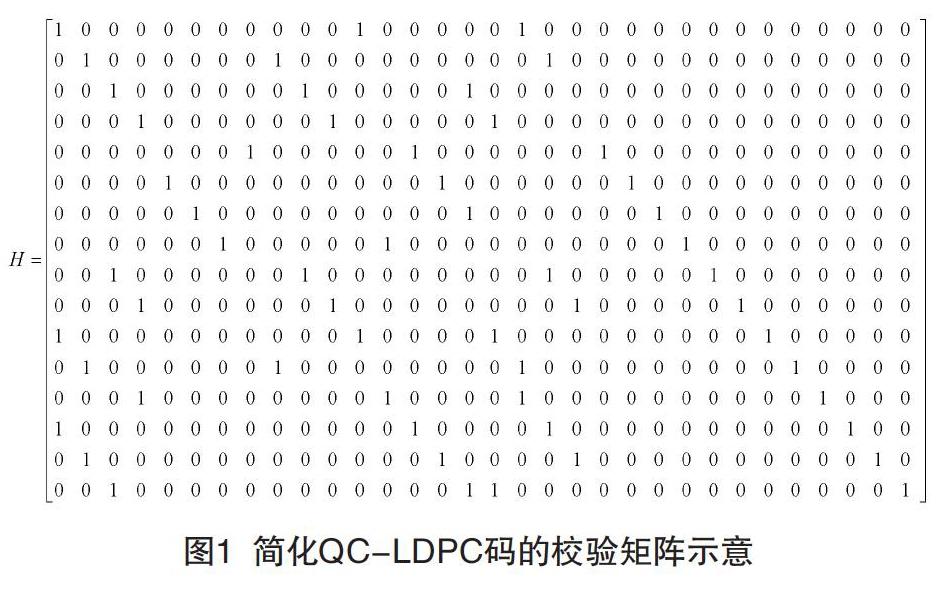

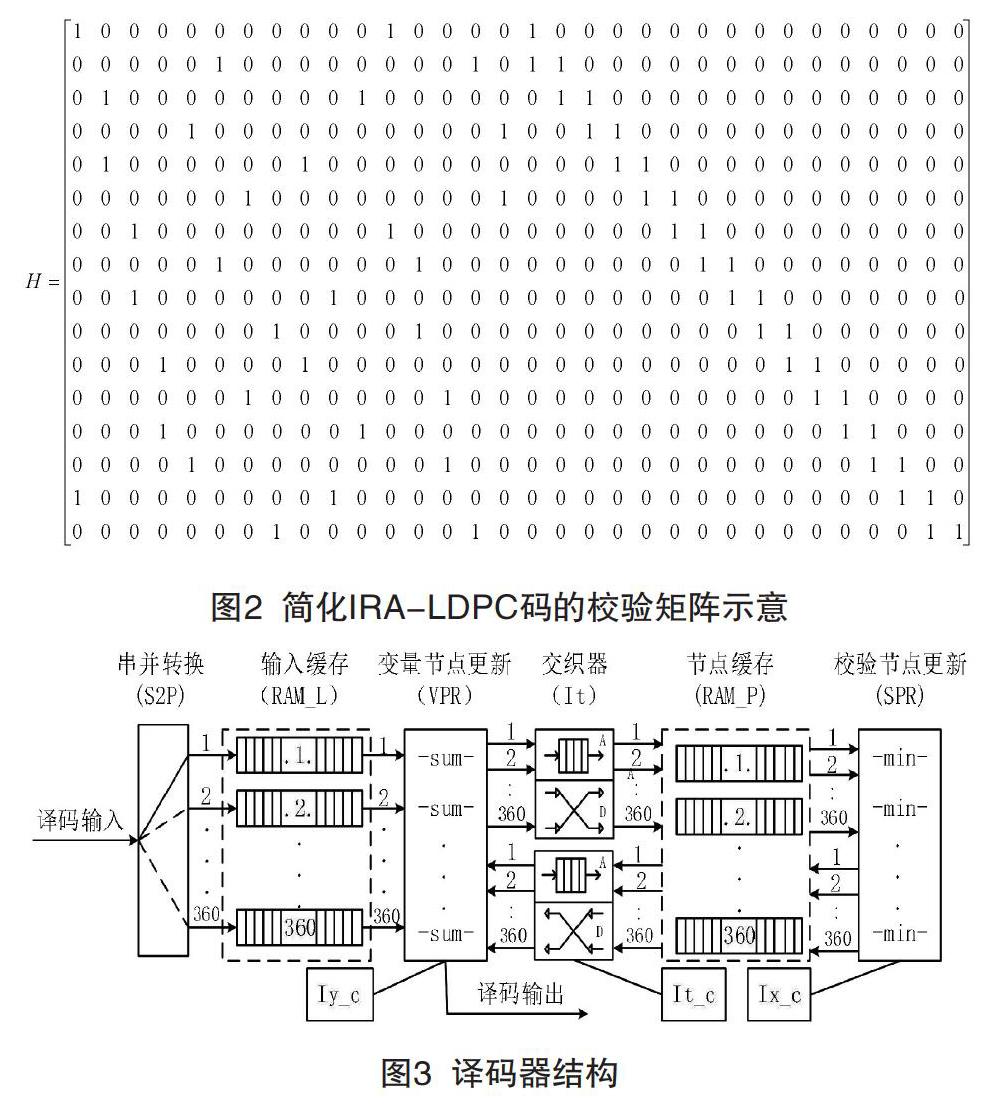

QC-LDPC码是一类具有循环结构特性的LDPC码,将LDPC码的校验矩阵划分成多个子块,每个子块由全零矩阵或非零的、具有循环特性的置换矩阵构成。这种矩阵的特殊性使得QC-LDPC码的编码复杂度为线性,有利于硬件实现,而且码字之间有较大的最小距离。QC-LDPC码H矩阵的表现形式如图1—2所示。

图1为符合地面5G标准规则的QC-LDPC码的简化校验矩阵示意,其中,k=16,n=32,进行4路并行译码,则Zc=4。

图2为符合DVB-S2标准规则的非规则IRA-LDPC码的简化校验矩阵示意,其中,k=16,n=32,进行4路并行译码,则Q=4。

2 译码器结构

本文设计的基于DVB-S2标准的IRA-LDPC码并行译码现场可编程逻辑门阵列(Field Programmable Gate Array,FPGA)实现方法主要包括以下6个部分:串并转换(Serial to Parallel,S2P)、输入缓存(RAM_L)、变量节点更新(VPR)、交织器(It)、节点缓存(RAM_P)和校验节点更新(SPR)。译码器结构如图3所示。

(1)S2P,对串行译码输入进行并行存储控制,前面系统码按顺序分别并行存储至360个输入缓存(RAM_L)中,后面校验码按顺序分别串行存储至360个输入缓存(RAM_L)中。

(2)输入缓存(RAM_L),由360个独立存储器(RAM)组成,单输入单输出,存储译码输入(似然比),每个存储器的存储深度为码长除以360。

(3)变量节点更新(VPR),由360个独立变量节点更新(VPR)模块组成,变量节点每次更新从相应输入缓存(RAM_L)中读取一个数据,从节点缓存(RAM_P)中按Iy_c控制字读取多个数据,按变量节点更新(VPR)规则更新后,再按Iy_c控制字存储至节点缓存(RAM_P)中。

(4)交织器(It),由正交织器(It1)和逆交织器(It2)组成,实现节点缓存(RAM_P)数据的存储地址(列)间交织和360個数据的(列)内循环移位。正交织器(It1)实现节点缓存(RAM_P)数据按It_c控制字规则的列间交织和列内循环移位,并输出至变量节点更新(VPR);逆交织器(It2)实现变量节点更新(VPR)后数据按It_c控制字逆规则的列内循环移位和列间交织,并输出至节点缓存(RAM_P)。

(5)节点缓存(RAM_P),由360个独立存储器组成,双输入双输出,所有存储器都同时按相同地址读取或存储数据,对应存储360路校验节点更新(SPR)之后的中间数据,存储深度为校验矩阵中每个按行块的所有行重之和。

(6)校验节点更新(SPR),由360个独立校验节点更新(SPR)模块组成,校验节点每次更新从节点缓存(RAM_P)中按Ix_c控制字读取多个数据,按校验节点更新(SPR)规则更新后,再按Ix_c控制字存储至节点缓存(RAM_P)中。

(7)Ix_c,Iy_c和It_c控制字,Ix_c为校验节点更新(SPR)控制字,是校验矩阵每个按行块中的每行行重的集合,Iy_c为变量节点更新(VPR)控制字,是校验矩阵按列块中的每块首列列重的集合。It_c为交织器控制字,包括交织器对节点缓存(RAM_P)存取地址的列间交织控制字,和相应地址上读取360路数据后的列内循环移位控制字。

3 译码流程

本文中译码器的译码流程主要由5个部分组成:初始化、译码输入、变量节点更新、校验节点更新和译码输出。

(1)初始化,节点缓存(RAM_P)置零,校验节点更新(SPR)载入Ix_c控制字、变量节点更新(VPR)载入Iy_c控制字和交织器(It)载入It_c控制字。

(2)译码输入,检测译码输入使能有效时,计数器开始计数。前面系统码时,计数器除以360取余作为360个输入缓存(RAM_L)的片选信号,计数器除以360取整作为每个输入缓存(RAM_L)地址信号。后面校验码时,计数器除以Q取余加系统码存储地址偏移后作为每个输入缓存(RAM_L)地址信号,计数器除以Q取整作为360个输入缓存(RAM_L)片选信号。整个码字输入结束后,开始译码,其中变量节点更新和校验节点更新按顺序都执行一次称为一次译码迭代。对于高速连续译码,需要设计乒乓缓存结构进行译码输入数据的缓存。