基于SOPC的视频采集卡设计

涂传亮

摘 要:文章主要介绍了Altera公司的PCI接口IP核的关键要点,阐述视频采集卡的核心技术。由于SDI信号的高速性和实时性,需要传输模块有较高的数据处理能力和较高的控制效率才能保证数據的完整性。该设计采用Altera公司的EP2C20Q240C8芯片和PCI IP核,利用片内双口RAM作为数据缓冲器,通过DMA控制器实现DMA传输控制功能,同时利用SOPC Builder开发平台简单有效地实现了FPGA核心部分的设计,实现上位机对SDI视频信号的接收。

关键词:可编程片上系统;Avalon总线;直接内存存取

由于人们对生活品质的高追求,数字化广播电视技术发展迅速,大容量信息处理成为关键技术,数字电视信号已经普及,要实现这个技术,通过PC接收串行数字接口(Serial Digital Interface,SDI)码流信息,已经成为主流的多媒体数据接收技术。因此,设计基于快速处理平台的SDI码流接收卡设计尤为关键。SDI信号的平均传输速率为270 Mbps,对传输实时性及稳定性要求高,因此本文选择了外设部件互连标准(Peripheral Component Interconnect,PCI)总线进行传输。PCI总线拥有32 bit宽度和33 MH带宽,传输速率最高可达133 Mbps,可很好实现高速和稳定传输。设计选择可编程片上系统(System-on-a-Programmable-Chip,SOPC)Builder(Altera公司内核)来实现PCI接口控制电路。SOPC Builder为PCI接口提供了一个完整的解决办法,内容涵盖了PCI控制电路的全部功能。用户可以利用该平台将各Avalon总线上的设备进行配置,结合直接内存存取(Direct Memory Access,DMA)控制器实现DMA方式的传输,设计外部设备接口逻辑,实现现场可编程门阵列(Field Programmable Gate Array,FPGA)硬件模块功能[1]。

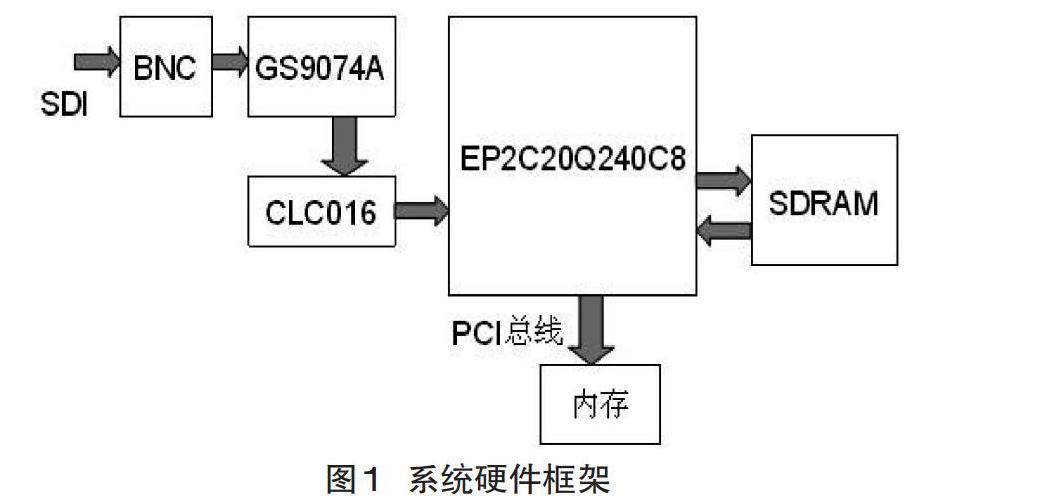

1 系统硬件模块设计

系统的硬件电路设计性能要求传输速率为270 Mbps的串行SDI码流,稳定、实时、无损地通过PCI接口传输到工作站,以供工作站上的应用程序作进一步处理。在操作和使用上要方便,在设计上要求紧凑、简单、可靠、便于升级。系统硬件框架如图1所示。核心部件如下:电缆均衡和时钟提取芯片分别选用GS9074A和CLC016,FPGA芯片EP2C20Q240C8是核心处理器,利用SOPC Builder平台构建基于Avalon总线的SOPC系统结构。另外,FPGA芯片中还包括SDI信号的解码解扰模块、串并转换模块等SDI信号的预处理模块,将串行的SDI信号转换为30 bit的并行信号存入缓存(32 bit PCI总线高两位置零)。

1.1 PCI_MT32功能模块

本设计选定PCI接口模块时,采用了来自Altera的PCI编译器软件包,利用SOPC Builder的调用,可以参数化设置PCI接口的IP核。这个可编译和综合的IP核有以下4种宏功能模块:PCI_MT64,PCI_MT32,PCI_T64和PCI_T32,主要功能是完成总线协议的转换,目的是转换为易于操作的本地接口逻辑,手段是通过复杂的电气和时序要求高的PCI总线逻辑转换,遵循协议2.2版(PCI总线),经过复杂、详实的工业级验证,最终支持多款优化FPGA。其中,PCI_MT32是支持工作频率达到33/66 MHz、最宽达到32 bit PCI总线,在工作模式上支持主/从模式的PCI IP功能模块。考虑到市场的需求,市面通用的工作站主板都支持32 bit PCI,为保障在主模式下DMA控制器工作,该设计选择了PCI_MT32[2]。

1.2 DMA模块

DMA全称是直接存储器访问。在实现DMA传输时,由DMA控制器直接控制PCI总线,CPU将总线控制权交给DMA控制器,这种工作模式下,CPU可以并行、高效地进行其他操作。在非实时操作系统中,DMA工作模式可以极大减轻CPU的压力,提高设备的性能。

本设计使用的是Altera的DMA Controller SOFT IP核。该DMA Controller SOFT IP,通过Avalon总线接口实现批量数据传输,从head地址范围读数据然后向goal地址范围写数据。此DMA控制器有两个Avalon-MM主端口,一个read主端口和一个write主端口,另外还有一个Avalon-MM从端口供系统使用,通过该端口来控制DMA操作。

标准的DMA传输过程包含下列步骤:

(1)系统的CPU通过向DMA的Controller端口write数据来通知DMA Controller准备启动传输。

(2)CPU使能DMA Controller,DMA Controller开始在无需CPU操作的情况下进行数据传输。DMA主write端口从外设或内存head地址中read数据,主write端口向外设或内存的goal地址中write数据。

(3)传输固定宽度的数据,DMA以一个特殊数据作为结束标志。对于可变长度的传输,DMA收到固定的结束包作为数据终点。在传输结束后,如果CPU配置允许,则DMA Controler产生一个中断请求(Interrupt Request,IRQ)。

(4)在传输过程中或传输结束后,CPU检测DMA控制器的状态寄存器来判断此次传输是否在进行或已结束。

对于DMA传输的设置,Avalon-MM主外设通过控制端口改写DMA内置的寄存器来建立和初始化DMA传输。外设可配置项主要有如下几个方面:(1)Read addrss地址设置。(2)Write addrss地址设置。(3)单次传输单位设置:字节(8-bit),半字(16-bit),字(32-bit),双字(64-bit),4字(128-bit)。

1.3 緩存模块

在设计缓存模块时,由于PCI总线上的时钟是66 MHz,而输入的SDI信号是270 Mbps,这就要求对两个频率不同的时钟进行同步。本设计选择双端口随机存取存储器(Dual Port Random Access Memory,DPRAM)作为系统的异步FIFO使用,使其数据输入和输出分别使用不同的时钟,从而实现时钟的隔离和信号的无缝拼接。

不过,SOPC Builder的组件库中并没有支持DPRAM的组件,要在该平台应用DPRAM就必须编写自定义组件。这里的DPRAM接口的一端要连接到Avalon总线上,另一端要作为数据输入接口,且必须作为外部接口使用。DMA控制器是通过Avalon总线与DPRAM进行通信的,DPRAM与DMA控制器通过Avalon总线连接如图2所示。

配置自定义组件各接口信号图。前两项为Avalon总线上的时钟,所不同的是slave_clk66是通过直接挂在Avalon总线上的时钟得到,ex_clk27则是由外接管脚提供,接口类型属于slave型的信号是连接Avalon总线端的DPRAM接口;接口类型属于ex_export型的信号是连接到外接管脚的DPRAM接口[3-4]。

2 设计结果

对生产的SOPC系统进行测试。用通过DMA方式将从外部输入缓存中的信号读入上位机内存。外部输入的信号是彩条SDI信号,而程序中显示接收到的数据,如第一组10 bit数据154-131-3ff-131对应的是第一个彩条的颜色Cb-Y-Cr-Y,对应为红色。再根据其他各组数据与对应的颜色数据进行对比,确定所接收到的数据是彩条信号的数据。

可见,上位机接收到的数据与SDI输入的数据相同,实现了将SDI信号通过PCI总线与PC进行DMA方式传输数据的目的。

3 结语

本设计通过在FPGA芯片中构建基于PCI核的SOPC系统,实现对高速、大容量SDI传输流的实时传输,实现了系统设计的目标。采用DMA方式的传输解放了上位机CPU,极大提高了传输速度。通过自定义组件实现DPRAM在系统中的应用,有效地解决了时钟同步的问题。该FPGA的应用易于在线升级电路,有扩充平台的功能。SOPC系统的使用使硬件电路更为简洁、可靠。经过验证,本系统可以很好地实现SDI信号的接收功能,同时,也可以作为其他信号应用的基础平台,有着良好的应用前景。

[参考文献]

[1]联合开发网.PCI compiler user guide[EB/OL].(2016-03-08)[2019-08-11].http://www.pudn.com/Download/item/id/2927515.html.

[2]李贵山,戚德虎.PCI局部总线开发者指南[M].西安:西安电子科技大学出版社,1997.

[3]纪献永,黄皆雨,冯穗力,等. DVB-ASI信号接收与发送系统的研究[J].电视技术,2004(11):87-88.

[4]夏宇闻.Verilog数字系统设计教程[M].北京:北京航空航天大学出版社,2003.

Abstract:This paper mainly introduces the hardware design scheme and design points of the video capture card of Alteras PCI interface IP core. Due to the high speed and real-time performance of SDI signals, the transmission module needs higher data processing capability and higher control efficiency to ensure data integrity. The design uses Alteras EP2C20Q240C8 chip and PCI IP core, uses on-chip dual-port RAM as data buffer, realizes DMA transfer control function through DMA controller, and realizes the design of FPGA core part simply and effectively by SOPC Builder development platform, to achieve the reception of the SDI video signal by the host computer.

Key words:system-on-a-programmable-chip; Avalon bus; direct memory access