4 Bit 100MS/s 的两步式模数转换器设计

魏一方,田鑫,沈福良,周柯港

(重庆邮电大学,重庆400065)

1 工作原理

两步式模数转换器(Two-Step ADC)[1]的整体结构是两个子ADC 的串联结构,假设两个子ADC 的有效位数分别为N1、N2,则总共需要的比较器为2N1+2N2-2,而相同位数Flash ADC 需要2N1+2N2-1 个比较器,相对而言数目大为减少。输入信号通过底极板采样电路采样后保持稳定,把信号传给第一级子ADC 进行比较,输出的温度计码通过编码电路转换成位二进制码,二进制码通过逻辑选择电路和DAC 电路控制减法电路,确保在保持周期内对稳定的保持信号进行减法操作,把减去的信号输送到第二级ADC 进行位解码。需要延时系统把第一级子ADC 的结果保持到第二级子ADC 的工作时间。最后通过D-触发器延时第一级子ADC 的二进制码和第二级ADC 二级制码组合输出。

图1

图2

2 采样/保持电路(S/H)

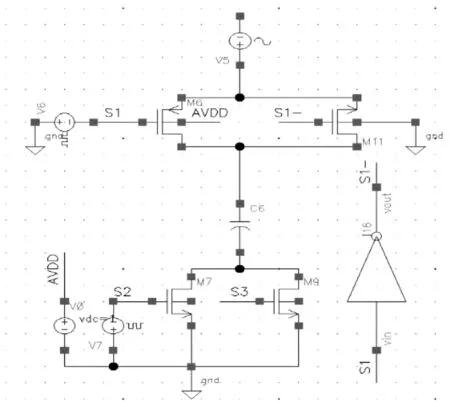

采样/保持电路是整个ADC 最前面的电路,负责把模拟信号采入,由于开关的电荷注入效应,单MOS 采样/保持电路很难达到较高的性能,所以本文中采用PMOS 和NMOS 并联结构。为解决开关的电荷注入效应,可以采用底极板采样技术。底极板采样技术(bottom-plate sampling)指利用开关的导通时间,使电荷注入与输入信号无关,其中涉及控制开关开断则是利用了non-overlap clock 技术[2]。电路如图1 所示。

3 子模数转换器(子ADC)

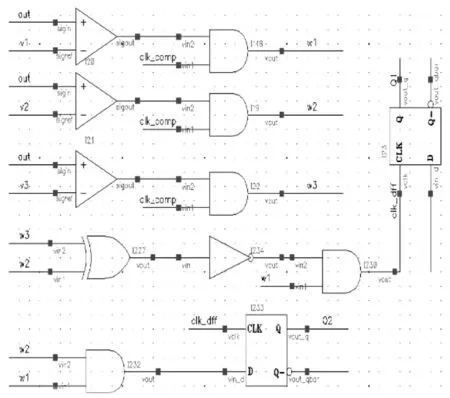

量化电路分为两个部分,比较器和转码器。就比较器而言,多个比较器可以组成得到温度计码,而由于温度计码不能输入DAC 做减法,也无法控制减法器的开关,所以需要把温度计码输入编码电路中转换为二进制码。编码电路由组合逻辑电路组成,如图2 所示。编码过程中,比较器的输入电压和基准电压相差比较小时,会使比较器出现亚稳态状态[3],从而产生数字失真,此问题可以用格雷码解决。

4 选择减法电路

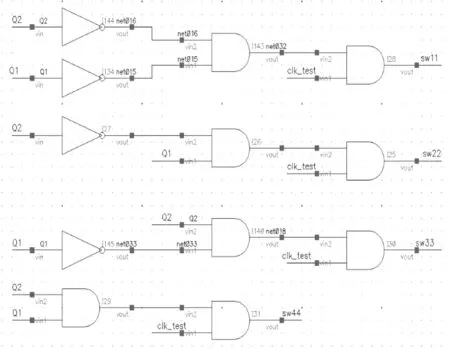

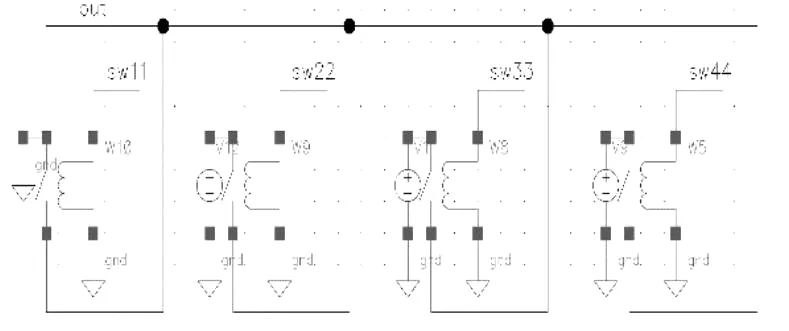

选择减法电路包括开关选择电路和减法电路。开关选择器如图3 所示,其作用是用逻辑组合电路判断第一级子ADC的输出结果,不同的精度要选择不同的减法电路,以4 bit 为例,减法器如图4 所示,其基准电压由一组DAC 确定,分别确定电压为-0.25V、-0.5V 和-0.75V。

图3

图4

5 电路结构

把采样保持电路(S/H)、子模数转换器(Sub-ADC)、选择器(Switch)、减法器(Subtraction)模块化以后其总的电路结构如图5 所示,延时器(Delay)由一组D-触发器组成。

图5

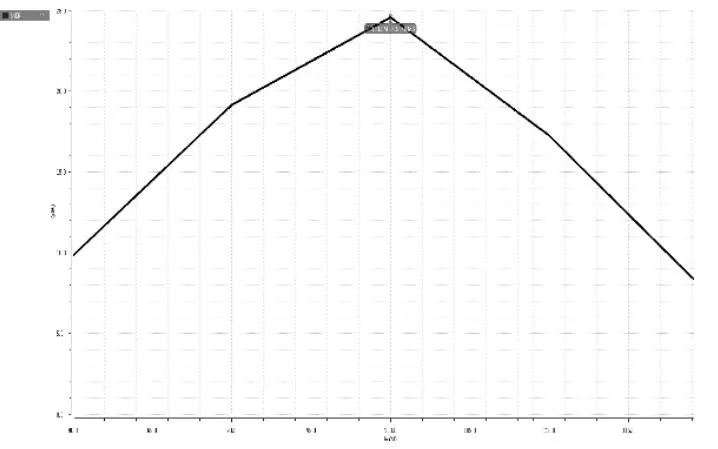

6 仿真结果

在4 bit ADC 的之后加上一个D-触发器可以消除前一级子ADC 的变化对后一级的影响,在输出连接一个理想DAC后可以判断ADC 的SNDR。其输入输出波形如图6 所示。从图7 可以看出,在输入频率是100MHz 时SNDR 为24.5540dB。接近于理想值。

图6

图7

7 结论

本文在65nm CMOS 工艺基础上,设计了一个4 bit Two-Step ADC,在100Mhz 的工作频率下仿真出来的SNDR≈24.5540dB,接近于理想值。在量化过程中运用了少量的比较器,并且把两级ADC 的工作时间分开,所以在功耗和精度方面表现优异。