一种A/D转换电路的设计与应用

吕小凤,杜 丹,张万玉

(1.中国电子科技集团公司第五十四研究所,河北 石家庄 050081;2.陆装驻石家庄地区第一军代室,河北 石家庄 050081;3.陆军装备部装备项目管理中心,北京 100071)

0 引言

模拟数据的采集与处理是信息技术的一个重要分支,广泛应用于地空信息传输系统中。随着信息技术的高速发展和对控制要求的不断提高,地空信息系统对模数转换速度和精度要求也在不断提高[1]。A/D转换芯片作为模拟量采集的核心部件,其内部ADC容易受到输入信号、电路布局以及芯片自身工艺的影响,使转换结果无法满足系统控制要求[2]。受硬件发展水平的限制,传统的地空信息系统中,通常采用单片机对A/D转换芯片进行控制的方式来完成模拟信号的采集和转换,处理速度慢,外围控制通过FPGA完成,硬件电路结构繁杂,软件设计中数据交互同时涉及到单片机和FPGA,可靠性不高。鉴于以上A/D转换发展与应用存在的两大瓶颈:① A/D转换器的速率和性能;② 可编程逻辑器件的处理速度[3],本文利用MAXIM公司具有12位高精度的多通道A/D转换芯片和具有高速数据处理能力的ALTERA公司Stratix系列+5 V工作电压的FPGA作为主控芯片实现了A/D转换,不仅接口简单、转换速度快、精度高[4],而且利用延时调整等技术解决了A/D转换芯片与FPGA之间的高速数据传输问题。

1 A/D采集转换控制电路的设计

1.1 方案设计

设计之初,考虑到应用的可扩展性,要求可对多路模拟数据进行转换,常用的设计方法有2种:① 电路使用多片A/D转换芯片,每片对一路模拟信号进行转换,多片芯片同步工作;② 电路选用多通道A/D转换芯片,通过软件控制依次完成多路模拟信号的转换。

显然,方案1可满足系统的实时性和同步性要求,但是针对目前的系统小型化需求,芯片使用数量多,占电路板空间大,而且外围电路复杂[5],大大增加了PCB设计难度。相较之下,方案2电路简化,虽然对软件控制的要求较高,但应用上更加灵活[6]。

本设计使用的FPGA可编程器件选用ALTERA公司Stratix系列的EP1S20F484I6N,该芯片工作电压为+5 V,A/D转换器选用MAXIM公司的8通道12位高精度MAX197芯片,该芯片仅需+5 V供电,工作电压与EP1S20F484I6N相匹配,二者硬件管脚可以直接相连,不需再使用电平转换芯片,极大简化了电路设计。

1.2 电路实现

本文设计重点是为完成A/D转换的MAX197芯片外围电路提供可靠接口,实现多通道的模拟数据采集转换功能。硬件电路主要由模拟数据接收和控制转换处理电路组成。

为了保证电路的转换精度和可靠性,合理的电路及PCB设计非常重要[7],尤其对于模数混合电路,如何减少模拟电路和数字电路之间的相互串扰,也是要精心考虑的问题[7-8]。

本设计在PCB优化布局和走线的基础上,将数字地和模拟地之间用0 Ω电阻连接,这样可保证直流电位相等,能有效限制环路电流,抑制噪声;否则,模拟信号将会受到干扰,严重影响转换结果。

图1 A/D转换控制处理电路

2 软件设计

软件设计采用Verilog HDL语言利用FPGA编程,通过有限状态机模式[13],实现对MAX197运行模式的配置、模拟数据采集和转换的控制。

程序流程如图2所示。

图2 A/D转换程序流程

在本系统实际应用中,A/D转换只是硬件电路板上FPGA所需完成功能的一部分且数据采集对时间无严格要求。因此,为了保证设计中所用时钟的全局性[14-15],MAX197选择在外部时钟模式下工作,信号获取方式选用时序关系更为简明的内部自动采集模式,模拟信号量程选择0~5 V,则写入的8位控制字为{5’b0,chNum},其中,chNum为模拟通道,数据位宽3 bit,有效范围为3’b000~3’b111,用来表示当前选定的模拟数据通道。

分步状态执行过程如下:

iSt0:初始化A/D转换芯片。nCS,nWR,nRD,HNEN信号置1,数据读写使能triEn置0;

iSt1:nCS信号置0,拉低片选信号;

iSt2:nWR信号置0,拉低写信号,准备产生写信号的上升沿;

iSt3:数据读写使能triEn置1,并按控制字格式编排数据准备写入数据总线,数据内容为{5’b0,chNum};

iSt4:nWR信号置1,拉高写控制信号,产生上升沿,此时,数据读写使能triEn有效,将控制字写入数据总线配置A/D转换芯片MAX197的运行模式,同时控制字中选定的模拟输入通道上的数据开始进行采集;

iSt5:数据读写使能triEn置0,并将nCS信号置1,拉高片选信号,不再对数据总线进行操作,同时等待模拟数据采集转换完成。当检测到nINT信号为低电平时,表示模拟数据已转换完成,转换结果已在数据总线上等待读出[16],否则,继续等待;

iSt6:nCS信号置0,使片选信号有效;

iSt7:nRD信号置0,拉低读控制信号,准备从数据总线上读取转换结果;

iSt8:HNEN信号从状态iSt0时一直为高电平,此时读控制有效,从数据总线上读取转换结果的高4 bit,当从总线上开始读取转换结果时,转换结束标识信号nINT恢复高电平,等待下一次转换;

iSt9:HNEN信号置0,准备读取转换结果的低8 bit;

iSt10: HNEN信号为低电平且读控制有效,从数据总线上读取转换结果的低8 bit;

iSt11:12 bit转换结果已全部从数据总线上读出,nRD信号置1,拉高读控制信号,不再对数据总线进行读操作,同时,HNEN信号置1,恢复到初始态;

iSt12:nCS信号置1,拉高片选信号,使片选信号无效,使所有控制和状态信号都恢复到初始态。

当所有控制和状态信号都恢复到初始态值时,表示对当前模拟通道的转换操作已全部完成,状态机跳转到iSt0,开始进行下一通道转换操作,以此循环8次,可实现8个模拟通道的顺序转换。开启新一轮的转换时,当模拟通道的信号量程、极性有变或需改变芯片的运行模式时,需按格式对控制字进行重新设置。如果在当前转换周期未结束时写一个新的控制字将使当前转换失效,并启动一次新的采集转换过程[17]。

3 系统仿真

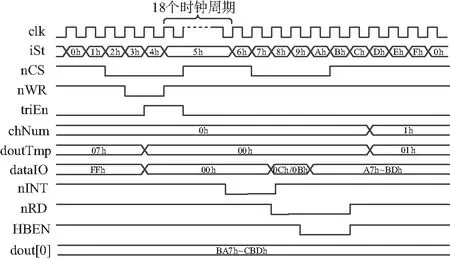

在Quartus II开发平台上,用Verilog语言进行程序设计,并用Quartus II软件的嵌入式逻辑分析仪Signal Tap II通过JTAG端口来查看以实际系统速率运行的系统内的各设计节点,从而实现对FPGA设计内部节点的访问。本设计的主时钟将外部晶振从FPGA芯片的全局时钟管脚输入,使用Alter公司的PLL内置模块对输入的外部时钟倍频[18],对高频钟分频后为MAX197提供1 MHz时钟。在模拟通道1上接入+5 V电压,数据采集转换时序如图3所示。

图3 通道1数据采集转换时序

图3中,clk是外部时钟模式下由外部晶振为MAX197芯片提供的时钟;iSt为状态机;doutTmp为FPGA内部寄存器,存储设置的控制字;dataIO为MAX197与FPGA交互的8 bit并行数据线;当nCS有效,nWR为低电平时,triEN使能将寄存器内的数写入数据线,初始化控制字。dout[i]为转换结果。软件设计中,所有赋值操作使用的都是非阻塞型过程赋值,则对应的状态机中,每一次信号的赋值要到下一个时钟周期来临时才会执行。通过时序图可以看到,在状态机iSt为4时,设置好的控制字写入了数据总线dataIO,配置好MAX197转换芯片的运行模式,并选定当前需转换的模拟通道为通道1。状态机iSt为5时,nWR的上升沿到来,开始采集信号,经过18个时钟周期,信号采集并转换完成;此时,转换结束标识信号nINT变为低电平,并开始向数据线上准备转换结果。状态机iSt为8时,nRD为低电平,开始从数据线上读取转换结果,nINT恢复为高电平等待下一次转换过程。dout[0]显示模拟通道1上+5 V的电平信号转换结果不稳定,数值一直在12’hBA7~12’hCBD间不停跳动,换算成电平值则为3.63~3.98 V。说明每次对+5 V电平采样时,采样到的电平值不稳定且数值偏差很大,模拟信号受到了严重干扰。检查电路布线,发现模拟地与数字地间未做等电位处理,可能造成模拟信号不能正确识别。将MAX197芯片的第28管脚和15管脚直接短接,并在模拟通道1上通过直流可调电源接入+5 V电压,模拟通道2上接入约+2.5 V电压,数据采集转换时序如图4和图5所示。

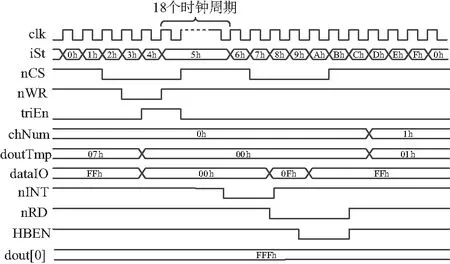

图4 优化后通道1数据采集转换时序

从图4转换结果可以看出,电路经初步优化后,+5 V电平的转换结果稳定,且转换值12’hFFF正确。

图5 优化后通道2数据采集转换时序

通道1转换完成后在转换周期结束前,通道号加1,准备进行通道2的数据转换。图5中,在新一轮转换周期中,chNum值由0变为1,表示当前选定模拟通道2,转换芯片的运行模式没有改变,此时,控制字doutTmp设置为’h01,dout[1]显示模拟通道2上+2.5 V的电平信号转换结果为12’h7FD~12’h7FF。

结合图4和图5,模拟信号经初步抗干扰优化处理后,+5 V,+2.5 V信号转换结果正确且稳定,芯片A/D采集转换功能正常。

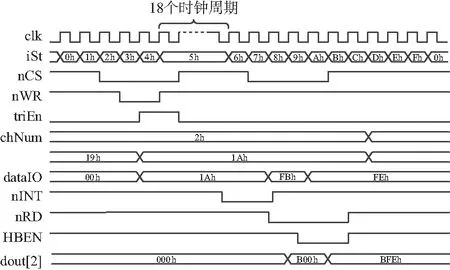

为测试软件的通用性,改变模拟通道信号量程和极性,将模拟通道3上信号量程设置为±10 V,并将通道3接入稳定-5 V电压,数据采集转换结果如图6所示。

图6 通道3数据采集转换时序

图6中,由于通道3信号量程改变,在进行数据采集转换前,控制字doutTmp应设置为{5’b11,3’b10},表示当前选定模拟通道3,且信号量程为±10 V,dout[2]显示模拟通道3上-5 V的电平信号转换结果为12’hBFE,转换结果与实际相符,芯片A/D采集转换功能依旧正常。

4 系统测试

在实际地空信息系统特定功能机箱内,将重新优化设计后的电路板与功放模块连接,模块反馈的模拟电压作为A/D转换电路的输入信号来检测硬件电路及软件的实用性。在数据转换测试中,通过功能机箱上的状态显示屏可查看12 bit A/D转换结果。调节反馈电压,当电压值为单极性且在0~+5 V间变化时,转换结果在12’h000~12’hFFF间变化。调节反馈电压分别稳定至+3.0 V,+2.5 V时,使用3块电路板进行测试,转换结果如表1所示。

表1 A/D转换测试结果

电路板序号模块反馈电压/V芯片模拟信号输入端电压/V测试结果转换值/V13.00002.999412’H9972.997623.00002.999712’H9982.998833.00002.999912’H9993.000012.50002.499212’H7FD2.496922.50002.499612’H7FE2.498232.50002.499912’H7FF2.4994

5 结束语

MAX197的采样精度和其时序密切相关,本设计电路使用FPGA做主控芯片,处理速度快,通过表1的测试数据,对3块不同的电路板灌装本设计软件后,误差均不超过3 mV,转换精度高,且多通道转换模式和数据处理通过FPGA编程控制,在硬件电路不变的情况下修改软件程序就能满足多种数据采集需求[19]。该设计已应用到实际的地空信息系统中,具有一定的实用价值,同时由于该设计采用Verilog语言完成电路的软件设计,易用性和可移植性得到了加强,不仅使硬件功能的设计修改和产品升级变得十分方便,而且极大地提高了电子系统的灵活性和通用性。结合图3~图5的实验数据,设计还强调了模数混合电路设计中信号抗干扰处理的重要性,具有一定的学习参考价值。