汽车事件数据记录系统硬件电路设计与开发

汤自宁,刘全周,李占旗,张 蕾,陈 正

(中国汽车技术研究中心有限公司 汽车工程研究院,天津 300300)

1 引言

众所周知,在飞机中有专门记录飞行数据的黑匣子[1],而在汽车中也有相应的电子零部件来记录汽车的行驶数据,尤其是当发生事故时,可以用来分析相应的事件数据。至今EDR技术已经发展了40多年,从1970年美国高速公路交通安全局 (NHTSA)声明要开发机动车碰撞记录仪起,国外汽车生产商开始在气囊控制模块中安装一个小型存储器,这便是EDR的雏形[2]。直到2006年NHTSA发布了EDR的定义和强制EDR标准49 CFR Part 563,并要求2012年9月1日及以后生产销售于美国本土的车辆必须遵守该规定[3],欧盟、日本也相继颁布相关规范。中国在2017年中国国家标准化管理委员会 (SAC)发布的《机动车运行安全技术条件》(GB7258-2017)中规定:“8.6.6乘用车应配备能记录碰撞等特定事件发生时的车辆行驶速度、制动状态等数据信息的事件数据记录系统 (EDR)”[4],也就是说,国家已经强制规定后续生产的车辆应具备事件数据记录系统 (EDR)。目前我国对汽车事故数据记录仪 (EDR)标准制定工作正在进行中,会对EDR的设计、制造、安装、检验及使用提出强制性要求。EDR将会作为一种法规性产品,必将成为国内车辆的标准安全配置。

目前EDR功能多被集成到安全气囊控制器 (SRS)中,着眼未来,随着自动驾驶技术和车联网功能的发展,以后车辆需要记录的数据会越来越多,所以需要有一个专门的电子控制器用来记录车辆的事件数据。本文从EDR功能要求出发,跟随国内外标准相关要求和市场需求,进行了独立的EDR电子控制器的硬件电路设计开发,并阐述了EDR的工作原理及控制存储单元各个模块的功能与电路设计。

2 EDR系统总体结构

汽车事故数据记录仪 (Event Data Recorder,EDR)是用来监测、记录、存储事故前后汽车行驶状态数据的装置[5],其所记录的数据均来自CAN总线、传感器以及自身内部计算信号,旨在事故发生后提取数据,可作为事故分析、事故鉴定、品质鉴定的重要依据。EDR系统由碰撞传感器、控制存储单元、数据提取工具、数据分析软件等部分构成。各部分之间的关系如图1所示。

3 EDR系统硬件电路总体设计

3.1 EDR控制存储单元功能需求

控制存储单元是EDR系统的核心构成部分,其通过CAN总线与整车总线网络相连,当条件满足时,实现车辆状态及驾驶员操作等信息的记录与存储,且控制存储单元支持提取工具的连接与数据提取。EDR控制存储单元应当满足以下基本功能需求。

图1 EDR系统总体结构

1)上电后监测车辆加速度变化,当碰撞发生时应自动触发记录事故前后车辆状态信息。

2)当达到锁定阈值时,EDR控制存储单元所记录的事故数据不可被擦除、覆盖。

3)由于事故导致车辆发生断电时,EDR控制存储单元应具备断电保护功能,完整记录本次事故数据。

4)EDR控制存储单元应支持UDS诊断协议,满足ISO 14229-1,ISO15765-2要求。

5)EDR系统存储的数据应支持标准车载提取 (SAEJ1962诊断连接器)与非车载提取。

3.2 EDR控制存储单元硬件方案设计

根据上述EDR控制存储单元的功能需求,其硬件结构主要由数据触发采集单元 (传感器单元)、控制单元 (微控制器单元)和外围电路3部分组成,其中外围电路包括电源电路、CAN通信以及断电保护电路等,EDR硬件结构框图如图2所示。

图2 EDR硬件结构示意图

4 EDR硬件功能模块组成及工作原理

4.1 数据触发采集单元

数据触发采集单元由板上加速度传感器和外围加速度传感器两部分组成,通过阈值计算,触发微控制器进行数据采集。板上加速度传感器与微控制器通过SPI接口连接;外围加速度传感器的数据采集由微控制器和PSI5接口电路芯片ELMOS公司的E521.40A共同完成。采用双传感器的逻辑算法冗余方案来保证数据触发的可靠性。

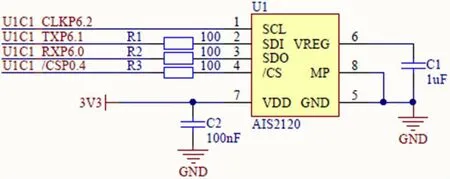

板上加速度传感器选用意法半导体 (ST)公司的AIS2120SX双通道加速度传感器,其具有±120g量程,完全独立的X和Y方向感应方向,14位精度的加速度数据输出,并集成可编程的数字低通滤波器与快速和慢速动态零点修正功能,可以满足碰撞工况下加速度准确检测[6]。AIS2120SX还具备兼容的SPI接口,且工作环境温度宽达-40°C~105°C,可确保EDR在车辆运行中各种环境变化及气候影响时可以正常工作。AIS2120SX通过SPI串行总线与微控制器连接,还可应用于安全气囊控制器开发设计中,其电路原理图如图3所示。

图3 板上加速度传感器原理图

4.2 微控制器单元

微控制器单元是EDR硬件设计的核心部分,根据EDR硬件设计方案的功能需求,最多情况下需要处理2路SPI接口加速度传感器信号;当加速度变化量达到触发阈值后,微控制器从车辆高速CAN总线采集所需的车辆状态信息,连同加速度信息,存储于自身RAM存储器,并锁定于片上Flash存储器中,这就需要控制单元具有较快的处理速度和较大的RAM和Flash空间,且支持标准车载提取与非车载提取;微控制器还需采集外界点火信号,并在碰撞发生时输出点火驱动信号。同时还要考虑微控制单元的可靠性要求。

综合上述多方面考虑,选用英飞凌 (Infineon)公司的SAK-XC2267M-104F80LR AB微控制芯片。XC2267M最高工作频率为80MHz,中断源多达96个,最快采样率达到12.5ns[7],满足EDR处理速度要求;存储器模块包括16KB片上PSRAM、16KB片上DSRAM以及高达832KB片上Flash程序存储器,充分满足EDR数据存储空间要求;同时配置8个通用串行通道,支持外围适配SPI、I2C等多种串行协议芯片,以及6路高速CAN通信接口、2路A/D接口与若干I/O,符合与其他模块间的外部接口需求;是一款具有-40°C~125°C的宽工作温度范围、高可靠性的符合EDR硬件功能需求的微控制芯片。

4.3 外围电路模块

4.3.1 电源模块

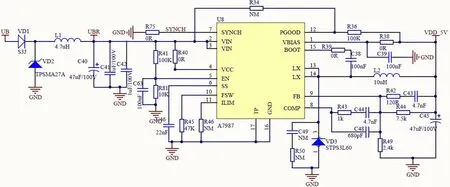

电源模块主要为EDR系统的硬件电路提供电源,其可靠性和稳定性直接响着EDR硬件电路的性能。EDR系统输入电压源为车辆蓄电池,由于蓄电池输出主要为+12V和+24V,所以EDR电源模块设计需要满足兼容+12V~+24V输入电压。由于微控制芯片与CAN收发器需要电压源为5V,而加速度传感器与PSI5接口芯片需要电压源为3.3V,则需要在电源模块设计中,分别选用5V和3.3V降压芯片与降压电路进行电源模块设计[8]。

选用意法半导体 (ST)公司的A7987作为5V降压芯片,将EDR输入电压源首先经过保护电路,然后经过芯片A7987的降压电路,转换成+5V电压源,降压电路如图4所示。A7987是专业汽车级的电源转换芯片,其电压输入可达4.5V~61V的宽电压输入范围,连续输出直流电可达3A,可满足工作环境较复杂,供电电压变化较大的情况。该降压电路的设计同时考虑了防反接保护、浪涌抑制等方面[9]。防反接方面选用二极管保护电路VD1,浪涌抑制方面则使用电容元件来抑制电源电压上的各种浪涌波形和静电,同时降压转换电路中采用稳压管抑制电压上升,从而避免休眠时电流过大导致逻辑芯片损坏。

图4 A7987降压电路原理图

同样选用ST公司的LDK130低压降稳压芯片将5V输入电压转化为稳定的3.3V电压,转换电路如图5所示。LDK130输入电压范围在1.9~5.5V内,同时具备广泛的0.8~3.5V固定输出电压范围,且拥有低压差、低静电电流、低噪声、短路常数限流和热保护的特点,充分符合EDR电源模块设计需求。A7987与LDK130的工作环境温度均为-40℃~125℃,可靠性较高。

4.3.2 CAN通信模块

当达到触发阈值后,EDR控制存储单元需要采集车辆高速CAN上运行状态与驾驶员操作信息并进行存储,还要求CAN接口支持故障诊断功能。由于主控制芯片XC2267M内部的CAN通信模块可以完成数据链路层连接,所以CAN接口的硬件设计只需要选择一个CAN接口收发芯片,来完成物理信号的转换即可。

图5 LDK130转换电路原理图

采用恩智浦半导体 (NXP)公司的TJA1042T/CM作为CAN接口芯片。TJA1042作为专为汽车电子控制系统通信所设计的高速CAN收发器,传输速率最高可达1Mbit/s,同时具有很好的电磁干扰耐受能力与抗静电放电 (ESD)性能,符合ISO 11898标准[10]。设计过程中采用共模电感、滤波电容等技术,更加保证硬件可靠性,设计电路如图6所示。

图6 CAN收发器电路原理图

4.3.3 断电保护模块

当碰撞发生导致蓄电池供电断开时,EDR控制存储单元无法正常工作会导致事故数据无法被记录并存储,这就需要设计断电保护模块。EDR采用超级电容作为备用电源,当蓄电池掉电后,微控制器及CAN收发器等系统的所有供电需求均由超级电容完成。同时超级电容作为储能元件,上电后5V电压源为微控制器供电的同时,也给超级电容进行充电。

根据EDR数据存储要求,计算所需超级电容大小。若设定为恒电流,即超级电容工况中的电流和持续时间一定的情况下,设置工作起始电压Uwork=5V,工作截至电压Umin=4.2V,工作时间t=10s(TBD),工作电源I=100mA (TBD),所需电容容量为1.25F,若设定电容量允许偏差为±20%,则可选用容量为5.5V1.5F的超级电容。选用AVX公司的SCMR22D155 MRBB0超级电容作为备用电源,断电保护电路设计如图7所示。

图7 断电保护电路原理图

5 硬件系统集成

对上述各功能模块进行系统集成设计,PCB设计采用2层板结构,以微控制单元为中心进行模块化设计,最终完成了EDR硬件电路设计,电路板如图8所示。经调试,该硬件电路符合EDR硬件控制存储单元的功能需求。

6 结束语

本文基于EDR系统功能原理,阐述了EDR控制存储单元的功能需求,并介绍了EDR硬件电路总体设计方案与各个模块的功能及电路设计。采用模块化的电路设计思路不仅提高了系统标准化,而且具有良好的可靠性和经济性。独立的EDR系统将为划分汽车厂商和驾乘人员的事故责任、实施医疗救助、进行保险理赔、安全性研究等提供数据支持,具有重要意义。

图8 EDR硬件电路板设计