一种新颖的低功耗低相位噪声VCO设计

罗 永 刚

(山东理工大学 电气与电子工程学院,山东 淄博 255049)

0 引言

使用无线平台的工业通信系统十年来一直是非常有前途的领域[1-2]。对于蓝牙、物联网和WiFi标准应用,频率合成器需要生成2.4~2.48 GHz频段的信道频率,因此,压控振荡器(VCO)的调谐范围不可低于80 MHz。在无线收发器的帮助下,用于发送和接收数据的无线传感器节点通常使用电池能量来操作,但频繁更换系统中电池则增加了监控难度及人力、物力等成本。VCO是收发器中耗电量较大的一个模块,因此在保持性能指标良好的同时,需要降低VCO的功耗。

在频率2.4 GHz处已相继出现了多款VCO文献的报道。虽然文献[3]、[4]都取得了较低的相位噪声,但却以增加功耗为代价。文献[5]采用倍频技术,基于180 nm CMOS工艺设计了一款较低功耗的VCO,由于相位噪声较差,致使VCO的品质因数仅为160 dBc/Hz。文献[6]报道了一款使用PMOS二极管实现的VCO,其取得了-113.4 dBc/Hz@1 MHz的相位噪声,但功耗较大。从上述结果可以看出,相位噪声随着功耗的增加而得到改善,因此,需要一种新的VCO架构来降低其相位噪声,且急需低功率VCO的合理解决方案。本文研究了传统的LC-VCO结构,并对结果进行了研究。比较了传统的VCO功耗性能折衷,并在此基础上提出了一种全新的CMOS VCO电路结构。

1 压控振荡器

交叉耦合LC振荡器是锁相环中的重要组成部分,已广泛用于接收器和发射器中。下面给出了3种可能的基本VCO架构:

1) 仅采用NMOS器件设计的NMOS VCO。

2) 仅采用PMOS器件设计的PMOS VCO。

3) 采用CMOS器件设计的CMOS VCO。

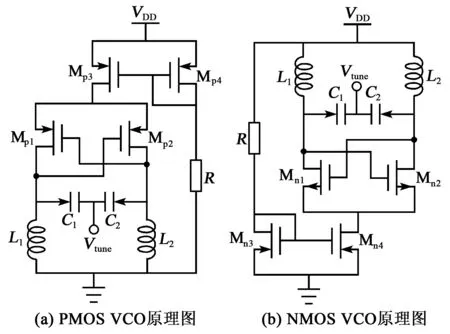

图1分别给出了PMOS VCO和NMOS VCO的原理图。图中形成LC谐振回路的电感和可变电容必须从两侧对称,以确保电路差分工作。当差分信号施加在如图2(a)所示的交叉耦合电路中时,产生差分负电阻,补偿能量损耗。

图1 PMOS VCO和NMOS VCO原理图

图2 交叉耦合NMOS电路以及小信号模型

图2(b)中,节点1、2处的电流分别为

(1)

(2)

式中:v为加在晶体管Mn1漏极和Mn2漏极之间的电压;rds1和rds2分别为晶体管Mn1和Mn2的漏源极间电压;gm1和gm2分别为晶体管Mn1和Mn2的小信号跨导。

由于在电路设计中两个NMOS器件完全相同,故有:

gm1=gm2=gm

(3)

rds1=rds2=rds

(4)

(5)

由于两个NMOS晶体管交叉耦合相接,因此,两个NMOS晶体管的等效跨导gmNMOS为

(6)

由图3(a)可见,两个交叉耦合结构并联连接,与仅NMOS或PMOS VCO相比,其电路的总跨导加倍。CMOS VCO的有效跨导gmCMOS为

(7)

图3 本文提出的VCO与传统VCO的比较图

由图3(b)可见,在努力使功耗最小化的同时,改善了VCO的相位噪声性能。在该电路中,除了简单的互补MOS结构外,还增加了级联的交叉耦合PMOS(Mp3和Mp4)结构,以最大限度地降低电路功耗对于外部偏置电流的依赖性。VCO核心需要偏置电流来获得所需的跨导,并最大限度地降低器件和工艺变化对电路性能的影响,但外部偏置电流会增加功耗并降低VCO的相位噪声。由于本文在所提出的CMOS架构中连接了额外的交叉耦合PMOS(Mp3和Mp4),故而提出的CMOS VCO的总跨导为

(8)

对于相同大小的偏置电流,与NMOS或仅PMOS拓扑相比,所提出的CMOS VCO的跨导提高了3倍。因此,与传统的CMOS VCO相比,所提出的CMOS VCO只需较少的外部偏置电流便可产生更高的跨导,因而可以消耗更低的功耗。所提出的VCO在功耗、相位噪声和交叉耦合晶体管的开关能力方面表现出了较优的性能。

在所提出的架构中,为了降低PMOS的栅极电阻,设计中使用多指MOSFET,通过将晶体管Mp5和Mp6并联连接到Mp3和Mp4来实现多指MOSFET设计。将Mp3、Mp4、Mp5和Mp6设置成相同的尺寸以获得最小电阻,从而更好地匹配MOSFET。在MOSFET中栅极电阻直接导致热噪声,并会降低VCO的相位噪声性能,因此,通过降低栅极电阻的方式,所提出的电路进一步优化了电路的相位噪声。噪声的频谱非常大,在工作频率范围内总是存在噪声电压分量,该噪声电压充当电路所需的触发电压。Mn3和Mn4相连接,组成电路的电流镜拓扑结构,基于Mn5实现的二极管充当连接负载,其电阻值等于1/gm。Mn4晶体管尺寸的宽长比是Mn3晶体管的3倍,这使得Mn4分支中的电流是Mn3和Mn5分支中电流的3倍;同时,在设计中添加的Mn3和Mn4增加了电路的电流驱动能力。当耦合的MOSFET对获得的差分负电阻值高于无源电感的寄生电阻时,CMOS VCO开启振荡。在该设计中,可变电容由PMOS晶体管实现,选择MOS电容和电感的大小以获得所需的振荡频率和调谐范围。所提出的电路以这样的方式偏置,可以降低所需的偏置电流,由此降低了功耗。

2 实验结果与分析

采用TSMC 0.18 μm RF CMOS工艺对本文所提出的新颖的CMOS VCO进行设计,电路仿真以及版图绘画工作均在Cadence软件中完成。芯片流片工作采用MPW服务实现,图4为流片实现的VCO芯片照片,其不包含焊盘的芯片(大小为520 μm×340 μm)。芯片在1.8 V供电电压下,仅消耗了2.9 mW的功耗。

图4 VCO芯片照片

图5为振荡频率的测试结果,其中调谐电压在0~1.8 V变化,所提出的VCO振荡频率为2.522~2.378 GHz,覆盖了蓝牙、物联网和WiFi等标准应用系统的2.4~2.48 GHz的频段。在振荡频率2.45 GHz处,对VCO的相位噪声进行了测试,测试结果如图6所示。由图可见,该VCO取得了-124.3 dBc/Hz@1 MHz的相位噪声。

图5 振荡频率测试结果

图6 相位噪声测试结果

为了验证所提出结构的优越性,在相同的调谐电压下,仿真对比了PMOS VCO、NMOS VCO、传统的CMOS VCO及本文提出的电路的功耗和在1 MHz下的相位噪声,其结果如图7所示。由图可见,在相同的功耗消耗下,本文提出的CMOS VCO取得了最优的相位噪声特性。为了实现相同的相位噪声,与提出的CMOS VCO相比,NMOS VCO、PMOS VCO和传统的CMOS VCO需要消耗更多的功耗。

图7 功耗对相位噪声影响

表1为仿真结果与测试结果的对比情况。由表可见,仿真结果与测试结果基本一致。在振荡频率和功耗两方面,仿真结果能表征电路的实测特性;在相位噪声方面,与仿真结果相比,测试结果性能略差,比仿真结果高了5.1 dB,分析其原因主要有:

1) 所采用的CMOS器件噪声模型精确度不够。

2) 由于工艺稳定性的因素,仿真结果中用到的衬底参数的设置很难与实际的保持完全一致。

表1 VCO测试与仿真结果比较

为了使仿真得到的相位噪声能够更好地与实测结果一致,可以进一步地优化CMOS器件的噪声模型,并根据工艺的实际情况,在仿真过程中对衬底参数作进一步地优化调整,以便更好地模拟工艺过程中的衬底特性。

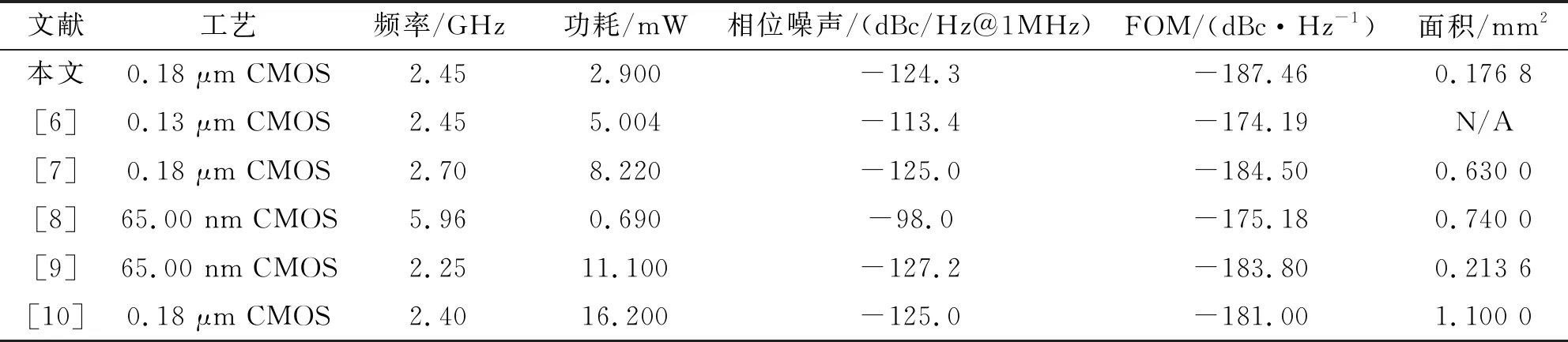

为了验证本文所提出VCO电路理论的合理性及先进性,表2为射频VCO的比较结果[6-10]。为了便于比较,采用由下式计算得到的品质因数作为FOM指标。由表可见,本文设计的VCO取得了最优的FOM特性,且所占据的芯片面积最小。

(9)

式中:P为VCO的相位噪声;fosc为中心振荡频率;Δf为偏移频率;PVCO为VCO的功耗。

表2 射频VCO比较结果

3 结束语

本文针对2.4 GHz ISM频段RF应用提出了新的CMOS VCO架构。从理论分析中研究了传统VCO架构和提出的CMOS VCO架构的性能。将本文提出的VCO的结果与传统LC VCO的性能进行了比较,结果表明,本文提出的VCO可在相同的功耗消耗下实现更优的相位噪声特性。芯片实测结果表明,本文提出设计的VCO在仅消耗了2.9 mW的功耗下,取得了-124.3 dBc/Hz@1 MHz的相位噪声。与功耗值小于3 mW的其他架构相比,本文提出的电路结构设计性能更好。