一种基于DDS的中频模拟电路设计

郝朝亮 软会英 侯光梁

摘要:介绍一种基于DDS芯片JS9854的雷达中频模拟电路,以AT91RM9200处理器为核心,以JS9854频率合成芯片为模拟信号产生器,可产生常规脉冲、相位编码、线性调频等多种不同调制方式的雷达中频回波,输出一组频率可调的模拟中频回波信号,可用于多普勒测速雷达信号数据处理分机的自检测试。

关键词: DDS 信号模拟器 自检测试

引言

直接数字频率合成技术(Direct Digital Synthesis,DDS)是20世纪80年代初发展起来的一种新的波形产生方法,具有体积小、功耗低、频率分辨率高、易于编程控制等优点,被广泛应用于电子对抗、雷达、通信等领域。近年来,基于DDS的中频模拟电路设计得到越来越多的研究和应用,为雷达研制、算法验证和故障检测等方面提供了很大的便利。本文介绍一种基于DDS芯片JS9854的雷达中频模拟电路,可产生常规脉冲、相位编码、线性调频等多种不同调制方式的雷达中频回波,输出一组频率可调的模拟中频回波信号,可用于多普勒测速雷达信号数据处理分机的自检测试,并已装备部分多普勒测速雷达,取得了良好的效果。

1 DDS技术原理

直接数字频率合成技术将数字信号处理理论引入频率合成领域,图1是DDS的技术原理图,系统由时序控制器、相位累加器、波形ROM、D/A转换器和低通滤波器组成。在参考时钟的控制下,相位累加器对频率控制字进行线性累加,得到的相位码对波形存储器寻址,使之输出相应的幅度码,经过数模转换器得到相应的阶梯波,最后经过低通滤波器得到连续变化的所需频率的波形。

2 中频模拟电路设计

模拟电路以AT91RM9200处理器为核心,以JS9854频率合成芯片为模拟信号产生器,产生一组模拟中频回波信号,通过滤波电路滤波以后以SMA接口形式进行输出。

2.1 系统电路设计

处理器选型为AT91RM9200,这是ATMEL公司推出的一款基于ARM920TTM核的微控制器,具有丰富的资源和外设接口,便于实现信息的处理和控制。

DDS芯片选型为中国电科58所的国产DDS芯片JS9854,JS9854内含一个DDS核(包含相位累加器、相位/幅度转换)、两个反正弦滤波器、两个12位数字乘法器、一个可编程PLL倍频器、一个高速比较器和两个12位高速高性能的正交D/A转换器。提供一个精确的参考时钟时,该电路能产生可以调频、调幅、调相位的两路正交正余弦波形,能够被广泛应用于通讯、雷达等领域中。这款DDS与ADI公司的AD9854在电路上完全兼容,最高支持到300MHz的工作频率,支持产生从直流到150MHz的宽频输出信号,其频率控制字的位数为48位,因此产生的信号具有很高的频率分辨率。

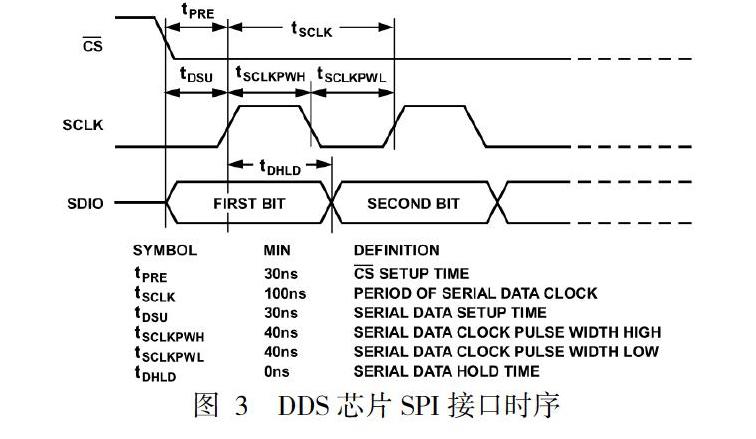

DDS的设计电路图如下图2所示。采用AT91RM9200的SPI口对DDS进行配置以及频率控制字的输入等,采用GPIO口为DDS提供硬件复位及工作模式选择等。22脚为SPI接口的片选信号,低电平有效;21脚为串行时钟信号,数据被寄存在时钟上升沿上;19脚为SDIO,在串行通信模式时作为双向数据输入/输出口,本设计中配置为数据输入口;18脚为SDO,在串行通信模式中为数据输出口;71脚为芯片复位信号,对芯片进行初始化配置。

69脚为单端参考时钟输入,设计采用雷达整机中Ku波段接收组件产生的40MHz时钟作为雷达系统工作时钟,系统时钟输入到DDS芯片的69脚作为DDS芯片工作时钟。

本设计中输出信号为10MHz±2.2KHz和10MHz±2.8KHz,采用串联三级82nH、120nH和120nH电感的方式来构成带通滤波器,滤掉高频和低频杂波信号。由于DDS芯片产生的低频杂波较多,所以另加七个电容来更好的消除低频杂波信号。

2.2 系统电源设计

本设计中需要向AT91RM9200提供稳定的数字3.3V电源和数字1.8V电源,需要向时钟模块提供数字3.3V电源,需要向DDS提供3.3V数字电源和3.3V模拟电源。系统电源输入为5V,设计采用Linear公司的单片双通道电源模块LTM4622将输入的5V转为3.3V和1.8V输出,为系统提供数字3.3V电源和数字1.8V电源,选用LDO电源芯片TPS74401将5V转为3.3V,为DDS芯片提供低噪声的模拟3.3V电源,有助于实现较高的DDS输出性能。同时在芯片的每一个电源管脚放置1颗0.1uF的电容进行去耦。

3 软件设计

软件设计主要是通过对ARM芯片AT91RM9200进行编程,按照一定的算法和协议,将频率控制字以一定的时序发送到DDS芯片JS9854。因此软件设计的重点是频率控制字的计算与频率控制字的传输。

3.1 频率控制字的计算

输出频率由频率控制字(FTW)决定,存在如下公式:

FTW=(Fout×2N)/Fc

其中FTW为频率控制字,Fout为输出频率,Fc为系统时钟,N为相位累加器的分辨率(此例中为48位),频率的单位是Hz。

本设计中,Fc的值为40MHz,N的值为48,Fout取值分别为10MHz±2.2KHz和10MHz±2.8KHz,因此计算出4个FTW的值如下:

FTW1=(9.9972MHz×248)/40MHz=70349040929294.25408

FTW2=(9.9978MHz×248)/40MHz=70353263053944.91392

FTW3=(10.0022MHz×248)/40MHz=70384225301383.08608

FTW4=(10.0028MHz×248)/40MHz=70388447426033.74592

在不影响精度的情况下,对结果取整,再将这个数以二进制的数值表示,就可以得出最终的48位频率控制字。

3.2 频率控制字的传输

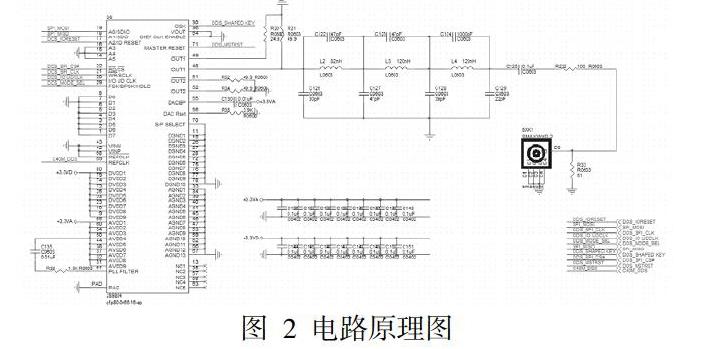

频率控制字通过SPI以串行的方式实现传输,SPI接口时序如下图3所示。

配置频率控制字是一共要在片选和时钟上升沿下传输7个字节的数据,第一个字节8个bit确定频率控制字的寄存器地址,第二个字节传输频率控制字的[48:41]位,第三个字节传输频率控制字的[40:33]位,以此类推,第七个字节传输频率控制字的[7:0]位,然后将片选拉高,完成48位频率控制字的传输。

4 输出结果

本设计中DDS输出信号频率为10MHz±2.2KHz和10MHz±2.8KHz,信号功率约为-20dBm,如下图4所示。

5 结束语

本文设计的中频模拟电路产生的信号精度高、稳定性好。此外,该系统还具有电路简单、搭建方便、可靠性高的特点。DDS芯片在低、中频波段范围内,都能产生质量非常高的输出信号,只要改变频率控制字就可以方便的改变输出信号的频率。

参考文献:

[1] 费元春、苏广川、米红等.宽带雷达信号产生技术[M].国防工业出版社,2002.

[2] 席安安、張春容. DDS在复杂信号产生中的应用研究[J].火控雷达技术,2005,1: 17-19.

[3] 张涛,陈亮.现代DDS的研究进展与概述[ J].电子科技,2008(3):73-77.