基于辐射环境集成电路的二维纠错码设计*

齐艺轲, 李少甫,2, 施宇根

(1.西南科技大学 信息工程学院,四川 绵阳 621010;2.中国空气动力研究与发展中心 气动噪声控制重点实验室,四川 绵阳 621900)

0 引 言

现如今传感器已经成为了电子系统中不可或缺的组件之一,并且广泛地应用于军事、医疗、航空航天、地质勘探等各个领域,辐射环境会对传感器中集成电路造成巨大的影响。随着集成电路工艺向纳米(nm)级、高密度、高性能低成本的发展,其工作频率高、电压低等特性使其更易受到辐射环境的影响从而产生软错误,并在实际系统中可能会导致信息丢失、系统故障或失控等现象。如今,软错误不仅会导致SBUs(single bit upsets),并且由集成电路工艺的发展和其对辐射环境的敏感性更易导致MBUs(multiple bit upsets)的发生,而由辐射剂量、粒子射入角度等因素的影响,翻转位数可能会更多。因存储器占据了集成电路系统级芯片60 %以上的芯片面积,并且系统中绝大部分的失效是由存储器引起的[1],所以,对集成电路中存储器进行加固以保证集成电路在辐射环境中的正常工作具有现实意义和重要的研究价值。

集成电路中常见的加固技术一般分为电路级、器件级、版图级、系统级加固技术。因系统级加固技术在较高的层面上分析,不会改变原有工艺,带来实际硬件开销和成本较低,所以成为了集成电路抗辐射加固研究中的热点。

传统系统级加固技术通常采用汉明码及其扩展码。汉明码[2]为单纠错双检错码(SEC-DED),不能纠正MBUs,而在信道编码中常用的RS(reed-solomon),Turbo,LDPC(low-density-parity-check-code)等纠错码虽然有优异的纠错性能,但此类码字编译码较为复杂,会给相应的编译码电路带来更多的面积、功耗、时延等。

以矩阵码为代表的二维纠错码[3,4]在纠错能力和编译码复杂度上有较好的平衡,适合于对集成电路存储器进行抗辐射加固。此类纠错码一般将码字信息位排列成矩阵形式,通过水平、竖直或斜向分别添加校验位进行构建。矩阵码[3]水平方向通过汉明码、竖直方向通过奇偶校验的方式得到校验位,能100 %纠正两位错误;文献[5]提出的方法通过水平、竖直、斜向奇偶校验的方式得到校验位,能100%纠正三位错误。但以上方法具体编译码电路功耗较高,而且纠错位数有限均较难满足于MBUs位数更多的情形。

针对以上问题,设计了一种新型二维纠错码及其相应的编译码电路,在功耗、时延较低的基础上拥有较强的纠错性能,适用于对辐射环境下传感器集成电路进行抗辐射加固。

1 编译码总体设计

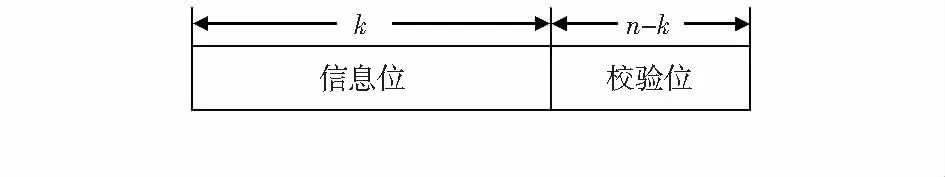

一个典型的纠错码码字结构如图1所示,其中,k为信息位,n-k为校验位,码长为n。

图1 纠错码码字结构

在集成电路抗辐射加固中运用纠错码对存储器进行加固时,需要相应的编译码电路对错误进行纠正。通过将信息位k输入至相应的编码电路产生校验位完成编码步骤,通过将存储器中的码字n输出至相应的译码电路完成译码步骤从而得到信息位k。

1.1 编码原理与电路设计

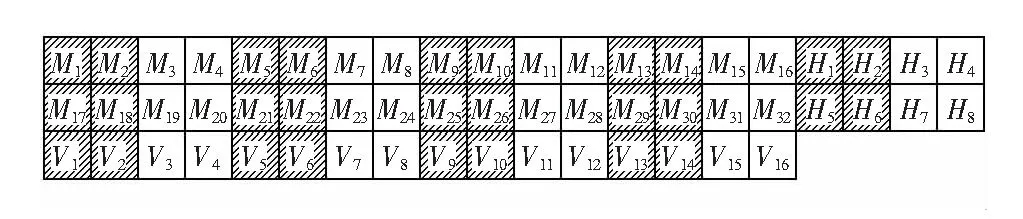

新型二维纠错码在逻辑上将一维信息序列排列成二维矩阵形式。基于逻辑可以避免存储器物理结构的改变,具体编码方式为将信息位k排列成矩阵A(k/2,2),然后将每行通过信息长度d分割成若干块(注:k/2能被d整除),水平方向校验位通过间隔d位信息长度进行异或相加,分块的优势在于能拓展水平方向校验位的纠错检测范围,而竖直方向校验位通过竖直方向信息位直接异或相加得到。以k=32,d=2为例,编码结构如图2所示。

图2 k=32新型二维纠错码

水平方向校验位为

(1)

竖直方向校验位为

V1=M1⨁M17,V2=M2⨁M18,…,

V15=M15⨁M31,V16=M16⨁M32

(2)

编码操作通过上述步骤完成,因此,编码电路只由异或逻辑构成,编码电路如图3(a)所示。

1.2 译码原理与电路设计

码字在存储器中存储时,由于辐射影响会出现错误,为获得正确码字还需进行译码操作。首先,由存储器输出的信息位M′,重复编码步骤得到H′与V′。其次,由编码所得校验位H,V与H′,V′得出水平校正子ΔH与伴随式S,具体由以下公式得出:

ΔH1H2=H1H2⨁H′1H′2,ΔH3H4=H3H4⨁H′3H′4,

ΔH5H6=H5H6⨁H′5H′6,ΔH7H8=H7H8⨁H′7H′8

(3)

S1=V1⨁V′1,S2=V2⨁V′2,…,

(4)

由水平校正子ΔH与伴随式S可以判定读出的信息位是否出错,分为以下三种情况:当水平校正子ΔH与伴随式S都为零时,表示接收到正确信息位;当水平校正子ΔH与伴随式S只有一个为零时表示

校验位出错,仍然接收到正确信息位;当水平校正子ΔH与伴随式S都不为零时,表示信息位出错,通过式(5)得出正确信息位:

Mcorrect=M′⨁S

(5)

译码操作通过上述步骤完成,译码电路设计(局部)如图3(b)所示。

图3 编码电路与译码电路设计

1.3 错误图样分析与改进设计

新型二维纠错码在发生四位、五位错误时有如图4所示的特殊图样不能纠正,运用信息位与校验位交错排列的方法可以防止此类错误图样的发生,从而提高纠错能力,具体排列方式如图5所示。

图4 四、五位特殊错误图样不能纠正情形

图5 信息位与校验位交错排列示意

首先,将码字第一行的信息位存入16个存储单元;然后将第一行水平校验位、竖直校验位、第二行水平校验位依次存入24个存储单元;最后再将码字第二行的信息位存入16个存储单元。运用上述信息位与校验位交错排列的方法既可以提高纠错能力,又可以在纠错范围内纠正信息位与校验位同时出错的图样,而对于只有校验位出错的图样,运用在纠错码中常用的检错电路[6]既可以降低电路功耗又可以纠正只有校验位出错的图样。这种交错排列方法只是基于逻辑选择性的排列数据,不会改变存储器的物理结构,容易实现。

2 实验结果与性能分析

2.1 纠错能力分析

运用故障注入的方法,在MATLAB仿真平台对新型二维纠错码进行纠错能力分析,并使用大量数据(106)以保证样本的完整性。以信息位为32位为例,将所设计的二维纠错码与汉明码、矩阵码的纠错能力进行对比,如图6(a)所示。

由图6(a)可以看出,所设计的二维纠错码不仅能纠正一位错误与两位错误,而且较于汉明码与矩阵码,最多能100 %纠正五位错误,有更强的纠错能力,适用于MBUs多位错误发生的情形。

2.2 功能验证

将设计的新型二维纠错码运用Verilog硬件描述语言进行编译,并在ISE 14.7仿真平台进行功能验证。如图6(b)所示,D1~D32为原始信息位,假设信息位第6到10位发生错误从而得到M1~M32,经译码电路后输出的信息位为C1~C32。可以看出,经过译码电路后原始的信息位与输出信息位相同,从而验证了新型二维纠错码的可行性。

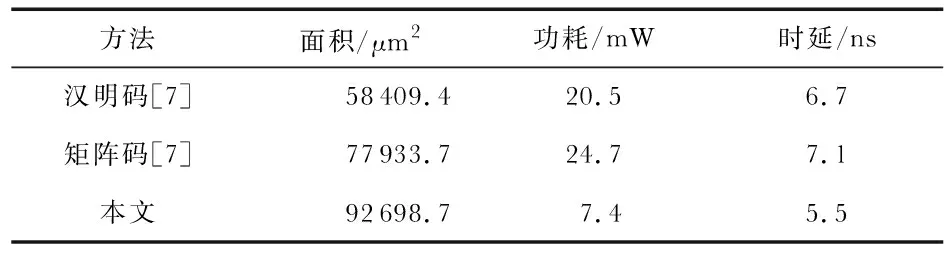

2.3 面积、功耗、时延等参数分析

运用Design Compiler工具在180 nm工艺对所设计的编译码电路进行综合,从而得到面积、功耗、时延等参数。

表1 面积、功耗、时延对比(k=32)

由表1可以看出:设计的新型二维纠错码电路面积、功耗、时延分别是汉明码的159 %,36 %,82 %,分别是矩阵码的119 %,30 %,77 %。这是因为所设计的二维纠错码在译码电路中运用与门来增加纠错检测范围,所以,布线较多因而电路面积较大,编译码原理简单并且使用门级电路因而功耗、时延较小。这表明:设计的二维纠错码编译码电路相比于汉明码与矩阵码在面积增加不大的基础上拥有较低的功耗与时延。

码率也是考量纠错码性能的重要指标之一,码率信息位/(信息位校验位)。如表2所示,汉明码的码率明显高于矩阵码与设计的二维纠错码,但与同类型二维码相比,所设计的二维纠错码码率高于矩阵码。

表2 码率对比(k=32)

因以上分析都是从单方面评价纠错码性能的优劣,相对具有片面性。文献[3]提出了纠错率每开销(correction coverage per cost,CCC)来评价纠错码的综合性能,但此方法未将码率纳入评价指标,文献[7]引入校验位以获得更全面的评价体系纠错率每开销=纠错率/开销,其中,开销定义为开销=面积×功耗×时延×校验位,其所需数据可以由图6(a)与表1、表2得到。图6(c)为CCC对比,由该图可知,当发生SBUs时,汉明码为对集成电路存储器加固最好的方法,但当发生MBUs时,设计的二维纠错码CCC要高于汉明码与矩阵码,为存储器抗辐射加固更好的方法。

3 结 论

根据实验结果与性能分析表明,设计的二维纠错码性能较好,并且功耗、时延较低符合传感器对功耗的敏感性,适用于对辐射环境下传感器集成电路进行抗辐射加固。