基于硅工艺的毫米波功率放大器中的堆叠型设计

那炘

摘 要:为了提高基于硅工艺功率放大器电路中场效应管的电压处理能力,越来越流行的方法是使用共享相同漏极电流的多个器件的串联连接。该方式使得高频率的功率放大器能够实现瓦特级输出功率,且具有良好的效率,线性度和扩展带宽。它还被证明可以在高达90GHz的毫米波频率和带宽高达50GHz的宽带放大器中有效工作。本文回顾了堆叠MOS场效应管设计的进展和挑战。重点突出阐述了晶体管在与上层晶体管堆叠时,如何进一步保证晶体管层间电流和电压的正确对准的相关问题。

关键词:CMOS功率放大器;高效率;毫米波

第一章 引言

雖然摩尔定律的进步提供了大量具有高微波增益的低成本MOSFET,但是缩放晶体管的电压处理能力还不适合功率放大器。大多数功率放大器都必须采用高压摆幅,以避免在场效应管(Field Effect Transistor,FET)漏极处使用非常小的负载电阻,同时对50欧姆输出进行大规模阻抗转换,这些输出往往是有损耗的并且带宽受限。从Shifrin,Sowlati,Ezzedine 和其他人的开创性工作开始,许多研究成果中已经确定,增加片上电压摆幅的有用策略是将器件串联组合,各个管子的电压相位相加以产生相对高的输出电压。本文回顾了使用数字CMOS集成堆叠结构实现微波和毫米波频率功率放大器的最新结果,并强调了在这一方面继续进行工作的挑战。

第二章 堆叠型功率放大器设计

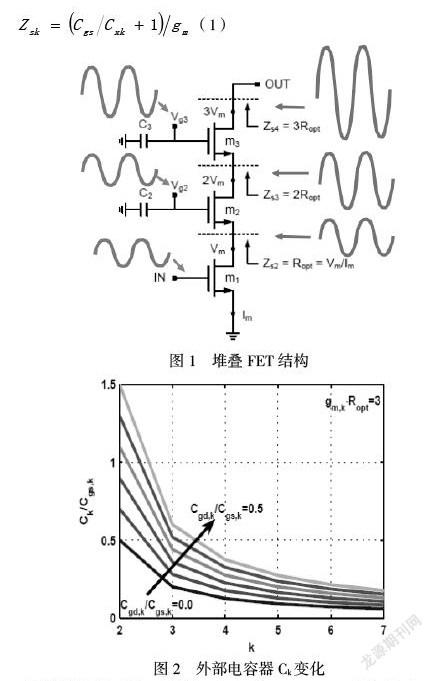

堆叠功率组合方法在图1示出。在大多数例子中,总漏极电压摆动在堆叠中的晶体管之间被均等地划分。由于漏极电流近似恒定,所以呈现给不同漏极的阻抗Zsk必须随着堆叠上升而增加。通过选择附着在上层晶体管的栅极上的适当的电容Cx,可以方便地设置这些阻抗。如果忽略Cdg,可以表示为:

对于级联连接,当Cx非常大时,导致Zsk = 1 / gm。相比之下,Cxk具有特定值,其导致适当增加的Zsk(尽管它从原则上可能作为共栅器件的情况下降低了顶级器件的增益)。因此,顶部器件的栅极经历显著的电压摆动,这是必要的,以避免在堆叠的上层处的漏极和栅极之间的击穿。式(1)指导了堆叠结构的直观设计,虽然它可以在许多III-V族器件中相对精确地应用,但在传统的硅基MOSFET中,必须对其进行校正以解决Cdg的显着影响。图2显示了Cx不可忽略时,Cdg / Cgs的计算值,这是对于Ropt = 3 / gm的特殊情况。利用这一效果是典型的设计方案。式(1)还有其他注意事项,这使得设计更复杂。阻抗关系假定晶体管作为压控电流源,在其有源区中工作;当器件两端的漏极电压崩溃时(当功率放大器接近饱和时),应用不同的考虑因素。此外,存在显著的电容,这些电容有助于在漏极处看到阻抗。加载中间节点的电容包括漏极,浮动源和互连的基板的寄生电容,以及上晶体管的固有栅极电容(由Cx修改确定)和晶体管的Cds值。为了减小寄生电容,以及避免体效应跨导退化,许多堆叠CMOS FET努力采用了绝缘体上硅工艺,特别是高电阻率硅或蓝宝石衬底。

第三章 毫米波设计

在高频时,忽略寄生电容会产生不可接受的增益降低。为了调出浮动源节点处的电容,已经采用了各种策略:a)并联电感到地:b)FET之间的串联电感:c)添加外部电容CD。在由Ezzeddine引入的最后一种技术中,如果实际上电压按照良好建立的比例随着堆栈上升而缩放,那么在电压偏移期间由Cdsx注入节点的电荷可以准确地抵消从电压偏移中移除的电荷。该节点以其宽带方式从其寄生电容接地。通常需要准确的电容知识以避免引入不稳定性。在许多毫米波设计中,并联电感器或传输线已用于中间节点匹配。一个典型的例子是采用45nm SOI CMOS工艺的3层放大器,其工作频率为90 GHz,增益为12 dB,饱和输出功率为17 dBm,PAE为14%,。

实际上,在毫米波状态下,根据简单的理论,没有观察到输出功率精确地缩放,因为沿着叠层的电压并不总是相加。如果在阶段k存在向上移动堆叠的相位角θk的变化,则功率降低并且效率受到不同阶段的cos2θk的乘积的影响。一种工作在45 GHz的堆叠FET放大器的就采用不同级数构建了一个新型结构。对于每个晶体管场景的恒定电流以及恒定RL情况,表示出了功率随晶体管数量的理论变化,其输出功率高达140mW。

各种机制都可能导致堆叠FET放大器的振荡行为。共栅极或共源共栅放大器众所周知的机制之一与堆叠晶体管源的电容性负载有关。从栅极看到的阻抗可能具有负实部,如果存在与外部栅极电容器串联的寄生电感Lx,则振荡可以在由Lx和总电容的谐振给定的频率下发生。相关的观察结果是,看到顶部晶体管的源极的阻抗仅对于栅极端子处的设计电容Cxk具有适当的设计值Ropt;如果存在接地寄生电感,则在足够高的频率下,栅极与地之间的阻抗将具有正电抗,负载阻抗Zsk将具有负实部。

第四章 总结

到目前为止讨论的堆叠FET结构使用连接到堆栈底部的单个输入驱动器,以及连接到上部晶体管的栅极的无源元件。一个有吸引力的想法是通过使用单独的驱动器或一堆变压器或耦合线来使用堆叠中更高的晶体管的有源驱动。堆叠结构的分析主要集中在A类或AB类放大器上。堆叠结构也已用于开关模式操作,用于在高达45GHz的频率下实现E类放大器。另一个主题是使用堆栈内的各种晶体管来执行附加功能,例如调制。得到的结构具有混频器/调制器以及功率放大的功能。这种电路可以比单独的调制器具有更高的效率,因为所需的电压开销是整个电源电压的一小部分,并且实现了非常高的频率操作。