一种雷达回波采集及显示方案设计

倪文飞,夏 丹,鲁长来,毛 飞

(安徽四创电子股份有限公司 安徽 合肥 230000)

0 引言

雷达IQ数据最后以A显模式展示于计算机界面[1-2],处理流程包括信号采集及数据发送、数据接收及显示,用户可直接观测A显波形判断处理是否正确。文献[3]阐述了一种S波段信道化数字接收机,文献[4]论述了一种光纤数据采集的系统设计方法,文献[5]通过C++实现雷达显示设计。雷达回波采集及显示设备存在的主要问题是计算机无法处理标准协议光纤数据,需通过昂贵的光纤采集设备对数据进行处理以便识别数据,提高了设备成本,同时,显示处理一般通过C++及开发库设计软件实现,软件语法繁琐,开发周期较长。针对以上问题,首先方案通过光吉比特以太网[6]实现IQ数据传输,可减少设备量,其次LabVIEW作为一种高效开发软件,已应用于众多开发场景,其图形操作模式减少了方案数据接收及显示软件设计开销。

1 信号采集及数据发送

1.1 信号采集

雷达时序周期为2 KHz,回波信号为中心频率30 MHz、带宽2 MHz的脉冲信号,信号采集的功能是对回波信号进行采样并将其转变为数字IQ信号。数字接收机[7]通过ADC芯片以200 MSPS采样率将模拟回波信号转换为16位数字信号,以QDR[8]模式将数据传输至FPGA芯片,FPGA芯片对所接收到的信号进行数字下变频处理,最终输出采样率4 MSPS的基带信号。通过数字下变频[9-11]可有效缩减输出数据率,节约传输带宽。

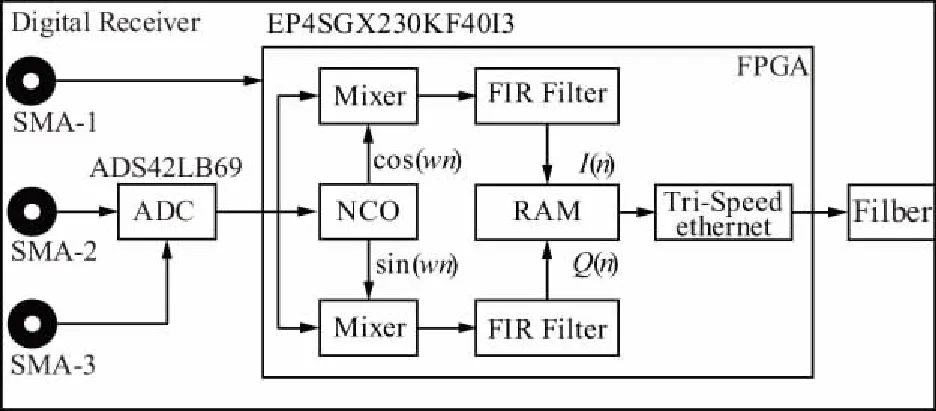

图1中,NCO产生两路正交的数字混频信号,ADC输出数据经过数字混频转变为采样率200 MSPS的零中频信号,通过FIR抽取滤波器[12]将高频分量滤除并将采样率抽成4 MSPS。输出的IQ信号传输至RAM进行数据存储及读写。

图1 数字接收机原理框图

1.2 数据发送

发送数据为数字下变频输出的IQ信号[13],二者均为16位数字信号,IQ信号原始数据率为128 Mbps。进行数据发送时,将I信号与Q信号拼接为32位IQ数据,因此每个周期具有2 000个32位IQ数据,IQ数据通过光纤传输,传输协议为千兆以太网。千兆以太网采样率为125 MSPS,IQ数据采样率为4 MSPS,异步读写先将数据存储,然后进行数据读取,因此异步读写可实现低采样率数据以高采样率传输,FPGA通过双口RAM实现[14]IQ数据异步读写。将每组RAM存储深度设为2 048×32 bit以保证数据存储而不溢出。首先在第一个重复周期,即0~500 μs区间,A口RAM以4MSPS采样率对IQ数据进行实时写操作,数据依次存储于A口RAM地址0~1999存储寄存器中,同时在480~500 μs区间,B口RAM以125 MSPS采样率依次读取B口RAM地址0~1999存储寄存器数据。在下一个500 μs时间内,B口RAM以4 MSPS采样率对IQ数据进行实时写操作,在480~500 μs时间内,A口RAM以125 MSPS采样率进行数据读操作。因此,通过乒乓读写便可实现IQ数据的有效传输,图2为双口RAM的操作流程图。

1.3 三速以太网IP核设计

双口RAM输出的IQ数据需封装以太网帧头才能以标准以太网协议传输,帧头包括目的MAC地址、源MAC地址、IPV4版本协议、源IP地址、目的IP地址及UDP端口号。首先将目的地址设为组播地址230.0.17.1,并将UDP[15]目的端口号设为5 060,封装后的数据帧包含42 Byte以太网帧头、2 Byte帧编号值及8 000 ByteIQ数据,数据总长度为8 044。数据帧通过三速以太网[16]内核输出并经光纤传输至网络交换机,由于数据帧经光纤传输,需将以太网内核工作模式设置为1000BASE-X/SGMII-PCS,缓存深度设为2 048×32 bit。将数据输入三速以太网内核时,在输入第一个32位数据时,需将以太网内核起始使能信号设置为高,当输入最后一个32位数据时,需将以太网内核结束使能信号设置为低电平,当检测到起始使能信号时,开始将数据通过光纤接口发送至网络交换机,当检测到结束使能信号时,结束数据发送。双口RAM操作流程如图2所示。

图2 双口RAM操作流程

2 数据接收及显示

以太网数据帧通过光纤传输至网络交换机,然后被转发至计算机,计算机需要解析出以太网数据帧包含的IQ数据,数据接收及解析通过LabVIEW软件实现。

2.1 数据接收

数据帧封装协议为UDP,因此需调用UDP多点传送控件、UDP数据读取控件及UDP关闭控件,如图3所示。UDP多点传送控件的作用是侦听并接收与所设封装信息一致的数据帧,因此将侦听地址设置为230.0.17.1,侦听端口号设为5 060,与数据帧封装信息保持一致。当接收到数据帧时,控件将其传送至UDP数据读取控件。由于数据帧字节长度为8 044,为防止数据溢出,将数据读取控件缓存深度设为9 000,使缓存深度大于数据帧长度,否则控件将输出错误指示。其次将超时毫秒设为-1,即在空闲时间,UDP数据读取控件处于无限等待状态,否则控件等待超时,将返回错误指示而中断操作。在进行数据包侦听解析时,可能出现错误指示,此时需要调用UDP关闭控件,在产生错误指示时,软件将会执行关闭操作,操作处理流程如图4所示。

图3 数据接收及显示软件框图

图4 数据接收处理

2.2 数据显示

设计通过计算机界面显示数据,UDP控件接收到数据后,将42 Byte以太网帧头去除,只输出2 Byte帧计数值及8 000 ByteIQ数据。UDP解析控件按每8位输出数据,原始IQ数据为32位,即I信号与Q信号分别为16位,所以需将输出数据按每16位拼接以还原I、Q信号。LabVIEW提供出色的脚本编辑功能,通过调用Matlab脚本控件可实现高效科学运算[17]。去除2 Byte帧计数值,每4 Byte长度数据组成一组IQ数据,排列顺序依次为I信号高8位数据、I信号低8位数据、Q信号高8位数据及Q信号低8位数据。I信号计算如式(1)所示:

I_data=I_l+I_h×28。

(1)

同理,Q信号的计算为:

Q_data=Q_l+Q_h×28。

(2)

式(1)和式(2)计算所得为补码,需要将其转换为原码。以I_data为例,当I_data最高位为1时,即大于32 767时,表示该值为负数,则I_data原码计算如式(3)所示:

I_data=I_data-216。

(3)

当I_data最高位为0时,表示该值为正数,则原码为其本身。Q_data原码计算过程与I_data类似。图形界面显示的为IQ数据幅值,幅值X计算如式(4)所示:

X=10lg(I_data2+Q_data2)。

(4)

幅值显示通过调用波形显示控件实现,由于幅值显示是实时的,需调用While循环结构以保证进程一直执行,对循环结构而言,在无中断条件产生时,程序一直执行,当执行停止中断时,程序将停止。

3 光纤通信硬件设计

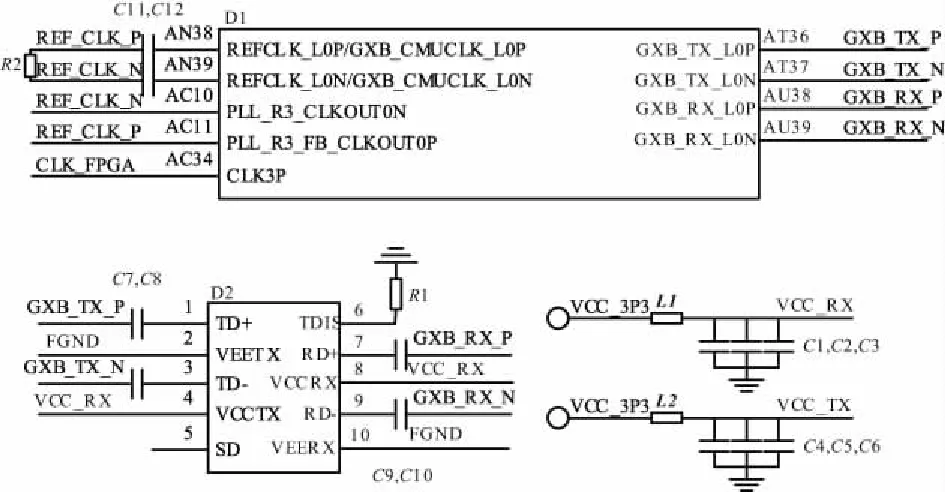

数据帧通过FPGA芯片EP4SGX230KF40I3产生,数据传输通过光纤模块USOT12F21I实现,该光模块最大通信速率为2.5 Gbps,满足光吉比特以太网通信速率需求。图5为光纤通信原理图,D1为FPGA,AC34为FPGA系统时钟管脚,该管脚为FPGA提供系统驱动时钟,D1通过时钟管脚AC11及AC10输出差分时钟REF_CLK至光纤时钟输入管脚AN38及AN39,该时钟为FPGA光纤接口提供工作时钟,由于是差分时钟,因此需在时钟接收处端接100 Ω电阻。D2为光纤模块,1脚及3脚为光纤数据发送管脚,7脚及9脚为光纤数据接收引脚,1、3脚与D1的AT36、AT37对接,7、9脚与D1的AT38、AT39对接,D2采用3.3 V电压驱动,VCC_RX为D2接收驱动提供供电,VCC_RX为D2发送驱动提供供电,均通过磁珠与电源VCC_3P3连接。为使数据传输具有良好耦合特性,须在数据串接100 nF电容,如C7,C8,C9,C10,C11,C12。C1,C2,C3为滤波电容,容值分别为47,10,0.1 μF。

图5 光纤通信原理

4 实验验证

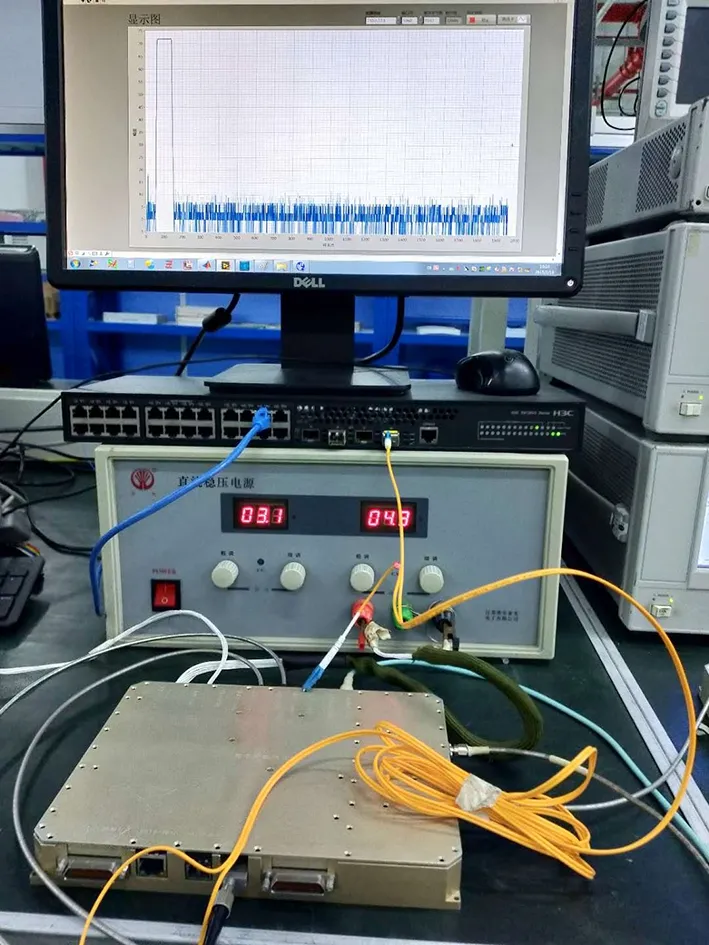

图6中,通过信号源输出模拟回波信号至数字接收机信号输入口,数字接收机通过光纤将数据传输至计算机显示,设计通过稳压电源供电。计算机界面显示的为最终通过LabVIEW显示输出的信号时域图,可知设计准确显示了脉冲回波信号。

图6 现场测试图

5 结束语

本设计方案的实现方式灵活高效,显示开发设计可进一步扩展对信号进行频域分析,设计方法简单明了。由于采用国际标准的光吉比特以太网作为数据传输协议,因此该设计方案也可以运用到其他数据传输系统中,在硬件设备量及软件设计方法上均有优势。但是,随着相控阵体制雷达的深入应用及多脉冲信号处理技术的产生,光以太网技术需要面对数据传输率上升的问题,需要后续做更深入的思考和研究。