基于Verilog的VGA显示控制电路设计

王涌 肖顺文 罗春梅

摘要:采用自上而下的设计方法实现了一个分辨率较高、显示迅速且协议简单的VGA显示控制电路。在QUARTUS II 13.1软件开发平台上使用Verilog HDL语言来完成时序模块和彩条像素模块的描述、编译,最后在第三方仿真工具Modelsim-Altera中对其进行模拟仿真,结果显示,该设计满足系统要求,能够成功的通过VGA接口在显示器上显示图案。

关键词:Verilog HDL语言;VGA技术;QUARTUS II 13.1;Modelsim-Altera

中图分类号:TN92 文献标识码:A 文章编号:1007-9416(2019)04-0150-02

0 引言

近年来,随着数字电路设计技术的逐步发展,集成电路的发展越来越趋近于超大规模、更低功耗及超高速[1]。Verilog HDL就是在迫切需要设计者使用EDA工具完成大规模集成电路设计发展要求的情况下应运而生的,它使用编写代码的方法来完成数字电路的设计,不管是底层的门级电路,还是高层的行为描述,都可以通过代码实现,这种方式大大的提高了数字电路的设计效率[2]。本文就是采用Verilog_HDL语言来实现一个VGA显示控制电路。VGA接口由于具有传输速率高,协议简单,成本低等特点,因此被广泛使用。

1 设计原理

1.1 VGA时序分析

VGA主要用于计算机显卡传输图像到显示器的桥梁,将显卡处理的视频图像数据实时传输到显示器上进行显示。广义的VGA为VGA显示器,狭义的VGA为VGA分辨率的时序。由IBM公司推出的采用RGB模拟信号的VGA视频传输标准,定义了具有60Hz刷新频率、可产生1677万种色彩的640×480像素格式。

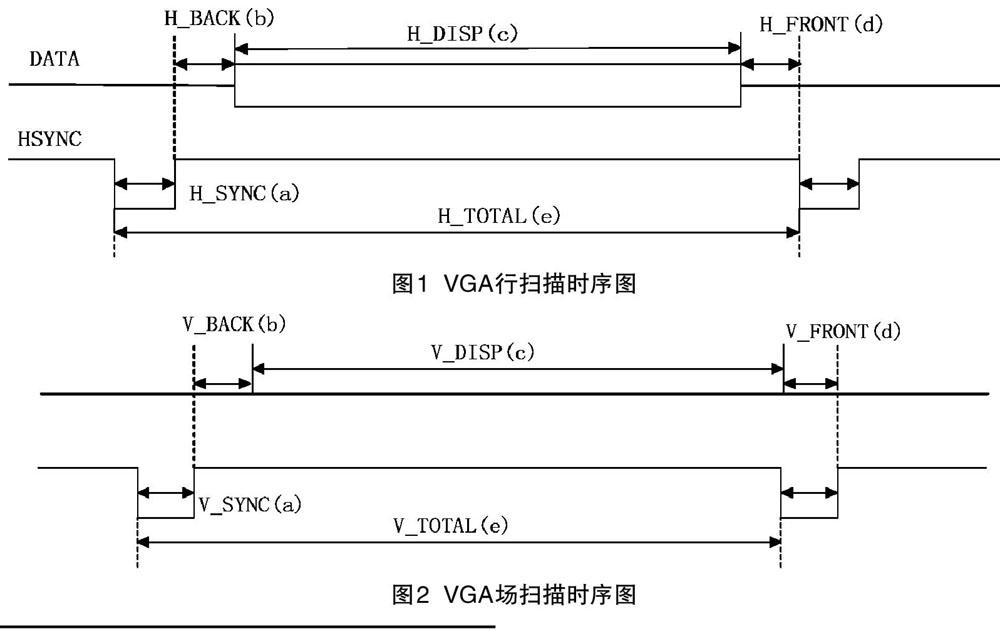

VGA的行扫描时序情况,如图1所示。

行同步时期a、行消隐后肩b、行显示时期c、行消隐前肩d四部分组成一个完整的扫描周期。开始扫描,首先进行行同步操作,同步完成后才开始数据的扫描。

同样,场扫描时序图和行扫描时序图类似,如图2所示。

一个场扫描周期由n个行扫描周期所组成。并且一次场扫描时序由完整的场消隐前肩、场同步时期、场消隐后肩、场显示时期组成,且自成体系。

1.2 VGA分辨率

分辨率就是一个用来表示物体精确度的参数,若显示器的分辨率参数越大,则其显示的图像越清晰,包含的信息量越大,画质中的细节越多,图像的保真性越高。

由于人的视觉暂留,想要实现CRT显示器画面不闪烁,至少需要实现每秒25帧画面的更新速度。而显示器为了保证图像流畅,视觉效果最佳,通常扫描帧都在每秒60帧及以上。IBM公司最先推出VGA视频标准,定义的VGA格式为具有60Hz刷新频率,图像分辨率为640×480。由于制造技术的快速发展,分辨率标准越来越高。本设计中的分辨率设为800×600,刷新频率设为60HZ。针对不同的分辨率,通常可以用两种方法来表示时序参数:像素表示法和时间表示法。FPGA擅长计数电路,因此采用像素表示法[3]。

2 设计实现过程

本文采用“自上而下”的方式,在ALTERA公司的QUARTUS II 13.1软件开发平台上使用Verilog HDL语言对PLL_40M时钟模块和VGA_module时序与彩色线条显示模块进行描述,在顶层模块中使用例化语句对两个模块进行调用,程序设计完成后,对所设计的VGA显示控制电路进行编译,编译无误后,通过编写Testbench仿真测试文件,在第三方仿真工具Modelsim-Altera中进行模拟仿真。

2.1 PLL_40M时钟模块

时钟模块提供电路所需的40MHz的时钟。Intel提供了用于实现PLL(锁相环)功能的IP核ALTPLL,在本设计中调用、配置该IP核可实现设计所需要的40MHz的时钟。

2.2 VGA_module模块

VGA_module模块用于生成设计所需的VGA时序驱动和提供VGA 显示的图像数据。VGA的时序驱动部分是相当固定的,本模块主要的设计方法是用了两个寄存器来分别对行扫描和列扫描进行管理。当行扫描计数器扫描完行同步脉冲后至高HSYNC;同理,当列扫描计数器扫描完列同步脉冲后至高VSYNC信号。

3 设计结果

在QUARTUS II 13.1软件开发平台上打开HDL的RTL级图形观察器,就可以得到VGA显示控制电路的模块图如图3所示。

在第三方仿真工具Modelsim-Altera中进行模拟仿真。本设计的要求是通过VGA接口,在显示器上四个区域依次显示红色(11100000)、黄色(11111100)、蓝色(00000011)、绿色(00011100),根據如图4总体设计仿真波形依次显示为11100000、11111100、00000011、00011100,得出该设计结果符合设计的要求。

4 结语

利用Verilog HDL设计VGA显示控制电路,采用“自顶向下”的方法,在QUARTUS II 13.1软件开发平台上,将各个独立但又相互联系的模块利用顶层文件调用实现复杂的数字电路,实现了以软件方式设计硬件的目的。本设计只实现了VGA基本的彩条信号显示,在此基础上还可以做很多的扩展,将其设计成动态图片的显示,可塑性很强。在第三方仿真软件Modelsim-Altera中验证VGA彩色信号显示控制电路的功能,操作简单易上手,不需要实际操作焊接、调试电路来验证设计功能,有效减少了设计所需的时间。

参考文献

[1] 潘松,黄继业,陈龙.EDA技术与Verilog HDL.北京:清华大学出版社,2010.4.

[2] 夏宇闻.Verilog基本知识(上)[J].电子产品世界,2002(19):70-72.

[3] 韩彬,于潇宇,张雷鸣,宋恒,林海全.FPGA设计技巧与案例开发详解[M].电子工业出版社.2016.1.

[4] 韩磊.基于FPGA的VGA信号发生器设计[J].产业与科技论坛,2018,17(20):54-55.

[5] 蒋艳红.基于FPGA的VGA图象信号发生器设计[J].电子测量技术,2008(03):78-81.

[6] 马智强.PXI总线VGA图像信号发生器硬件模块设计[D].电子科技大学,2015.