某机载电子控制器余度控制技术研究

王晓勇,李兴智

(中国航空工业集团公司西安航空计算技术研究所,西安 710065)

随着多电飞机的发展,机载机电系统进一步综合化,综合化的系统架构对电子设备的任务可靠性要求更高。在电子设备的设计过程中相应的出现了主备控制、双余度控制和多余度控制的产品架构;根据模块功能的区别,形成了同构型设计、非相似余度设计等产品配置;供电模块也相应的分为分布式、综合式供电等供电模式;各种架构设计均是为了通过硬件设计减少产品的共模故障,提高了任务执行的可靠性。

本文以某机载机电子系统控制器为对象,进行了余度控制相关技术的研究分析。

1 产品架构设计

产品采用同构型主备控制架构设计,简化设计工作,提升产品的三化水平,总体架构如图1所示。

图1 产品架构图

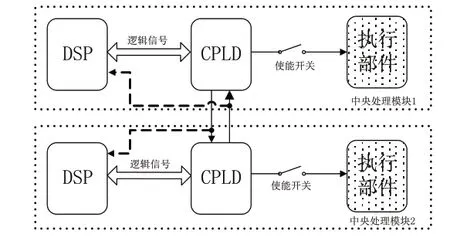

2块中央处理模块为同构型设计,默认中央处理模块1为主控状态,中央处理模块2为热备份状态,产品正常上电后,主备处理器模块通过硬线连接进行同步,同步完成后,主处理器模块故障时,主处理器模块上的通道故障逻辑电路终止其对接口模块的控制,备处理器模块检测到主模块故障后,接管输出控制任务。2块电源模块为同构型设计,一块给中央处理器模块1和接口模块1提供二次电源,另一块给中央处理器模块2和接口模块2供电,双供电电路无交汇点。

2 主备同步设计

同步功能实现主备处理器模块任务运行的实时匹配,通过硬线连接设计主备同步电路,在软件中设计上电同步和周期同步,上电同步在模块BIT 运行之后执行,同步等待时间指标较长,保证主备处理器模块接收的接口状态和下发指令一致;周期同步每个任务周期执行一次,同步等待时间指标较短,保证主备通道切换后,输出控制任务的无缝接管。

同步过程采用硬线握手算法实现,具体如下:

(1)控制本通道同步信号输出“1”,并等待对方通道同步控制信号。

(2)若检测接收到对方通道同步控制信号为“1”,控制本通道同步信号输出“0”并等待对方通道同步控制信号。

(3)若检测接收到对方通道同步控制信号为“0”,则同步完成。

(4)若等待超时,则通道同步失败,记录该故障状态后上报。

3 主备通道切换

主处理器模块故障时,通道切换电路应保证备处理器模块可以及时接管任务,实现和外部系统的通信。通道切换逻辑(CFL)负责采集模块工作状态,并将状态信号发送给CPLD;CPLD 编程实现切换逻辑,并将逻辑输出使能信号下发给输出执行电路。

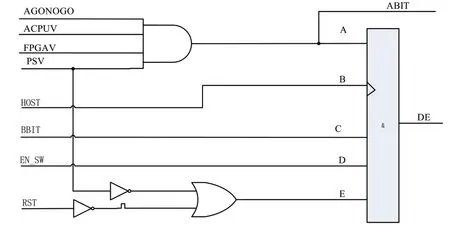

通道故障应具有以下功能:

(1)上电自锁功能:主备通道故障逻辑应保证本模块接口在默认情况下均处于安全状态。

(2)输出控制:主备通道故障逻辑应保证本通道与刹车接口模块和前轮转弯接口模块输出执行电路的关闭或使能。

CFL 硬件设计。通道切换逻辑的主要载体为CPLD 芯片,处理逻辑由CPLD 编程实现,使用VHDL 语言编码。CFL 硬件设计如图2所示。通道故障逻辑设计如图3示。

图2 CFL硬件设计

图3 通道故障逻辑关系

4 交叉链路传输和心跳监控

交叉链路传输(CCDL)和心跳监控都是为了主备处理器之间进行相互工作状态确认及数据备份交换。

交叉链路传输内容包括两部分:一是CPU 工作状态、本CPU 模块的BIT 结果、输出使能状态;二是外部监控总线和指令总线的通信数据。

其中,1项用于状态监控,主备切换;2项用于防止本CPU模块与外部系统交联的总线故障时,依旧可以获取外部系统数据。当交叉链路传输故障时,主备处理器模块的工作状态通过彼此的心跳信号、输出使能信号进行确认,交叉链路传输所传输的数据仅作为备份数据;同时,主备CPU 与外部系统的双余度总线设计失效,降级为单路的总线通信。

心跳监控用于自主获取对方处理器工作状态,定时器中断开启后,软件按照N 个单任务周期的时间周期进行两路心跳字接收检测。当同时收到1或者同时受到0则心跳正常,否则心跳异常。心跳异常时,异常计数加1,心跳异常计数大于X 时报心跳故障。心跳故障时,再检测CCDL 传输的对方工作状态,若CCDL 数据同时故障,则进行自主通道切换。

5 结束语

为了提高机载电子设备综合后的安全性和可靠性,该电子控制器设计为主备处理控制、接口独立的余度架构,本文对其余度管理相关的同步、通道故障切换和交叉链路传输进行了研究,该余度架构技术已经过了多项系统综合试验,可以提高系统的任务可靠性。