动态随机存储器刷新的分析

柴晓东

(黄河科技学院国际学院 河南郑州 450063)

1 DRAM 存储器

DRAM 存储器的存储元是由一个MOS 管和电容器构成。MOS 管作为一个开关使用,通过MOS管对电容器进行充电或放电,利用电容器的电荷存储效应来存储数据。当电容器充电后,电容器上充满电荷时,表示存储数据1;当电容器放电后,电容器上没有电荷时,表示存储了数据0。虽然MOS作为开关使用,其输入阻抗相对较高,可达到1014欧姆,但电容器的自动放电是不可避免的。随着时间和温度的变化,电容器上的电荷会慢慢减少。这种电荷的漏电,会导致电容器上存储的数据丢失,即数据1 的丢失。为了防止出现这种数据丢失的现象,必须定期对DRAM 中存储的数据进行读操作,通过对电容器充电的方法,及时对电容器上的电荷进行补充,使其恢复到放电前的状态,这个过程就称为刷新。

在DRAM 存储器中,读1 的过程也是刷新的过程[1]。当读出1 后,刷新缓冲器会打开,读出的数据1 又会经过刷新缓冲器被送到位线上,通过MOS 管对电容器进行再次充电,从而保证电容器上的电荷得到补充,即对电容再次写1。但是DRAM 的读操作具有随机性,利用读操作进行刷新,不能保证在一定的时间间隔内,将DRAM 内所有的存储元都进行一次刷新。因此,在DRAM 内部有一套独立的刷新方法。

2 刷新方式

刷新方式有两种,一种是分散式刷新,一种是集中式刷新。两种刷新方式中,分散式刷新方式是最常见的。

2.1 分散式刷新

分散式刷新是把DRAM的每一行刷新都均匀的分布到所有行都被刷新一次的刷新时间(刷新周期)内,即在所有行都被刷新一次的时间(刷新周期)内,每隔一段时间,对其中一行进行一次刷新,整个刷新时间结束,DRAM的所有行都被刷新一次。当DRAM不进行刷新时,即可进行相应的读、写操作。例如,某DRAM有1024行,其刷新所有行的时间为16ms,则任意相邻两行的刷新间隔时间应为16ms/1024=15.6μs。在刷新间隔15.6μs内,如果DRAM不进行刷新操作,则可进行读、写操作。

2.2 集中式刷新

集中式刷新是将DRAM的所有行的刷新都集中在一个刷新周期内的一段时间内进行。即整个刷新周期分两个阶段,前一个阶段时间内将DRAM的所有行进行一次刷新,而在后一个阶段时间内则进行相应的读、写操作。例如,某DRAM有1024行,其刷新周期为16ms,每一行的刷新操作时间为130ns,则刷新所有行需要的时间为130ns×1024,约为0.133ms,而可用于读、写操作的时间为16ms-0.133ms=15.867ms。即整个刷新周期分为0.133ms和15.867ms两个阶段。前一阶段时间0.133ms用于刷新1024行,后一阶段时间15.867ms用于进行读、写操作。

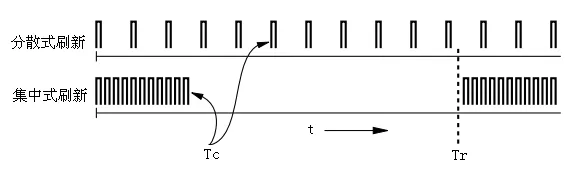

图1所示为分散式刷新和集中式刷新两种刷新方式的时序对比图。其中Tc为刷新一行所用的时间,Tr为规定的将所有行都刷新一次所需要的时间(刷新周期)。

图1 分散式刷新和集中式刷新

3 刷新方法

刷新方法有三种,RAS#-only刷新,CAS#-before-RAS#刷新和隐蔽刷新。

3.1 RAS#-only 刷新

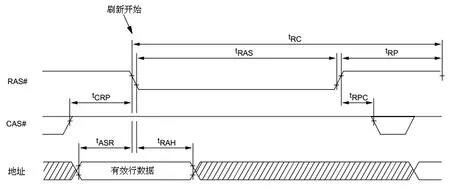

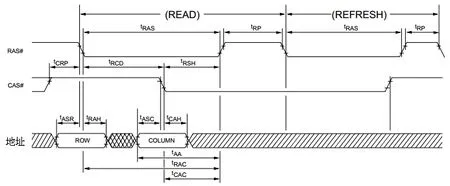

图2 RAS#-only 刷新

RAS#-only 刷新又称为ROR[2]。在执行RAS#-only 刷新时,行地址信号会被送到地址线上。在地址线上出现有效的行地址信号后,行地址信号RAS#开始由高电平向低电平转变。当RAS#信号低电平有效时,该行地址所对应的行开始被刷新。在刷新过程中,列地址信号CAS#一直保持高电平,处于无效状态。整个刷新过程的时序图如图2 所示。图中tRC为读周期,tRAS为行地址设置时间,tRP为行地址预充电周期[3]。

DRAM 控制器负责行地址的提供和对应行的刷新,并且确保在适当的时间内,将片内的所有行都刷新一次。需要注意的是,不管每一行的刷新次序如何设定,所有行的刷新必须在规定的时间内完成。

3.2 CAS#-before-RAS#刷新

CAS#-before-RAS#刷新又称为CBR 刷新,或者自动刷新(auto-refresh[4])。这种刷新方法具有使用方便,功耗较低的特点,是最常见的一种刷新方法。CBR 刷新是从CAS#信号由高电平变成低电平后,RAS#信号由高电平变成低电平时开始执行。以后,每当RAS#信号有效时,就执行一个刷新周期。需要注意的是,当RAS#信号有效时,WE#信号必须保持高电平,不允许进行写操作。

在DRAM 的刷新模块内有一个内部计数器。当刷新模块上电后,该内部计数器被初始化,设置一个随机计数值。每次进行CBR 刷新时,由内部计数器来确定哪一行被刷新,该行被刷新后,内部计数器的计数值自动加1。当再次进行CBR 刷新时,下一行被刷新,刷新完毕后,内部计数器计数值又自动加1。依此类推,DRAM 的所有行都会被轮流刷新。当计数器的计数值达到最大值时,计数器会自动清零,并继续计数。整个刷新过程中,每一行的刷新,都不需要外部地址。

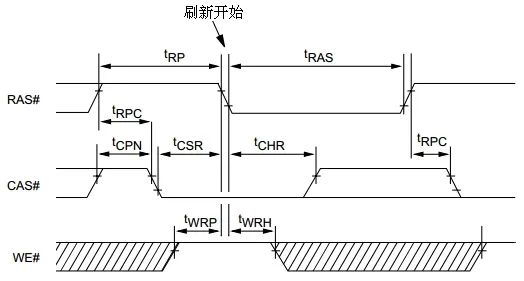

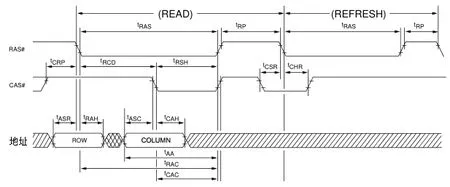

图3 所示为一个CBR 刷新周期的时序图。从CAS#信号低电平有效开始,到RAS#信号变为低电平有效,这段时间为tCSR,即列地址设置时间。从RAS#信号低电平有效开始,到CAS#信号变为高电平无效,这段时间为tCHR,即列地址保持时间。如果多个刷新操作连续进行时,CAS#信号将一直保持低电平有效状态,每次RSA#信号变为低电平有效时,就开始进行一个刷新操作。

由于CBR 刷新使用内部计数器来确定哪些行被刷新,因此不需要外部地址。在刷新过程中,地址缓冲器一直处于关闭状态,不需要额外的功耗向总线传送行地址信号,从而可以降低DRAM 的功耗。

3.3 隐蔽刷新

图4 所示为一个隐蔽刷新的时序图。

隐蔽刷新是一种特殊的刷新方式,刷新是在DRAM 空闲时才进行,即在DRAM 不进行读、写操作时进行,它不影响DRAM 的正常读、写操作。隐蔽刷新一般是将存储周期分为读、写周期和刷新周期两部分[5]。读、写操作与刷新操作分开,互不干扰,因此刷新总是在一个读、写操作之后进行。

图3 CAS#-before-RAS#刷新

在进行隐蔽刷新时,需要在刷新之前先进行一个读操作或者写操作,然后再进行刷新操作。图4所示隐蔽刷新为一个读操作之后进行的刷新。在进行隐蔽刷新时,RAS#信号由高电平变为低电平有效,在经历行寻址和列寻址时钟周期的差值即tRCD时间后,CAS#信号由高电平变为低电平有效。当CAS#信号经历RAS#保持时间即tRSH后,RAS#信号由低电平变为高电平,进入tRP行地址预充电时间。当读操作结束后,进行刷新操作。在整个过程中,由于刷新开始之前CAS#信号已经变为低电平有效,刷新开始时RAS#才变为低电平有效,因此相当于执行的是一个CBR 刷新(事实上不是一个CBR 刷新)。在这个CBR 刷新周期中,包含了正常读周期中的tRP和刷新周期中的tRAS,因此在读周期读出的数据将会一直保持有效至刷新结束,而这一现象恰恰是隐蔽刷新中隐蔽的意义所在。换句话说,隐蔽刷新隐蔽的不是刷新过程所耗费的时间,而是在刷新过程中,数据总线上一直有读周期读出的有效数据,好像是在进行读操作,没有进行刷新操作一样。在隐蔽刷新中,读操作占用的时间和刷新操作占用的时间都是tRC,总时间为2tRC。

图4 隐蔽刷新

图5 所示为一个读周期后进行CBR 刷新的时序图。

图5 中所示,一个读周期结束,紧跟着执行一个CBR 刷新周期。读周期占用时间为tRC,CBR 刷新周期占用时间也为tRC,总时间为2tRC,这和隐蔽刷新中读操作和刷新操作占用的时间相同。需要注意的是,隐蔽刷新在刷新过程中,数据总线上有有效数据的输出,而CBR 刷新过程中,数据总线上没有有效数据的输出。

图5 读周期后的CBR 刷新

4 结束

对于一个标准的DRAM存储器,一般都支持RAS#-only刷新,CAS#-before-RAS#刷新和隐蔽刷新三种刷新方法。每一种刷新方法既可以应用到分散式刷新方式中,也可以应用到集中式刷新方式中。至于应用哪种刷新方法最合适,需要根据设计者的使用需求而定。随着DRAM的发展,越来越多的DRAM刷新都采用CBR刷新方法。可以预见,在不久的将来,CBR刷新方法将有可能替代其他两种刷新方法,成为DRAM刷新技术中惟一的刷新方法。因此,建议设计者在进行DRAM刷新相应设计时,采用CBR刷新方法。