PR9200芯片的超高频RFID读写器通信技术

曹丹丹,景为平

(南通大学 江苏省集成电路设计重点实验室,江苏 南通 226019)

0 引 言

无线射频识别(Radio Frequency Identification,RFID)技术在零售业、食品溯源、制造业等领域得到广泛应用并取得良好的效果。PR9200芯片是一款高度集成芯片,内部高效集成ARM Cortex TM-M0处理器、超高频(Ultra High Frequency,UHF)、射频模块以及基带调制解调器等,并且包含UART、SPI、I2C等外设。与同类产品,如R1000芯片相比,PR9200芯片在价格上占有优势,且内部集成了MCU及各种接口。PR9200芯片的UHF RFID读写器在体积、低功耗以及成本上的优势远大于其他同类产品。

相较于大功率的RFID读写器而言,PR9200这款小功率读写器一般作为手持式读写器或是嵌入到其他主系统中,如:作业现场货物的入库、出库、盘点、基本信息录入和工厂自动化生产等。针对这些对操作速度有要求的应用,目前市面上的小功率读写系统的通信速度远远没达到理想要求。本文为PR9200芯片的读写器通过将串口通信改成网口通信且加入FPGA处理部分程序来设计一个高速稳定的通信系统,并对测试结果进行比较和分析。

1 数据通信总体架构

目前市面上的小功率读写器大多以串口或USB接口方式与上位机界面通信,但在实际应用中,考虑到数据传输速度以及参与工厂管理系统的实时性,网口实现方式是最佳的选择。基于PR9200芯片的UHF RFID读写核心模块通过网口与PC相连,PC机中的上位机程序通过事先约定的通信协议发送数据,网口监听到数据后,再传给FPGA。FPGA提供数据包解析,判断数据包完整性、CRC校验、消息类型是否正确、打包数据返回上位机等功能,FPGA旨在通过并行处理数据来提高数据处理的速度。

FPGA处理后的数据发往MCU,MCU接到操作命令并调用相应的函数;函数返回得到的值经过FPGA组包后由网口反馈给上位机软件,如图1所示。

图1 数据通信架构

2 数据传输协议

通信协议是指通信双方的一种约定,约定包括对数据格式、传输速度、检纠错方式以及控制字符定义等问题作出的统一规定,通信双方必须共同遵守。

2.1 帧结构设计

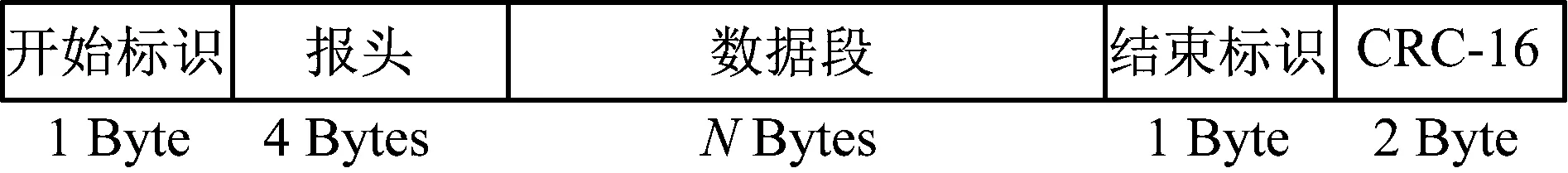

数据包格式如图2所示,开始标识和结束标识都具有固定值。

图2 通信协议据帧格式

开始标识(start_mark):表示1个数据帧的开始,本协议约定为0xEE,占1 Byte。

报头:报头由消息类型(msg_type)、控制代码(code)、数据长度(length)3部分组成。其中消息类型用于指示数据类型,分别为命令0x00,反馈0x01,通知0x02,消息类型占1 Byte;控制代码用于指示控制命令类型或反馈类型,本协议的控制代码主要有读标签(0x22)、写标签(0x44)、盘存标签(0x11)以及读写器的其他基本设置,占1 Byte;数据长度用于指示数据段的有效长度,有效长度用2 Byte表示。

数据段:包含数据或者控制信息,具体取决于数据包类型。对于命令数据包,控制信息置于此;对于响应和通知数据包,数据信息被置于此。

结束标识(stop_mark):表示一个数据帧的结束,协议约定为0x7E,占1 Byte。

CRC码:为了校验的准确性,采用循环冗余校验码,从数据帧开始标识字段到结束标识字段的所有消息位计算16位CRC(X16+X12+X5+1),初始值为0xFFFF。生成的CRC值应附加到数据包的末尾并发送。每个字节的最高有效位应首先发送。CRC校验码用2 Byte表示。

2.2 FPGA与上位机的网口通信设计

相较于单片机的单步处理而言,FPGA并行处理数据的能力大大提高了数据处理的速度,且相较于常用的串口,网口传输速度更快,也更适用于工厂或企业的管理系统。

本文采用百兆以太网数据传输,选用主流的TCP/IP协议,网口通信总体设计如图3所示,主要包括物理层PHY模块、MAC控制模块、协议处理模块、数据缓存FIFO。FPGA选用实验室现有的Altera Cyclone IV系列,PHY物理层选用PHY Ethernet模块。

图3 百兆以太网数据传输

MAC层发送模块的状态转换如图4(a)所示,共有7个状态。① 系统复位之初处于初始状态Idle,当rx_finish(接收数据结束)信号到来时,进入Start状态;② Start状态:写入各层首部,进入Make状态;③ Make状态:生成首部的校验,进入Send_mac状态;④ Send_mac状态:发送MAC的前导码和地址,进入Send状态;⑤ Send状态:发送IP数据包和TCP数据包的首部,判断处于TCP控制的哪个状态,若是在连接状态,则进入Link状态,等待握手成功。若是在释放状态,则进入Rel状态,等待下次连接的请求;若是在已建立连接状态则进入Send_data状态;⑥ Send_data状态:发送缓存在FIFO中的数据,进入Send_crc状态;⑦ Send_crc状态:发送MAC帧数据的CRC校验值,最后跳转到Idle状态,等待新发送触发的到来。

(a)MAC发送状态

(b)MAC接收状态

图4 MAC工作示意图

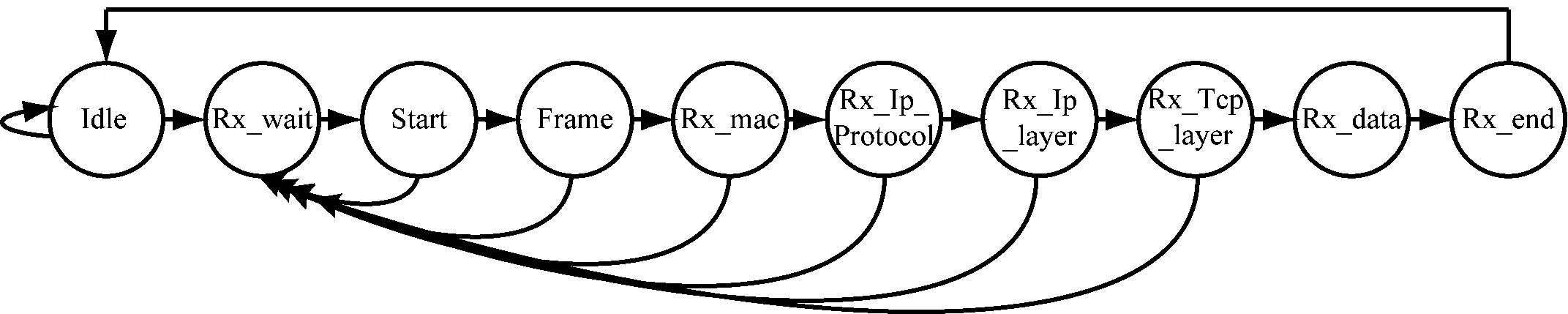

MAC接收模块的状态是发送模块的反过程,状态转换图如图4(b)所示,共10个状态。① 系统复位之初处于初始状态Idle:等待Tx_finish(发送数据结束)信号到来,进入Rx_wait状态;② Rx_wait状态:判断并接收前导码,判断到第1个0x55,进入Start状态;③ Start状态:接收剩下的6个0x55,接收完成后进入Frame状态;④ Frame状态:接收并判断帧起始定界符,判断正确则进入Rx_mac状态;⑤ Rx_mac 状态:接收目标地址和源地址,进入Rx_Ip_Protocol状态;⑥ Rx_Ip_Protocol状态:接收2 Byte IP类型,跳转到Rx_Ip_layer状态;⑦ Rx_Ip_layer状态:接收TCP虚拟包头以及IP地址,进入Rx_Tcp_layer状态;⑧ Rx_Tcp_layer状态:接收TCP数据包头,端口号等,进入Rx_data状态;⑨ Rx_data状态:接收TCP数据,进入Rx_end状态;RX_end状态:接收数据完成,跳转到Idle状态,等待发送触发的到来。

2.3 MCU与FPGA通信设计

MCU选型则由PR9200芯片自带的内部ARM Cortex TM-M0,MCU与FPGA之间的数据传递是通过单片机的外部中断机制来实现。MCU引脚采用P17、P10、P12、P13、P14、E6、E7这7个端口与FPGA完成通信,相应的引脚连接以及功能意义如表1所示。

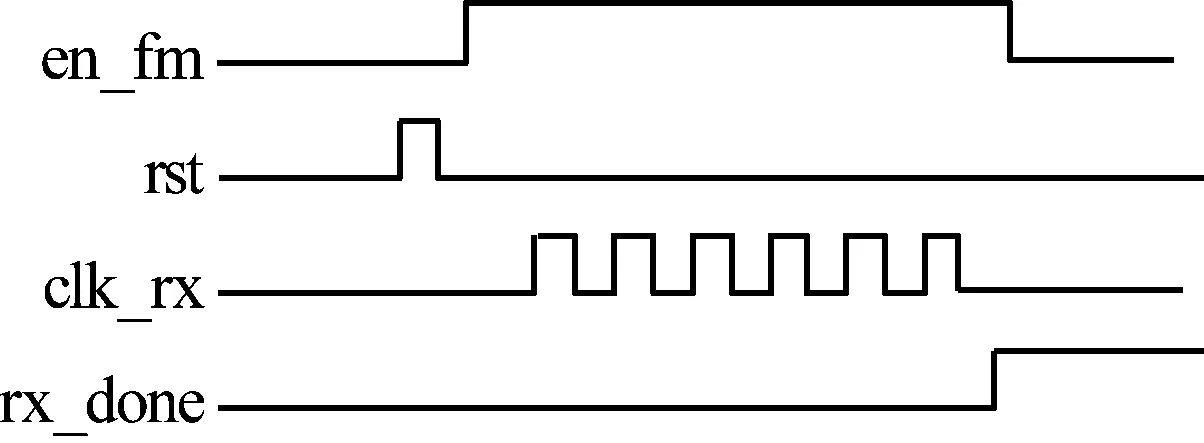

FPGA向MCU发送数据:FPGA判断完消息类型后,产生复位信号rst,准备向MCU发送数据。首先FPGA 给MCU发送接收使能信号(en_fm),通知MCU准备接收信号;然后FPGA将同步时钟信号(clk_rx_50 MHz)送至MCU中断0处,FPGA在clk_rx_50 MHz信号的上升沿向数据通信口(data)发送数据,MCU在clk_rx_50 MHz信号的下降沿向数据通信口(data)接收数据;当MCU数据接收结束,返回数据接收完成信号(rx_done),并将接收使能信号(en_fm)拉低,如图5所示。

MCU向FPGA传递数据:MCU向FPGA发送复位信号rst。首先MCU给FPGA发送接收使能信号(en_mf),通知FPGA准备接收数据;然后FPGA将clk_tx_50 MHz信号送至MCU中断1,MCU在clk_tx_50 MHz信号的下降沿时向数据通信口(data)发送数据,FPGA在clk_tx_50 MHz信号的上升沿时接收数据通信口(data)接收数据;当FPGA数据接收结束,返回数据接收完成信号(tx_done),并将接收使能信号(en_mf)拉低,如图6所示。

表1 FPGA与MCU管脚连接

图5 FPGA向MCU传递数据

图6 MCU向FPGA传递数据

2.4 数据包处理流程

上位机发送的数据包经网口传送至FPGA,FPGA对接收到的数据进行并行处理。由数据的开始标识、数据有效长度以及结束标识来判断数据包的完整性。若数据包不完整直接跳出程序,返回错误代码DATA_ERROR(10),错误代码进入组包函数Pack_write(),Pack_write()函数是将返回的代码按照通信协议打包成约定格式传给上位机。否则进行CRC校验,CRC检验错误则直接返回CRC_ERROR(20)表示CRC错误,由组包函数Pack_write()组包并传给上位机否则进行消息类型判断,如果不是对应的消息类型,那么返回Not_Support cmd(30)指令,表示不是支持的代码类型。case语句实现控制命令(code)的识别处理,返回的关键数据再传到MCU中断,调用对应的函数。具体处理流程如图7所示。

图7 数据处理流程

3 通信系统实现与测试

为测试本文设计的基于PR9200模块通信协议的高速稳定性,对FPGA与上位机之间的网口通信进行使用Quartus II自带的Signal Tap II工具进行仿真,利用上位机测试指定时间中PR9200读写器能读到的指定标签的数量。

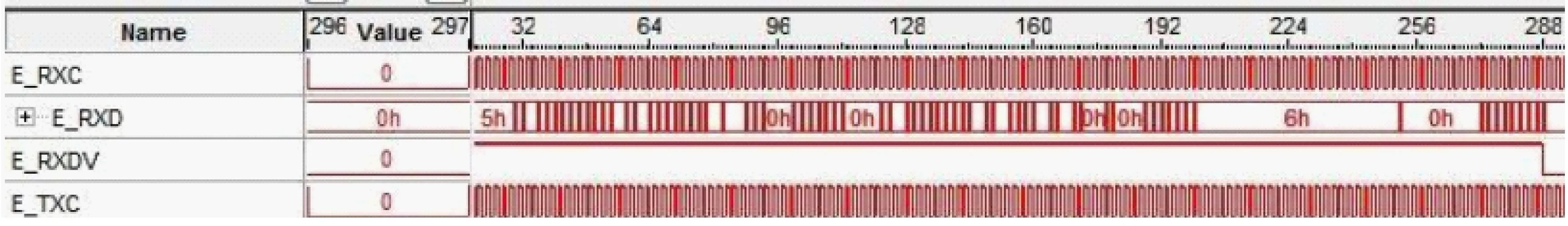

3.1 网口通信测试

使用Quartus II自带的Signal Tap II工具进行仿真,Signal Tap II是嵌入式逻辑分析仪工具,工程中加入中.stp文件,相当于在FPGA内部接入一个数字示波器,可以观察到FPGA内部的任何信号。图8(a)、(b)为PC端发送一串数据时,在Signaltap II上抓到的数据波形,图8(c)为波形图放大之后,对其作的解释说明。

(a)以太网口接收数据波形

(b)以太网口发送数据波形

(c)以太网发送(接收)数据波形放大图

3.2 上位机实测

在上位机软件给定时间2 s对同一个标签自循环读取,并记录读到标签的个数如图9所示,可以测得在固定时间2 s内,能读取标签110个,相比图10用串口通信且未加FPGA进行数据处理的通信系统,平均每秒多识别了20个标签。

图9 改后通信系统读取标签

图10 原始通信系统读取标签

4 结 语

本文将PR9200读写器的通信过程加以改善,首先网口在提高通信速度的同时,也更有利于该读写器应用于物联网系统中,便于使用于工厂车间等管理系统中。其次使用FPGA来实现一部分数据的并行处理,在确保稳定性不变的前提下显著提高了读写器的数据处理速度。下一步的研究方向将着重于增强整个通信系统的可靠性、保密性以及可扩展性。