双通道5 GS/s高速数据采集卡设计

刘 鸣,孙秀男,梁 昊

(1.中国科学技术大学 核探测与核电子学国家重点实验室,安徽 合肥 230026;2.中国科学技术大学 近代物理系,安徽 合肥 230026)

0 引言

雷达、声呐、核探测器等仪器输出的高频信号频率有时可以接近GHz,对于这些信号的采集需要更高的采样率和精确度,因此GS/s高速数据采集系统是近年来数据采集领域的研究主流[1-4]。目前GS/s高速ADC一般都是采用时间交替并行采样结构(Time Interleaved ADC,TIADC),而大部分的GS/s高速数据采集系统是采用单片GS/s高速ADC,虽然能够让单片ADC工作在多通道模式从而可以采集多通道的模拟输入信号,但是这样会降低ADC的采样率从而不能满足高频信号采样的要求。

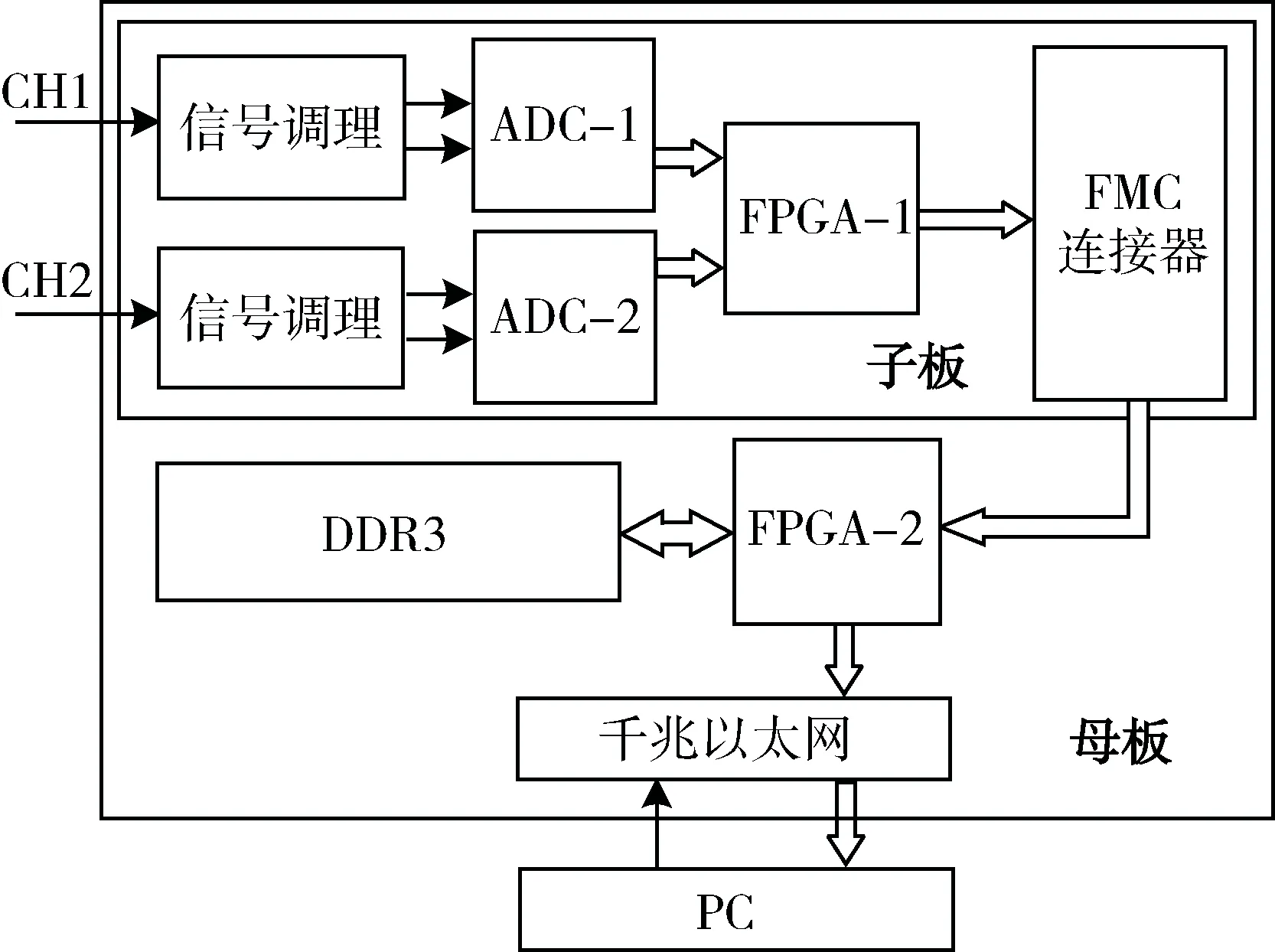

本文针对双通道高频信号输入的场景,提出一种双通道5 GS/s采样的高速数据采集卡的实现方案。采集卡使用两片型号为EV10AQ190的10位、5 GS/s 高速ADC,利用FPGA夹层卡(FPGA Mezzanine Card,FMC)设计成子母板结构,通过两片Xilinx公司的Vertex-6 FPGA来负责子母板的逻辑控制,母板利用DDR3进行数据存储并通过千兆以太网的方式传至上位机进行数据处理。通过性能测试,采集卡在双通道5 GS/s模式下采样100 MHz的正弦波,两片ADC的有效位都能达到8.0以上,能够满足GHz信号对高采样率和高精确度的要求。

1 采集卡总体设计结构

双通道5 GS/s高速数据采集卡总体结构如图1所示。采集卡采用扩展性极强的FMC连接器将数据采集子板和数据处理母板分离,方便今后对采集子板的升级或替换。子板接收通道1、2的模拟输入,通过信号调理模块对每个通道的信号进行调理,ADC1和ADC2接收两路调理信号并转换为实时的高速数字信号。FPGA1接收两片ADC输出的数字信号,并利用片内BRAM资源进行缓存。当FPGA1采集到目标大小的数据后,将BRAM中缓存的数据通过FMC连接器传输给母板,并在FPGA2控制下将数据存入DDR3中,最后通过千兆以太网将数据包上传至PC,从而完成数据的采集传输、接收缓存、存储上传的流程。整个流程中上位机通过对FPGA2的控制,间接地控制FPGA1,进而控制采集的开始与结束。

图1 采集卡总体结构图

2 采集卡子板硬件设计

采集卡子板的电路结构如图2所示,主要包括模拟信号调理模块、时钟产生与扇出模块、高速ADC采样模块、FPGA逻辑控制模块、电源模块等。另外考虑设计冗余性,还预留了外部的采样时钟、电源以及触发输入模块。

图2 子板电路结构图

2.1 模拟信号调理

信号调理是模拟信号采集不可或缺的前端部分,其结构如图3所示,主要包括幅度衰减电路、滤波电路以及单端转差分电路等。

图3 信号调理结构图

幅度衰减电路将输入模拟信号的幅度进行衰减,以满足ADC采样信号的电压范围。经过幅度衰减电路后的两路信号都通过低通滤波器,目的是滤除极高频率的噪声信号,采用无反射低通滤波器XLF-861+,其3 dB带宽为0~1 150 MHz,能够很好地满足设计要求。由于ADC的信号输入是LVDS输入,因此还需要对滤波后的信号进行单端转差分处理,选用巴伦型高速射频变压器ETC1-1-13,其3 dB 带宽为4.5~3 000 MHz。

2.2 高速ADC采样

两片EV10AQ190组成的ADC采样模块是数据采集子板的采样核心部分。EV10AQ190是一款10位、5 GS/s采样率、3.2 GHz输入带宽的多通道高速ADC。它基于TIADC结构,内置4个ADC核,四通道模式采样率为1.25 GS/s,单通道模式采样率5 GS/s[5]。本采集卡的两片ADC的采样模式如图4所示。ADC工作在单通道模式,即四ADC核交错采样率为5 GS/s。 ADC内部的多相时钟产生电路将时钟模块产生的2.5 GHz的时钟信号做二分频处理,然后分为四路相位差间隔为90°的1.25 GHz的时钟作为四个ADC子核的采样时钟,进行时间交替并行采样,从而实现单片ADC单通道5 GS/s的采样率。经过信号调理模块后的两路模拟差分信号分别进入ADC1的AAI、AAIN模拟输入通道和ADC2的DAI、DAIN模拟输入通道,两片ADC在两路扇出的时钟信号的驱动下,对这两通道的输入信号进行采集,从而实现双通道5 GS/s的信号采集。

图4 采集卡双通道ADC采样示意图

2.3 低抖动高速采样时钟设计

采样时钟的信号质量是影响采样性能最为关键的因素之一。衡量时钟信号质量的指标主要是孔径抖动,过大的孔径抖动会导致错误地触发采样,从而降低ADC采样数据的信噪比[6-7]。只考虑ADC的量化误差,信噪比SNR与时钟抖动tj的关系可以表示为[8]:

(1)

式中n是ADC的转换位数,f是输入模拟信号频率。

由式(1)可知,在输入信号频率和孔径抖动tj确定的情况下,系统信噪比会随ADC转换位数n的增加而升高,因此可以采用高分辨率ADC来提高采样系统的信噪比。而当ADC转换位数n确定时,在采样低频信号时,系统对时钟抖动的要求不高,但是当采样高频信号时,系统的信噪比将主要取决于总的时钟抖动。为满足高速数据采集对高质量低抖动时钟的要求,基准时钟源和时钟发生器的输出时钟抖动都要尽可能地低。本采集卡的时钟方案如图5所示。采用时钟抖动为40 fs的超低噪声压控振荡器CVHD-950-50作为基准时钟源,通过时钟抖动为97 fs的高性能时钟发生器HMC1035产生2.5 GHz的高速时钟,然后经过低噪声时钟扇出缓冲器HMC6832将时钟扇出为两路,作为两片ADC的采样时钟。

图5 低抖动高速采样时钟方案框图

3 采集卡FPGA逻辑设计

3.1 数据采集子板FPGA逻辑设计

子板FPGA作为数据采集子板的控制核心,其内部逻辑主要包括ADC高速数据接收、数据整合与读写控制、数据缓存BRAM、时钟发生器的SPI配置、两片ADC的SPI配置等模块。子板FPGA的整体逻辑框图如图6所示。

当两片ADC工作在5 GS/s模式时,ADC内部四个ADC核(A、B、C和D)交错采样,两片ADC共输出80对差分数字信号以及8对随路时钟信号。FPGA内部逻辑首先要做的就是准确无误地接收ADC的高速数字信号。ADC数据输出为DDR模式,因此随路时钟速率是数据速率的一半只有625 MHz,但FPGA内部的普通逻辑资源仍是难以处理,需要采用串并转换单元将数据速率降低下来。

ISERDES是Xilinx公司FPGA内嵌的高速串并转换器,其IP核内部包含的IODELAY模块提供了一种基于源同步的高速数据接收技术,能针对高速数据在传输路径上造成的延时进行调整,使源同步时钟与数据满足时序关系。IODELAY有64级可调延时,步长精度最高可达78 ps[9]。采用8个6倍转换率的ISERDES接收两片ADC的输出数据,将80 bit位宽的数据转换为480 bit位宽的数据,这样输出的数据速率变为208.33 MHz,然后经过8个异步FIFO进行跨时钟域处理,将数据的驱动时钟从随路的局域时钟变为PLL模块产生的250 MHz的全局时钟,方便后续的数据处理。

图6 数据采集子板FPGA逻辑框图(x=A,B,C or D)

由于ADC的四个核交错采样,又经过6倍的串并转换,因此480 bit数据的顺序是错乱的,需要重新排序,另外考虑母板DDR3数据输入宽度为256 bit,需要做数据位宽的匹配,因此加入32 bit的无效0数据,使总的数据位宽变为512 bit。数据整合的具体方法如图7所示。

图7 数据整合示意图

以ADC1为例,假设N为ADC1当前采样周期的第一个采样点。4个ADC核的采样方式是按照图中的顺序交错进行的。每个ISERDES接收ADC核的6个采样周期的数据,串并转换后将第一个采样数据放在低位,最后一个采样数据放在高位。数据整合逻辑将ADC核输出的交错数据按照采样顺序进行重新排序,并且将第一个采样数据放在高位,最后一个采样数据放在低位,从而可以符合后续FIFO与BRAM的读写时序。重新排序过程中,在最高位插入8 bit的无效0数据,然后隔12个数据后再插入8 bit的0数据。这样ADC1的24个并行采样数据从原来的240 bit经过整合变为256 bit。

整合后的两片ADC的512 bit数据输入到BRAM进行缓存,考虑到子板通过FMC接口到母板的数据接口为32位,需要将数据位宽降下来,而FIFO不能直接进行512位到32位的转换,因此先要利用异步BRAM将512位降至256位。由于数据流向是单向的,采用简单双端口BRAM,其容量设为1 MB。当BRAM存满后停止数据的接收,开始从BRAM读出,经过一个FIFO将数据位宽降至32位然后通过FMC传输至母板。

3.2 数据处理母板FPGA逻辑设计

母板FPGA作为数据处理母板的控制核心,其内部逻辑主要包括数据接收、DDR3接口控制、千兆以太网接口控制、上位机接口控制等模块。母板FPGA的整体逻辑框图如图8所示。

图8 数据处理母板FPGA逻辑框图

上位机接口控制模块是FPGA逻辑的控制中枢,它接收上位机命令信息进行解析,并结合各个FIFO的空满状态、DDR3的空满状态来控制整个数据传输流程。

数据接收模块仍采用源同步的方法,同时接收子板发送过来的数据与随路时钟。其中接收的时钟信号利用BUFR(区域时钟缓冲器)使其可以驱动其区域内的所有的IO和内部逻辑,数据信号则利用一个写FIFO实现缓存、位宽匹配、时钟域转换等功能。DDR3接口控制模块和千兆以太网接口控制模块利用了Xilinx公司提供的IP核。在上位机接口控制模块的控制下,数据经过前置写FIFO缓存后通过DDR3 IP核存入内存条,当DDR3存满后再读出,经过后置FIFO中缓存后进入到MAC层IP核,最后利用物理层芯片88E1111将数据上传至上位机[10]。

4 采集卡性能测试

4.1 ADC静态性能测试

ADC的静态性能指标描述ADC的内在特性,关注于ADC在稳定输入的情况下数字输出与对应模拟输入之间的关系。其中微分非线性(Differential Nonlinearity,DNL)和积分非线性(Integral Nonlinearity,INL)衡量了ADC的线性精度。利用码密度直方图法可以计算DNL、INL,当ADC1、ADC2都工作在5 GS/s 模式,测试结果如图9、表1所示。可以看出ADC1、ADC2的DNL和INL在输出的数字码范围内分布良好,且DNL在±0.5 LSB以内,INL在±1 LSB以内。

ADC模式DNL(LSB)INL(LSB)MINMAXMINMAXADC1-ABCD-0.410.30-0.800.78ADC2-ABCD-0.500.42-0.950.98

4.2 ADC动态性能测试

ADC的动态性能指标是衡量ADC在交流条件下采集转换交变信号的能力,主要包括信噪比(SNR)、信纳比(SINAD)、无杂散动态范围(SFDR)、有效位(ENOB)等。采用FFT快速傅里叶变换可以实现信号从时域到频域的变换,再利用其频谱图就能够方便地提取到ADC的相关动态性能参数。

双通道采样模式下,两片ADC都工作在5 GS/s模式,采用100 MHz正弦波双通道输入,先对输入波形进行重现,如图10所示。然后做FFT得到对应频谱图,如图11所示,可见重现波形稳定平滑无毛刺,频谱图中信号频率分布良好,谐波较低噪声较小。利用频谱图量化计算,可以得到两片ADC的动态性能参数,如表2所示,可见ADC1、ADC2的单核1.25 GS/s及四核5 GS/s有效位都能达到8.0以上,其SINAD、SNR、SFDR也都较高。

图10 输入100 MHz正弦波采样重现波形图

图11 输入100 MHz正弦波FFT频谱图

表2 ADC动态参数测量表

5 结论

本采集卡利用两片10位5 GS/s的高速ADC,实现了对双通道高速数据的采集传输、接收缓存、存储上传的功能。采集卡在双通道5 GS/s模式下,两片ADC的静态性能与动态性能良好,有效位达到8.0以上,满足对双通道高频信号采集的设计要求。另外由于本采集卡采用扩展性极强的FMC子母板的方式,数据采集子板能方便地根据需求进行升级,如更多通道采样或多片ADC交错采样提升整体采样率等方案,有待进一步的研究实现。