线阵CCD输出特性测量系统设计

程 瑶,甘婷源

(重庆理工大学机械工程学院,重庆 400050)

0 引言

图像传感器是以光学理论为基础,包括计算机应用、图像处理及半导体电路集成等技术,在光谱分析、几何尺寸测量、表面检测等领域的应用较广泛[1]。电荷耦合器件(CCD)的特性决定了应用系统的质量,为了提高系统测量的精度,对图像传感器输出特性的研究有重要的意义[2]。本文即针对典型的线阵CCD 图像传感器TCD1209D,构建CCD输出特性测量系统,设计了一个基于FPGA的线阵CCD输出特性测量系统,实现图像数据采集、数据缓存以及与PC机进行数据传输等功能,对CCD器件积分时间、驱动频率、输出信号幅度等进行测量,以此对特性进行分析。

1 典型线阵CCD TCD1209D

TCD1209D是一款低噪声、高灵敏度、宽动态范围的线阵CCD图像传感器,其最佳工作频率为1 MHz,最大驱动频率可达20 MHz,作为二相单沟道型线阵CCD器件,TCD1209D的驱动时序、电路及结构原理等都具有典型性。可用于传真和图像扫描。中心间距为14 μm,大小为14 μm×14 μm的像元点;2 048个有效像元;光敏区域由低暗电压信号和高灵敏度的光电二极管组成;封装形式为DIP22的双列直插型图像传感器件。

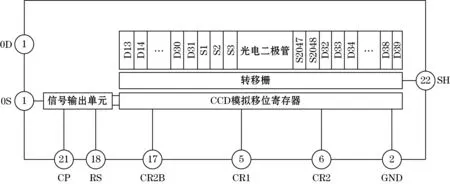

TCD1209D的原理结构如图1所示。从图1可以看出,TCD1209包含1个模拟移位寄存器与1个转移栅。其光敏阵列中含有2 075个光电二极管,其有效光敏单元是中间2 048个S1-S2048,前D13~D31与后D32~D39共27个是被遮挡的。

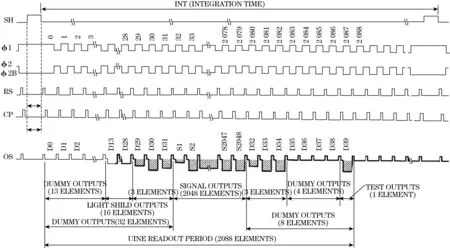

TCD1209D的驱动信号时序要求如图2所示。包含转移脉冲SH、驱动脉冲CR1和CR2、复位脉冲RS以及控制脉冲CP。为了保证光敏区中的电荷信号能够向φ1电极上转移,φ1的高电平时间必须大于SH的高电平时间,且φ1的高电平在SH之前开始,在SH之后才结束。电荷转移完成后,要将模拟移位寄存器与光敏区隔离,因此将SH变为低电平。同时,在φ1和φ2作用下,向左转移模拟移位寄存器内φ1的电荷信号,然后得到被光调制的脉冲信号输出,即OS信号。

图1 TCD1209D原理结构图

图2 TCD1209D驱动脉冲时序图

为了保证CCD在转移行信号时能够正常工作,必须满足tINT>2 088Tφ1,使SH在转移下一行信号时上一行信号的完整性,即SH周期应大于等于2 088个φ1周期。SH由高电平变为低电平时,OS端开始输信号。由于前13个没有光电二极管与之对应,因此输出13个虚设信号,随之是光电二极管被遮蔽的16个哑元信号,然后是3个可能因光的斜射而产生电荷信号的输出信号,不用作信号处理,然后才输出有效像元信号2 048个,最后输出包含有1个结束检测信号的哑元信号8个[3]。

2 硬件设计

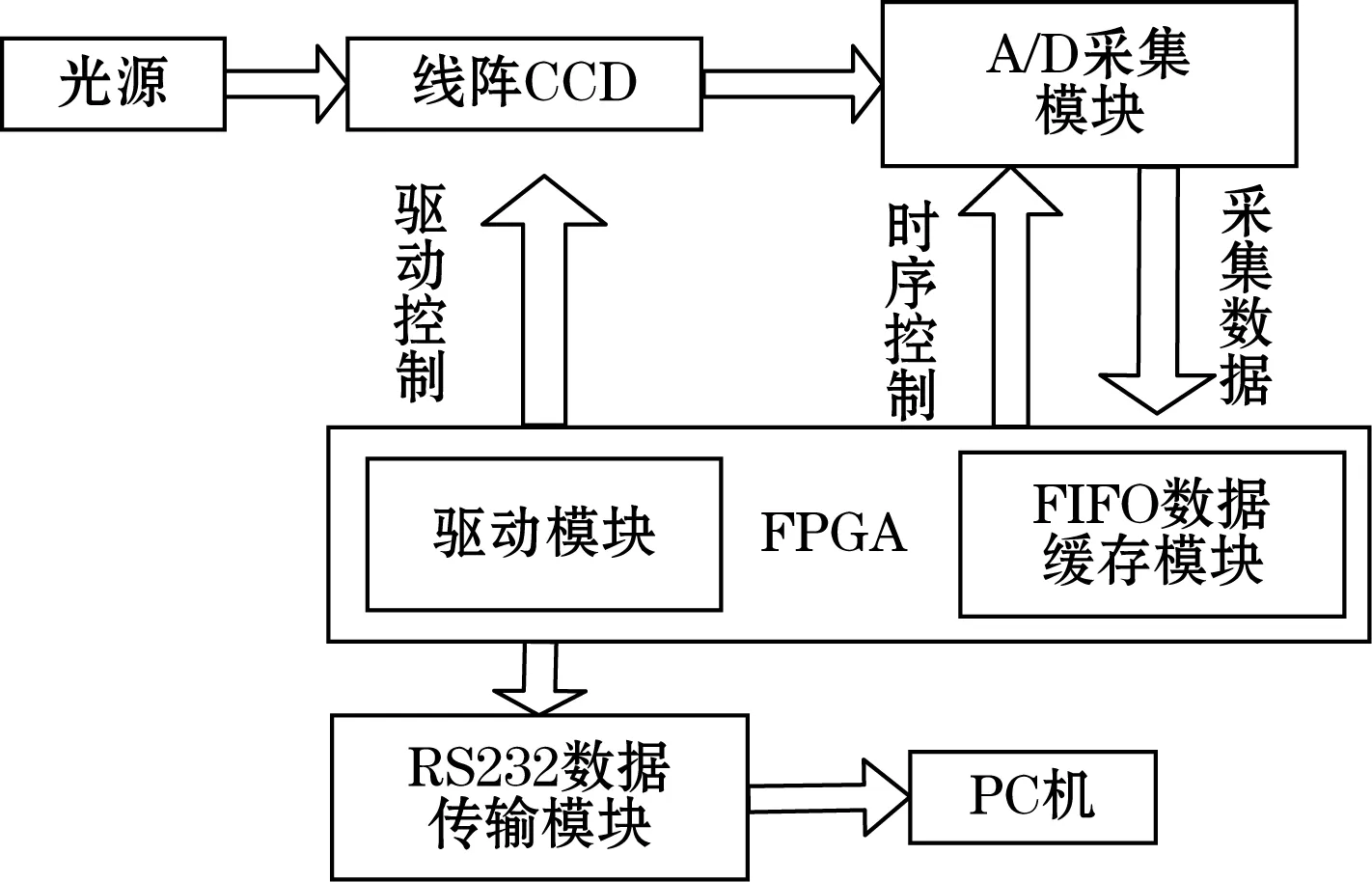

线阵CCD输出特性测量系统以FPGA为主控核心,主要包括:光信号源、线阵CCD传感器、驱动控制模块、A/D数据采集模块、FIFO数据缓存模块以及RS232数据传输模块。线阵CCD传感器由FPGA内驱动控制模块产生时序驱动,即线阵CCD TCD1209D的五路驱动信号,分别是SH、CR1、CR2、RS、和CP。数据采集模块由AD9822构成,其配置时序和驱动时序由FPGA产生。光源信号经线阵CCD传感器感应后,将光信号转换为了模拟的电信号。模拟的电信号经过A/D采集变为数字信号。经过处理后的数字信号缓存于FPGA中的FIFO中。最后再通过RS232串口将缓存的数据传至PC机。本系统整体框图如图3所示。

图3 系统整体框图

2.1 CCD驱动模块设计

在本系统的设计中,CCD驱动脉冲时序信号产生的正确性是保证后续电路得以继续进行的前提。只有驱动信号正常,传感器才能正常工作。在一定的驱动频率条件下,线阵CCD能够输出完整、可靠的信息[4-5]。

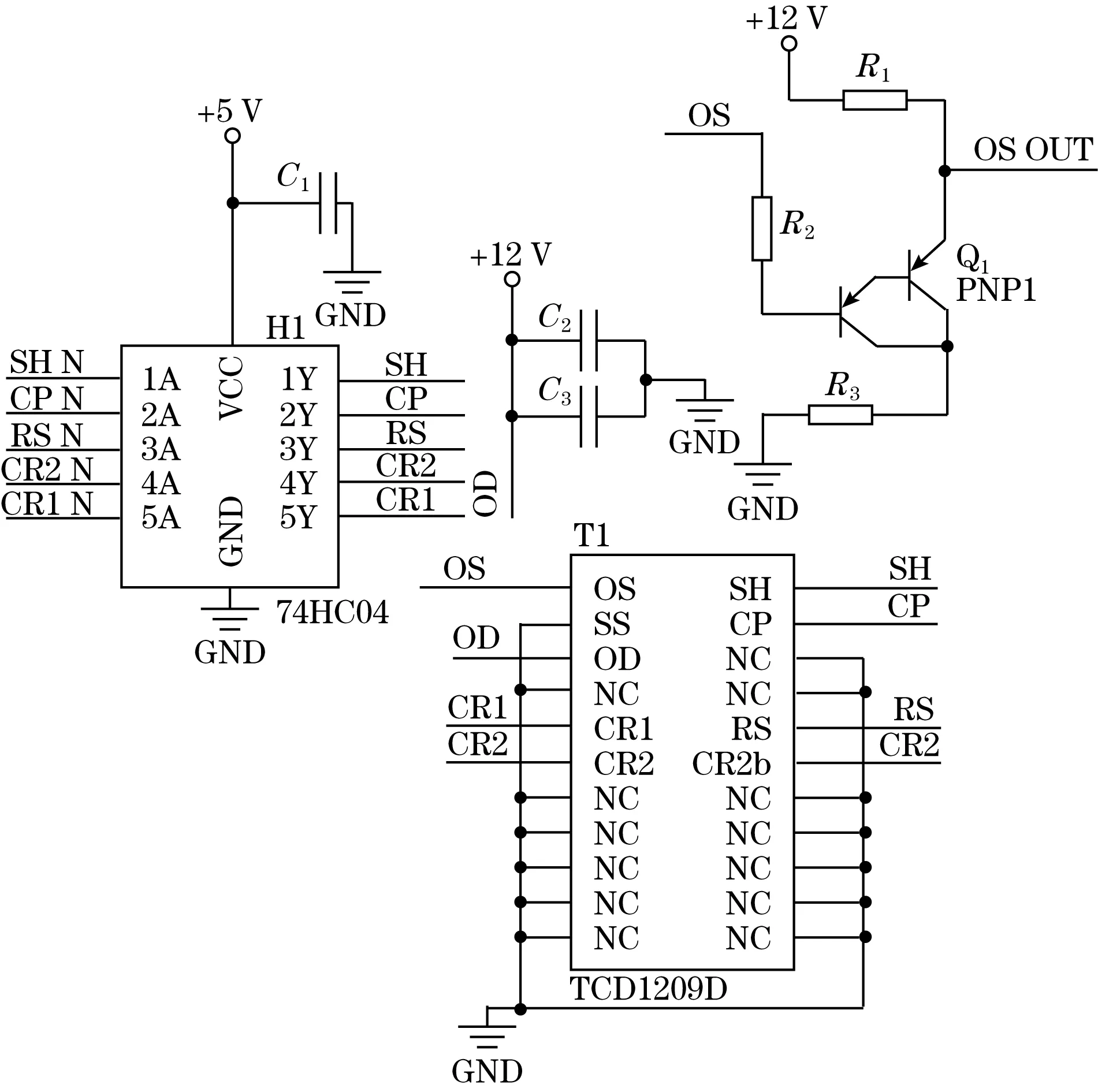

线阵CCD的驱动时序由FPGA控制核心产生。但由于线阵CCD的驱动脉冲的高电平最低值为4.5 V,而FPGA的I/O输出电压为3.3 V,采用74HC04作为CCD的输入驱动,但由于74HC04是反相器,因此在FPGA的输出端输出各路驱动信号的反相信号。对74HC04的特性进行分析可得,当供电电压大于4.5 V时,输出端的最小值为3.84 V,满足线阵CCD TCD1209 驱动时序的要求。CCD驱动外围电路的设计如图4所示。

图4 线阵CCD TCD12090硬件原理图

2.2 数据采集模块设计

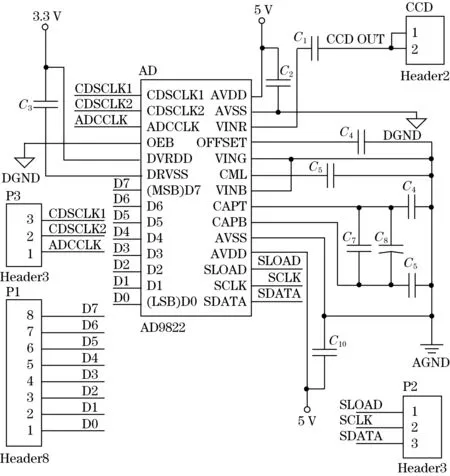

系统采用AD9822芯片作为系统的数据采集芯片。AD9822是一款专用于图像采集系统的模数信号转换器,三通道相关双采样(CDS)输入,可编程增益放大器(PGA),调理三线彩色阵列的输出[6-8]。

采用单通道CDS相关双采样时的电路设计如图5所示。其中C2、C3、C10为去耦电容,用于保证供电电压的稳定性,取0.1 μF。C1为0.1 μF滤波电容,使CCD产生的模拟信号经滤波输入AD,去除输入信号的直流分量。

图5 AD9822的外围电路图

2.3 数据传输模块的设计

RS232能够允许全双工的双向通讯,计算机可以同时接收数据和发送数据。最大的可支持传输速率为10 KBytes/s.

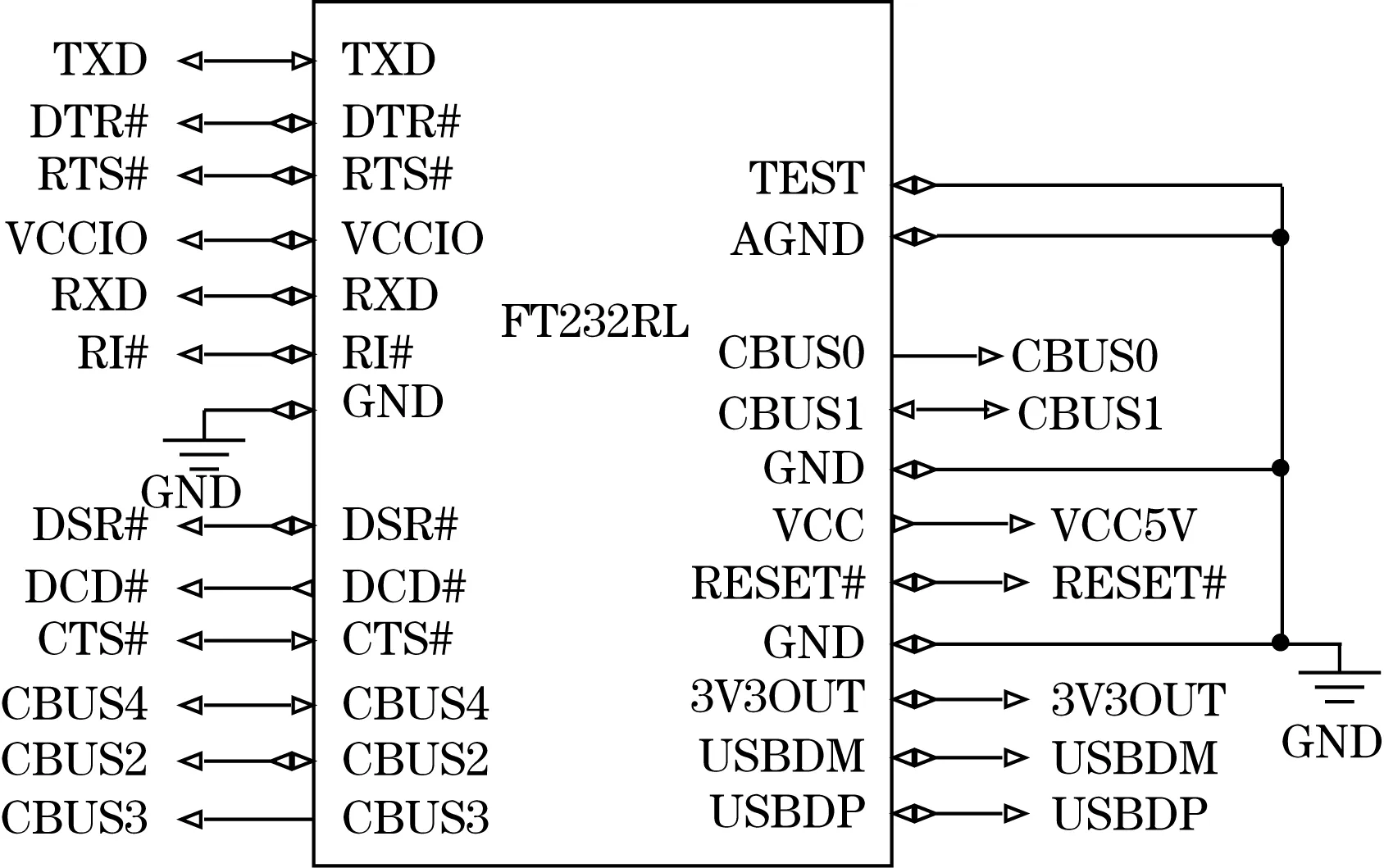

RS232的接口能够利用专用的芯片实现,这些芯片中还含有很多的辅助模块,如FIFO、调制解调器以及中断等。本系统RS232数据传输模块采用的是FT232RL芯片,其硬件电路图如图6所示。

图6 通信模块硬件电路图

串口发送模块采用FT232RL转换芯片,用于实现USB转换到串行UART数据传输模式。如图6所示,管脚TXD为数据发送输出,管脚RXD为数据接收输入。在本系统的实际应用中通过USB转TTL数据传输模块来实现。

3 软件设计

本系统的软件设计部分采用Verilog HDL语言来实现。软件设计包括对线阵CCD TCD1209D驱动时序设计,AD9822的配置和驱动时序设计,FIFO数据缓存模块设计和RS232串行数据模块驱动程序。

3.1 CCD驱动脉冲时序设计

通过FPGA内部逻辑,产生驱动脉冲信号[9]。包括转移驱动信号SH、模拟移位寄存器驱动信号φ1(即CR1)和φ2(即CR2)、复位驱动信号RS、缓冲脉冲信号CP。

通过对基准信号CLK四分频,利用各种计数器实现驱动信号的设计。

当计数值为0~3时,输出为1;当计数值为4~7时,输出为0。这样就产生了CR1信号,对CR1信号进行取反操作,就输出CR2信号。当计数值为0~1时,输出为1;否则输出为0。这样就输出了RS信号。再判断计数值为2~3时,输出为1,否则输出为0,这样就输出了CP信号。当计数值为0~2 088时,输出为0;当计数值为2 089~2 091时,输出为1。这样就得到SH信号。

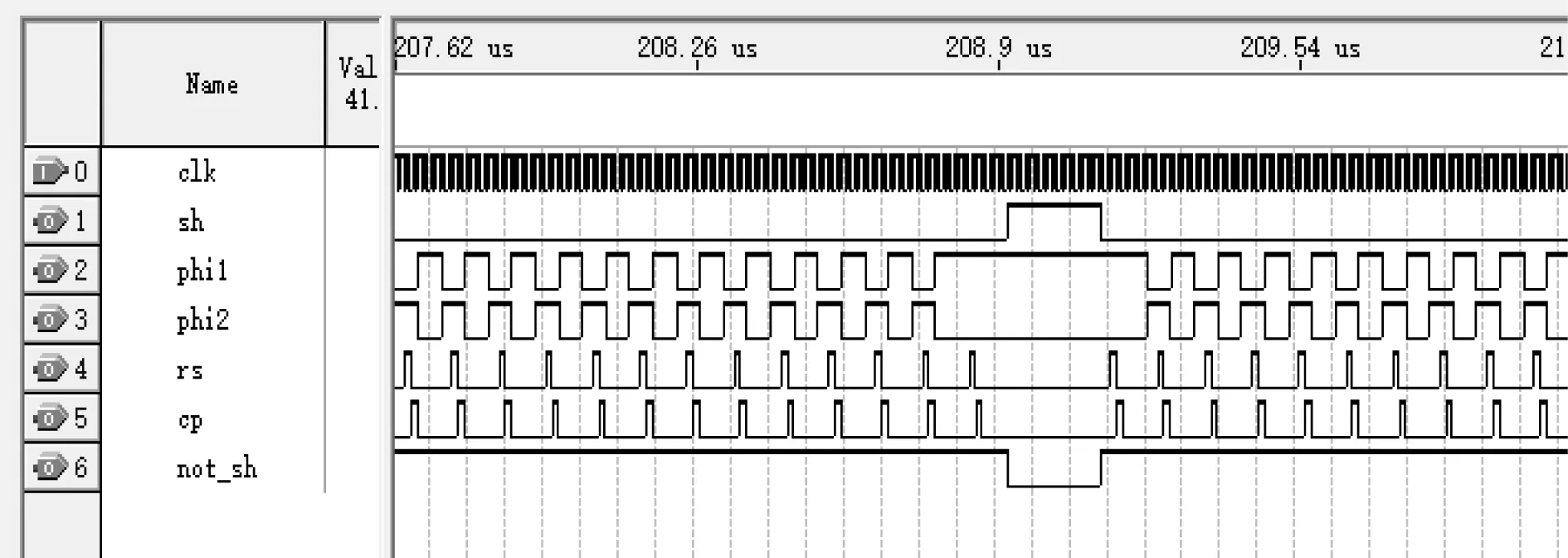

Quartus Ⅱ开发环境下,利用FPGA产生TCD1209D的驱动信号,并进行仿真,得到如图7所示的仿真结果。对照前文对TCD1209的时序要求,可得产生的驱动信号满足TCD1209D的驱动信号要求。

图7 TCD 1209D驱动时序仿真局部放大图

3.2 A/D采集时序设计

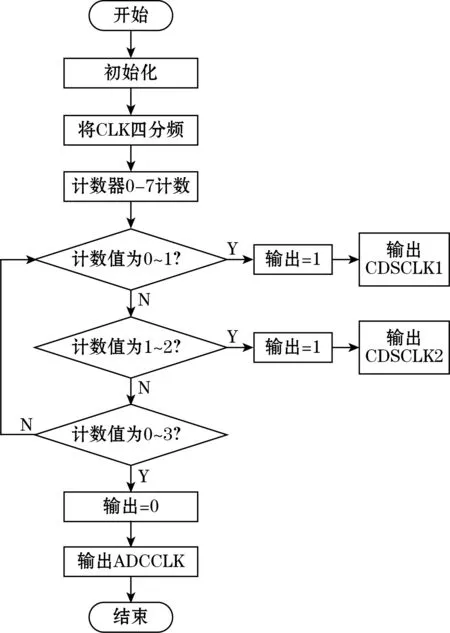

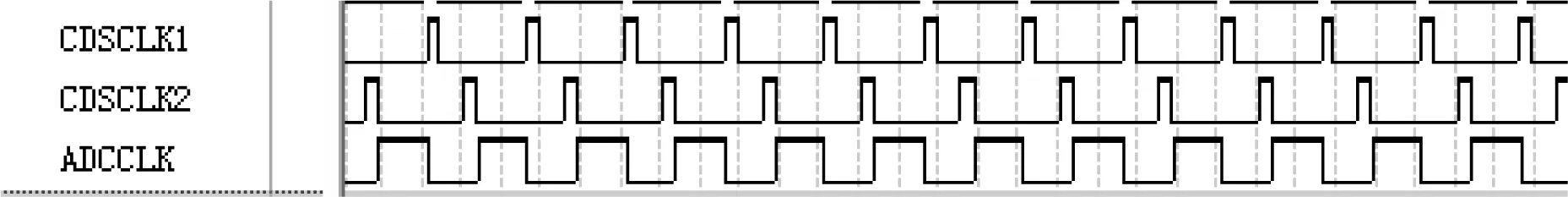

AD9822工作在单通道的CDS工作模式下,要求ADCCLK时钟与线阵CCD TCD1209D输出信号保持高度一致。由AD9822的时序图可得,CDSCLK1采集输入信号中的高电平点,CDSCLK2负责采集输入信号中的低电平点,AD9822内部比较控制信号为ADCCLK。且必须严格控制相关双采样的3个时序脉冲信号。通过Quartus Ⅱ环境下,设计流程编辑程序(图8),进行仿真,得到采集时序仿真图(图9)。

图8 AD9822采集时序的程序流程图

图9 AD9822采集时序仿真图

在ADCCLK的低电平范围内,首先输出CDSCLK1的高电平,然后接着输出CDSCLK2的高电平。对照AD9822的采样时序,可知满足要求。

4 实验结果

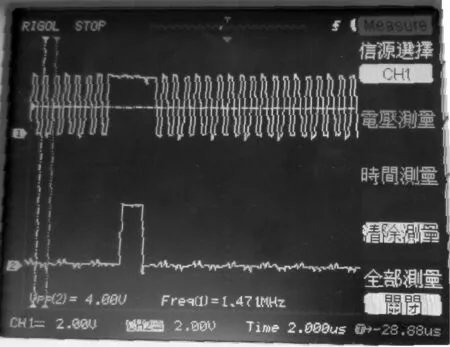

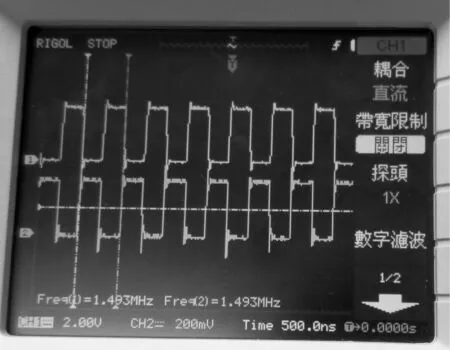

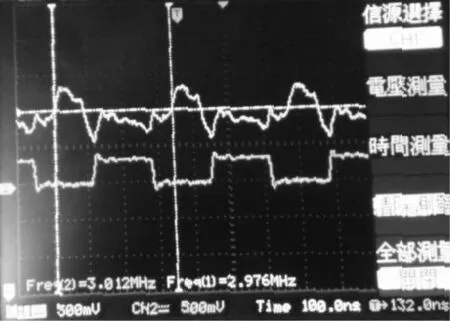

通过电路硬件设计,程序下载到FPGA开发板上,并通过示波器测试各个模块的输出波形,测试结果如图10、图11所示。对照TCD1209D的驱动时序,可知测试结果正确。

图10 SH和CR1驱动信号测试结果

图11 CR1和CR2驱动信号测试结果

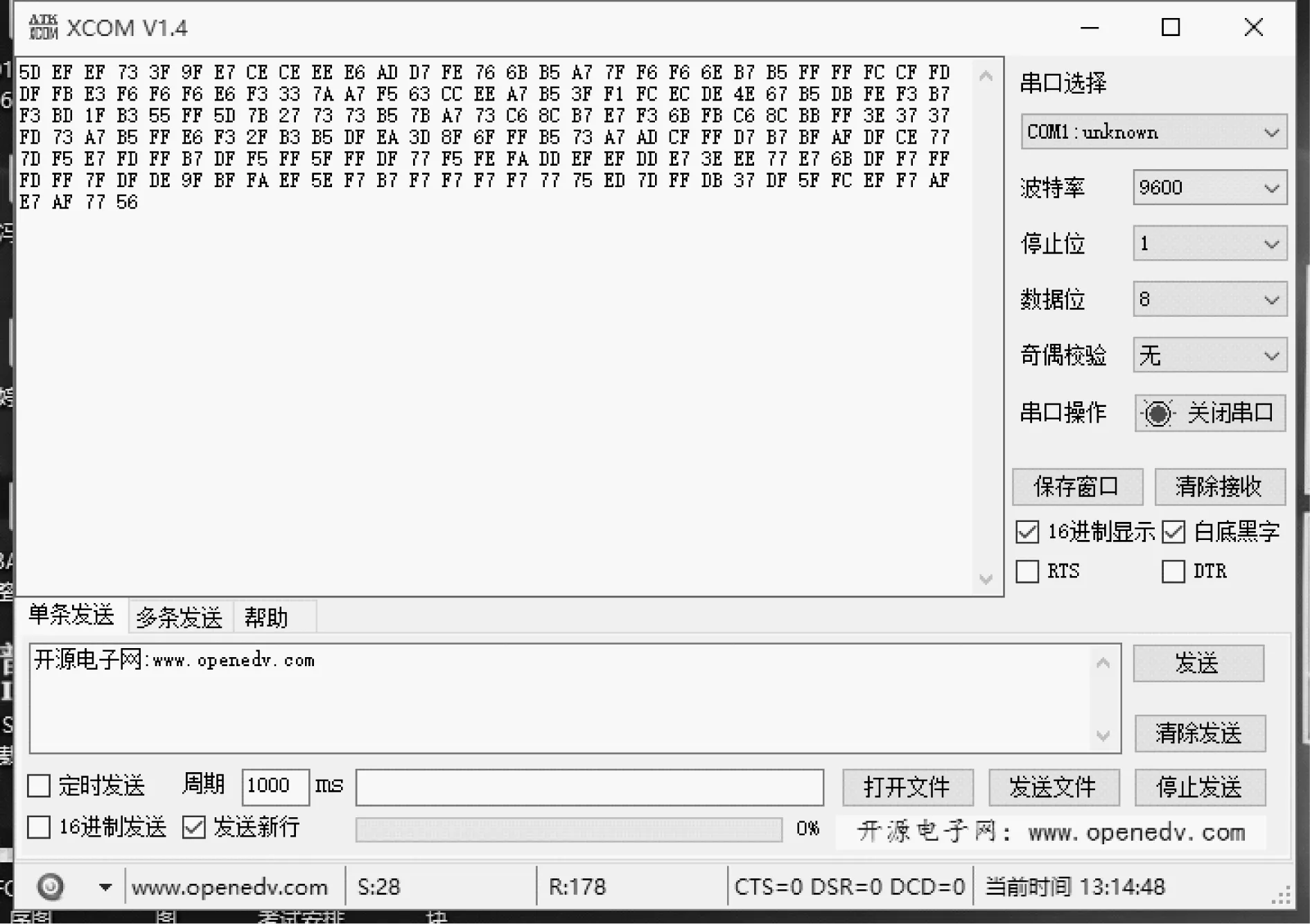

图12为线阵CCD的输出OS信号和AD9822的采集时序ADCCLK测试结果,从示波器的显示可得,满足输出信号的频率和采集时序一致。将RS232串口传输模块与FPGA器件连接,再通过USB与PC机相连,并利用串口调试助手进行调试,测试过程如图13所示。

图12 CCD的输出信号和采样时钟信号ADCCLK测试结果

图13 串口测试结果

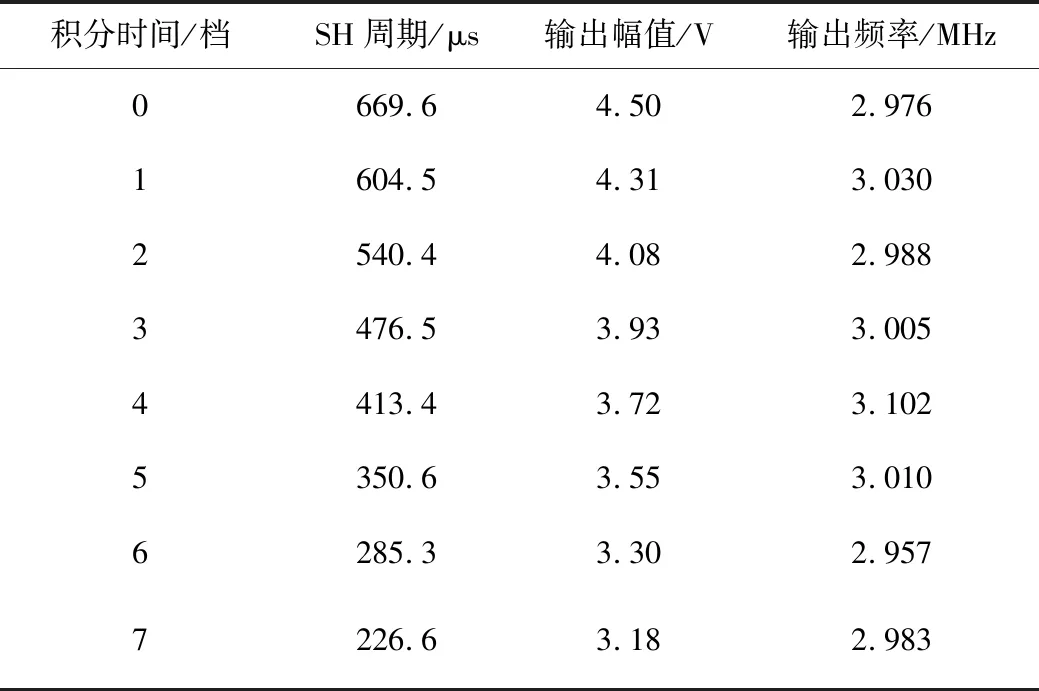

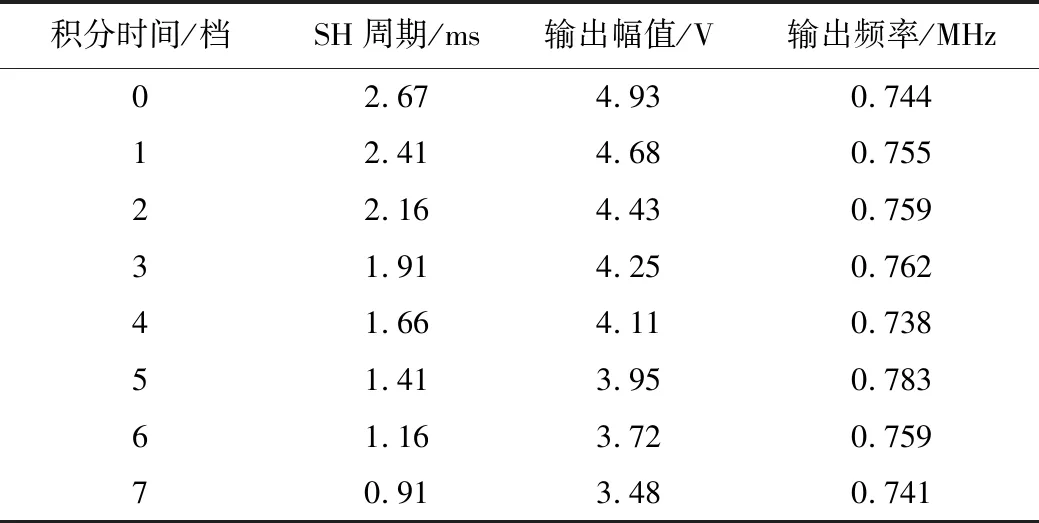

在相同的驱动频率下,改变积分时间;在相同的积分时间下,改变驱动频率,通过采集的数据,绘制成测试数据表格,如表1、表2所示。

表1 驱动频率24 MHz测试数据

表2 驱动频率6 MHz测试数据

由表1、表2实验数据可得,当驱动频率相同的情况下,通过调整积分时间的档位改变积分时间,积分时间的档位越高时,SH周期越短,即积分时间越短时,对应输出信号的幅值就越小;当积分时间相同的情况下,改变驱动频率,当驱动频率越大的情况下,对应积分时间越短,其输出信号的幅值相应的也越小。输出信号的频率变化与输入频率保持一致,当输入频率为24 MHz时,对应OS输出频率平均为3 MHz,当输入频率为6 MHz时,对应OS输出频率平均为0.75 MHz,其输入频率越高,对应的输出频率也越高,且呈线性变化的关系。

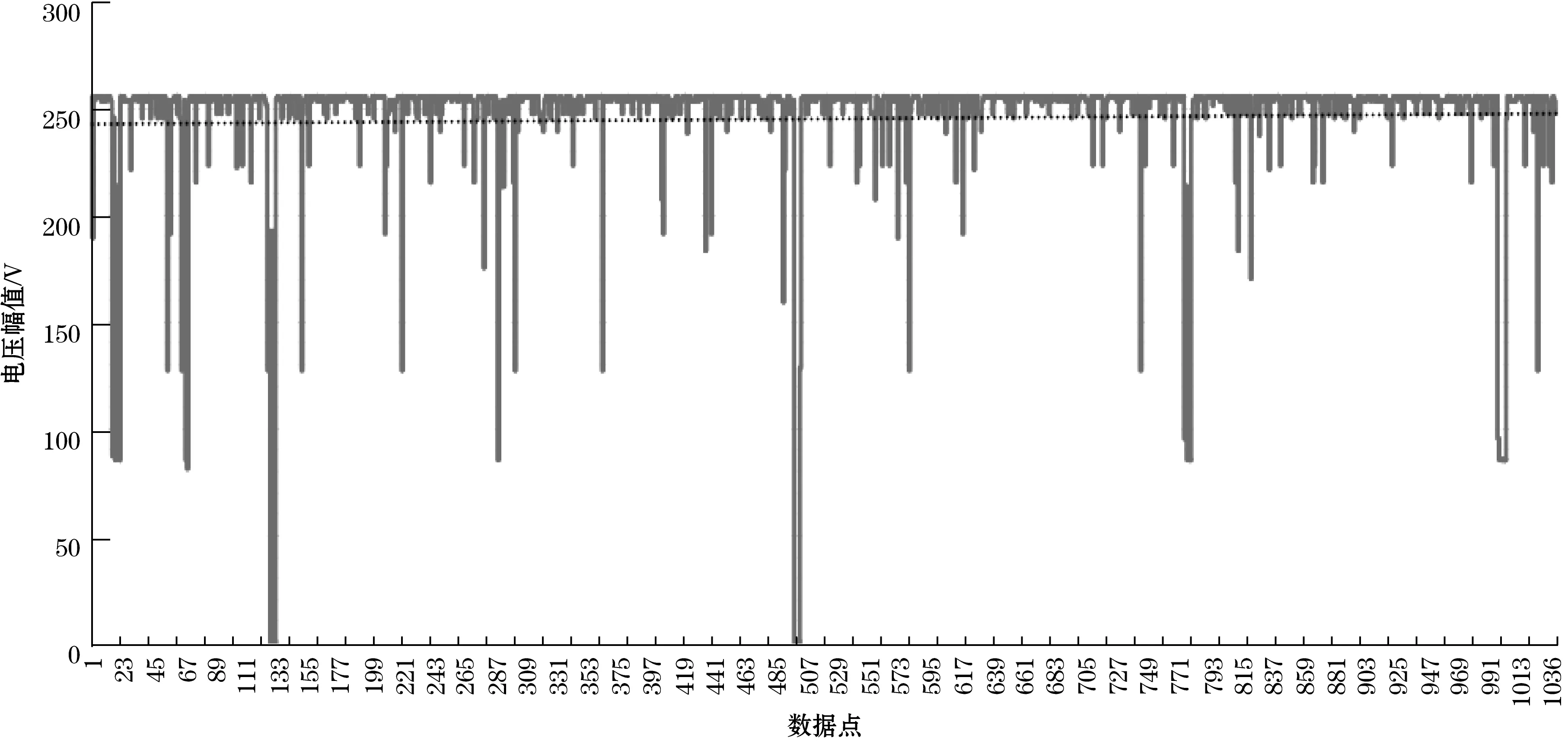

通过串口将数据传回PC机的实验结果图如图14、图15、图16,横坐标为采集的数据点,纵坐标为输出电压幅度。图14是在12 MHz的光照条件下,由串口获取的CCD数据。根据采集输出数据位8位,即0~255,根据比值换算可得趋势线大致幅值为4.70 V。图15是在12 MHz的光照条件下通过串口将数据传回PC机的实验结果图,输出幅度平均为4.90 V。

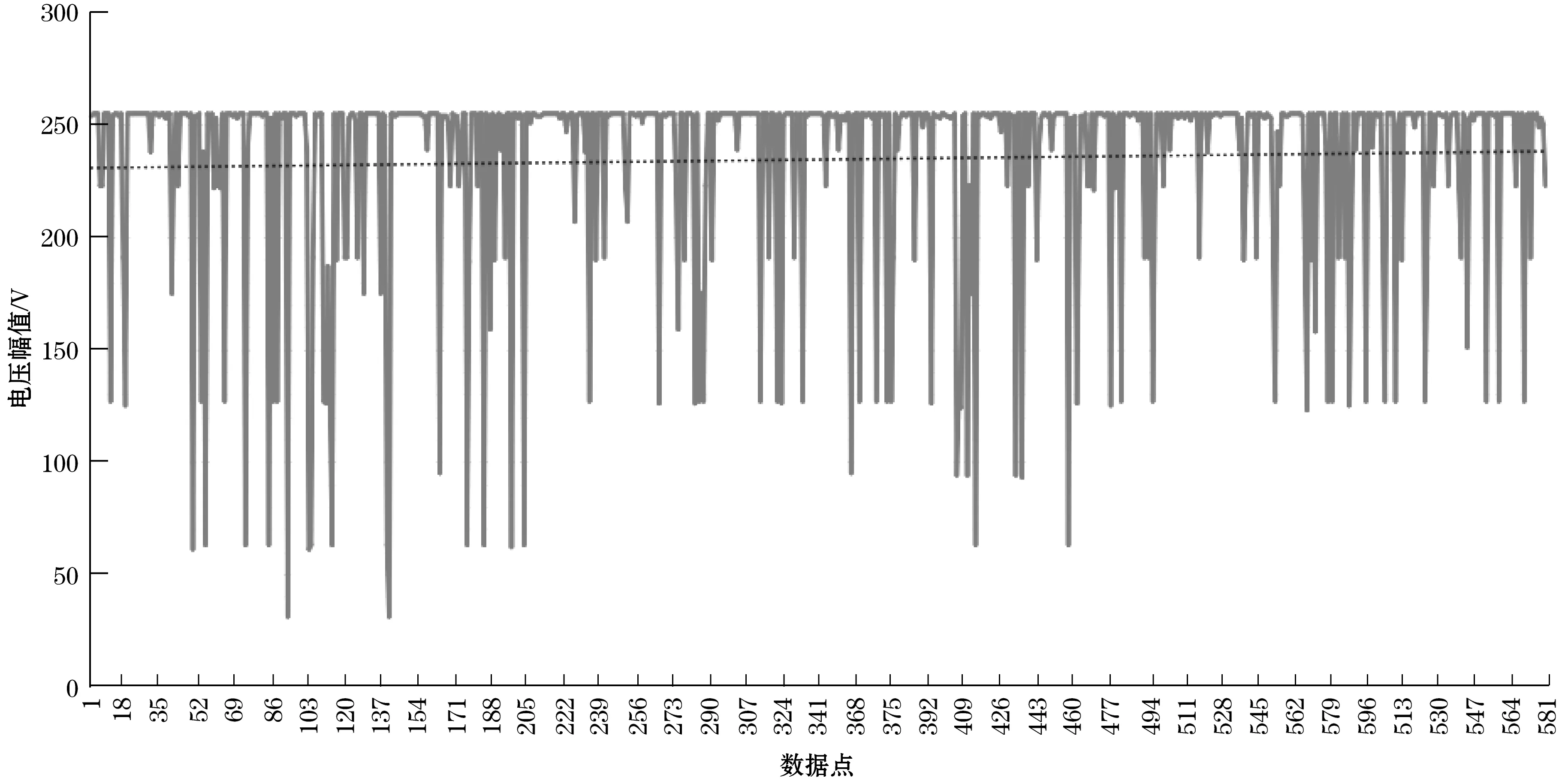

图16是在24 MHz的光照条件下通过串口将数据传回PC机的实验结果图,输出幅度平均为4.50 V。

5 结束语

通过CCD测试系统数据分析,在相同的驱动频率条件下,光照越强,输出幅值越大。在相同自然光照射条件下,驱动频率越大,输出幅值越小。通过构建在特性测量系统,通过对不同条件下数据的分析,可以实现对CCD器件参数的测量。

图14 12 MHz自然光条件下测试分析图

图15 12 MHz光照条件下测试分析图

图16 24 MHz光照条件下测试分析图