IC验证三种不同方法的分析比较

王立平 ,姚程宽 ,陈向阳 ,光 峰, 卢灿举,王 伟, 赵 彦

(1.安庆医药高等专科学校,安徽 安庆 246003;2.国防科技大学 电子对抗学院 ,安徽 合肥 230037 ; 3.中国电子科技集团公司第三十八研究所,安徽 合肥 230088;4.福州瑞星微电子有限公司,福建 福州 350003)

任何一款芯片在正式投片之前都需要进行完备和详实的IC验证工作,其目的就是搜寻已知和未知的验证空间,从中找出bug,从而提高芯片的质量,延长芯片的市场生命周期.IC验证本质上是一项科学且严谨的工作,和IC设计具有同等重要地位,在现有的芯片市场中,成功的SOC都是设计和验证密切配合、相互融通和共同努力的产物.IC验证是前端设计工作的最后一道防线,同时也是保证芯片最终成功的重要环节.目前常用的IC验证方法主要有三种:RTL模拟器、FPGA原型和现代硬件仿真,他们的工作原理、优缺点和应用背景方面都有较大差异[1-3].

1 RTL模拟器(RTL Simulator)

1.1 RTL简介

数字电路发展的初期,电路设计的规模只有几百到几千门,芯片的设计可直接通过试验型电路板进行原型验证.试验型电路板通常利用TTL逻辑部件(SSI/MSI 芯片),在目标系统中对芯片进行验证和调试,因为目标系统中测试环境是基于真实运行状态的,这种测试可以保证功能的完整性,提高流片的成功率.

随着芯片中电路规模的增长,当电路设计规模超过1万门时,试验型电路板难以完成验证任务,取而代之的是基于事件驱动算法的逻辑模拟器,随之产生了一个新的行业:EDA(电子设计自动化).作为最重要的一种事件驱动模拟器,RTL(Register Transfer Level,寄存器传输级)支持精确的功能和时序验证,在寄存器传输级得到了广泛的使用[4-6].

1.2 RTL的优缺点

RTL模拟本质是程序仿真,又称为功能仿真或软件仿真,是不加入电路延时的逻辑仿真.RTL仿真能够检查代码bug以及行为的准确性,能够在不依赖特殊底层元器件的情况下,将代码的可读性和可维护性极大提升,并同时提高仿真效率.由于RTL属于综合前的逻辑仿真,重用性很强.采用了硬件验证语言及其测试功能库(Vera,e,C,C++语言等)的RTL仿真,能够批量生成无法手动创建的测试,从而提高测试验证的效率.

RTL软件模拟器虽然具有先进的调试功能,且经济高效,但是当设计规模达到或超过 1 亿门时,缓存不能及时和内存交换数据,导致运行速度急速下降.可以通过 PC 服务器版本的并行化软件模拟器来缓解这一问题,但不能从根本上解决这一问题,且这一方案无法测试基于串行通讯技术的的嵌入式终端软件.比如设计规模为1 亿门电路,运行频率为200 MHz,实时执行速度 1秒/门,则需要执行的循环次数为2亿次.对于目前最好的CPU(具有足够的RAM和缓存),假设每秒100次循环,需要三个多星期才能完成这个任务.RTL实际运行时效率低下,只能验证小规模电路,如果在亿门级的电路验证中使用RTL,不可能实现功能的100%覆盖验证,必然导致设计工作的返工,且付出极高的成本代价[5-7].

2 FPGA 原型(FPGA Prototype)

2.1 FPGA简介

随着电路设计规模的不断扩大,科研人员将验证方案转向硬件测试,准确地说是采用动态测试原理的硬件测试平台.这一方案非常适合对嵌入式软件的测试,比如实时操作系统和自定义应用程序等.

随着可编程器件出现,产生了FPGA 原型(Field-Programmable Gate Array),即现场可编程门阵列.简单地说,FPGA原型就是规范化的测试电路版,是可编程器件发展的高级阶段,是一种半定制的电路板,其中SSI和MSI元器件被FPGA取而代之[8-9].

2.2 FPGA原型的优缺点

FPGA原型本质上属于一种半定制专用集成电路(ASIC),既克服了定制集成电路的缺点,同时也解决了原有可编程器件门电路数量有限的问题,极大缩小了设计目标与传统逻辑验证结果之间的差距.FPGA原型验证板的运行速度仅次于芯片,这是FPGA能够广泛推广和应用的一个重要原因[10-11].

FPGA原型的缺点是映射到原型验证板的调试时间过长.随着设计规模的不断扩大,FPGA 原型的开发工作量会按照指数增长.当FPGA 数量在 10 个以上的情况下,FPGA 原型就不能使用了.对FPGA调试非常困难,这将导致验证工程师转向处理复杂的原型问题.

FPGA原型的另一个缺点是设计过程的可视性很差.或者说,设计过程对于开发者过于透明,无法跟踪硬件错误.今天的IC设计过程不但追求视线范围可达,而且还包括非视线范围可达.

3 现代硬件仿真 (Modern Emulator)

3.1 硬件仿真简介

因为RTL和FPGA都不能提供运行间的实时问题解决方案,而硬件仿真在这一问题上则提供了可行的方案.早期的硬件仿真由于高昂的成本使得其难以推广,随着IC成本的不断降低和性能的极大提升,现代硬件仿真得到了广泛的认可和应用.

硬件仿真遵循的最重要的原则就是“验证解决方案”,作为清除bug最有效的工具,硬件仿真解决方案目前有较高的占有率和增长率.在芯片流片前的SoC调试过程中,对硬件测试和软件集成都有极高的价值.采用硬件仿真,设计人员将不再考虑设计复杂性和拓扑结构.

3.2 硬件仿真的优缺点

1)与RTL 软件模拟器相比,硬件仿真的运行速度可提升5-6个数量级,这个运行速度保证了硬件仿真可以有效运行嵌入式软件.1千万门电路的平均频率约为2 MHz,而1亿门电路的最高频率可以达到1 MHz.可见,当设计规模增加时,相比于RTL模拟器,硬件仿真的性能下降得明显很慢.

2)与FPGA原型相比,硬件仿真能有效运行嵌入式软件.硬件仿真从顶层的嵌入式软件出发,逐渐向下层抽象,追踪各个硬件运行时的状态.嵌入式软件将运行数据库划分为几十亿个时钟周期,其中软件调试只在其中的几百万个时钟周期内,大大缩小了对软件中每个bug追根溯源的工作量.

3)如果软硬件开发工程师都采用硬件仿真,即合成了软件和硬件的设计视图,依托相同的设计表示,那么他们在一起调试软件和硬件的同时,可以有效解决嵌入式软件与硬件之间的边界衔接问题.简单地说,就是能够确定出了问题的地方究竟是软件还是硬件.

4)硬件仿真不仅能够对内在的系统进行物理测试,而且还可以通过多种语言的软件平台对目标系统加速测试,其中包括SystemVerilog,C/C++,Verilog以及VHDL等[12-14].

4 性能综合分析

现代硬件仿真的优势是显而易见的.现代硬件仿真速度更快、使用更容易,并且初期的成本较低.在处理几十亿ASIC门级规模情况下,编译时间明显减少,可为多个并发用户提供强大的调试环境.

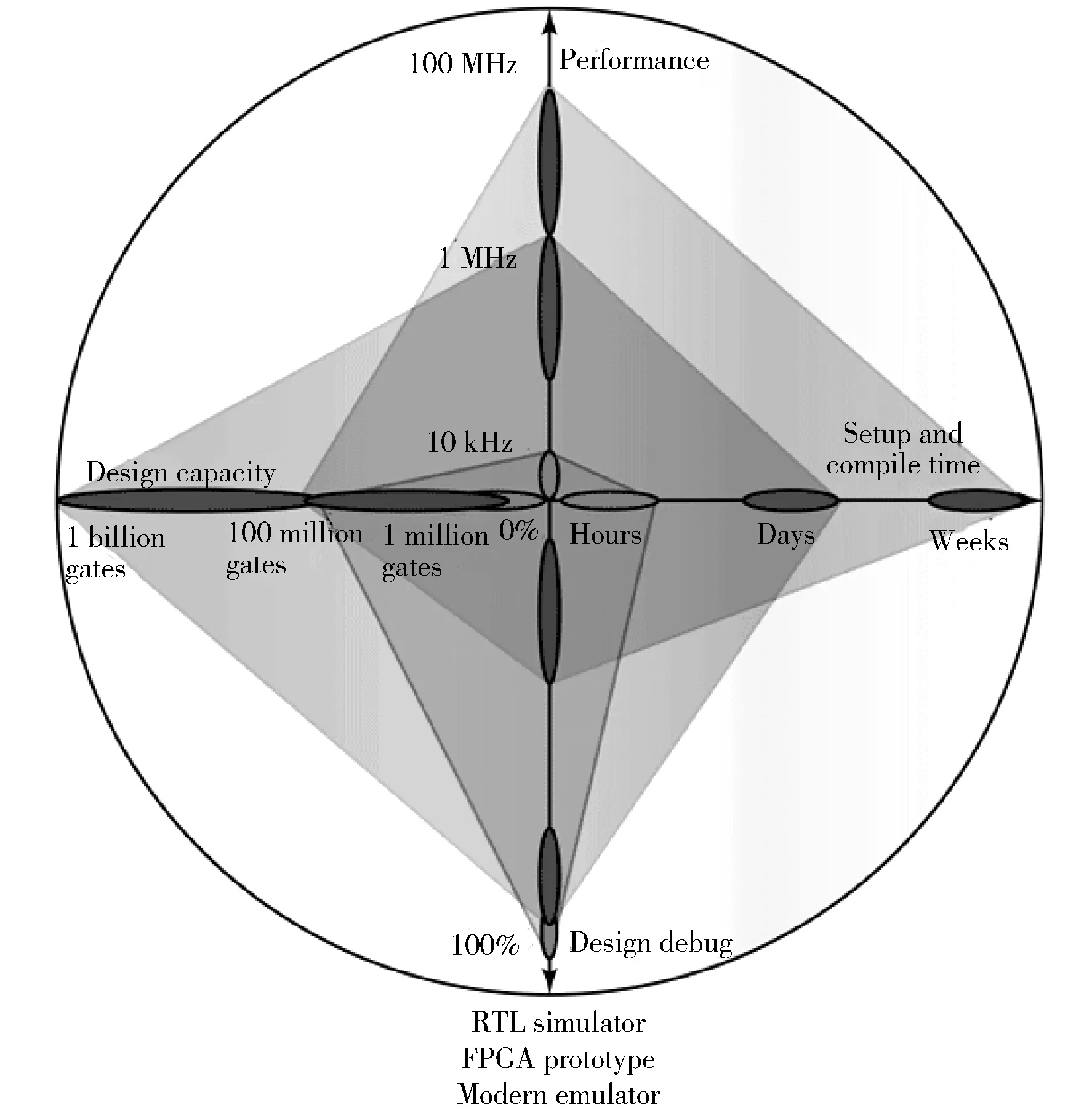

图1 性能比较分析

从性能(Performance)、设计容量(Design capacity)、设置和编译时间(Setup and compile time)和设计调试(Design debug)四个方面综合考虑, RTL和FPGA这两种方案并不是完全被否定,他们也都有自己独特的优点.比如说,RTL可以获得最短的编译时间,FPGA可以得到最高的性能.这四个方面的性能比较如图1所示[15].

5 总结与展望

本文介绍了IC验证的三种方法,并对他们的性能进行了分析比较.在现代的IC行业中,对芯片上市的时间要求越来越高,同时不断升级的软硬件集成问题和质量问题等,给设计师带来了很大的压力.由于芯片流片的高昂成本,使得IC验证和IC设计具有同等的重要性,无论是对企业的成本控制,还是对于特定产品的质量控制,针对不同的需求分析,采用合适的验证方法是极具战略意义的重要选择.