基于FPGA的DDFS信号发生器设计

杨 敏,王 利,张金时,裴水源,罗 浩

(中北大学机电工程学院,山西 太原 030051)

0 引言

由于直接频率合成(direct digital frequency synthesizer,DDFS)技术具有频率转换速度快、相对带宽宽、频率分辨率高以及波形稳定等优点,已经广泛用于雷达、通信、导航、遥控遥测、电子对抗以及现代化的仪器仪表工业、生物医学检测等领域[1-2]。随着现场可编程门阵列(field programmable gate array,FPGA)技术的发展,其资源容量、工作频率以及集成度都得到了极大的提高。由于FPGA灵活的接口和控制方式,使得其广泛应用于实现某些专用数字集成电路[3]。本文基于DDFS基本原理,采用Inter公司的FPGA芯片Cyclone IV E系列器件,完成DDFS信号发生器设计。该信号发生器可产生不同频率、相位的正弦波、矩形波、三角波信号。

1 DDFS基本工作原理

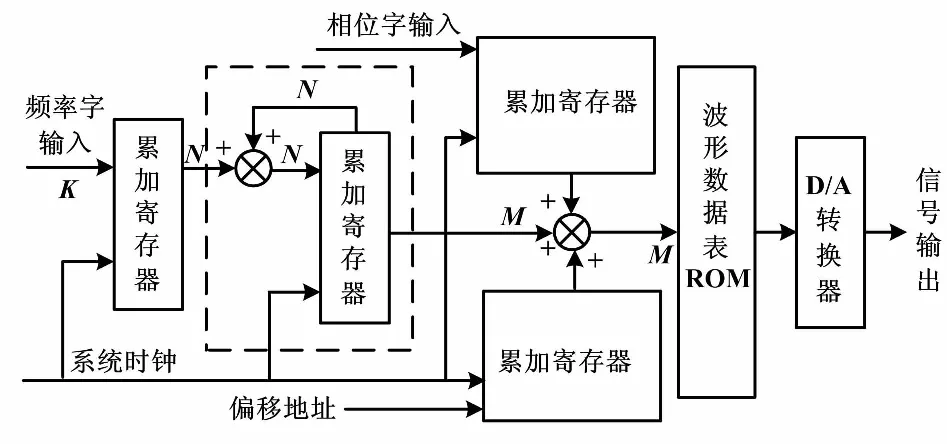

基于FPGA的DDFS原理框如图1所示。

图1 基于FPGA的DDFS原理框图

DDFS主要由相位累加器、波形存储器、D/A转换器、低通滤波器组成[4]。相位累加器由N位加法器和N位寄存器构成。在系统时钟作用下,相位累加器中的加法器将频率控制字与累加寄存器输出的相位数据进行累加,并将得到的相位数据输入累加器的输入端,以便在每一个时钟到来时与频率控制字线性累加。相位累加器根据得到的相位码对波形存储器进行寻址,经查找表找出波形存储器里的波形采样值。输出的数字信号经过D/A转换器转换为模拟信号。DAC输出信号实际上是阶梯模拟信号,需在D/A转换后利用低通滤波器对波形进行平滑处理,滤除高频分量,得到连续变化的波形[5-6]。

DDFS输出信号的频率为[7]:

(1)

式中:fo为输出信号频率;K为频率控制字;N为相位累加器的字长;fc为系统时钟频率。

2 系统总体方案设计

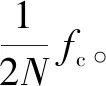

信号发生器系统框图如图2所示。

图2 信号发生器系统框图

首先,通过按键控制频率字、相位字以及波形地址的选择,并将其显示在LCD上。其目的是与在示波器上的观察到的波形、频率、相位进行比较。然后,通过12位的DAC将数字信号转换为模拟信号,并经低通滤波滤除高频分量,得到光滑的、连续的信号波形。最后,将其输入到示波器进行观察。

本系统主要包括硬件设计和软件设计两部分。软件设计主要基于FPGA平台的程序部分,包括相位累加器、波形存储器、按键设计和LCD设计,使用Verilog HDL汇编语言进行编程设计。硬件设计主要有D/A转换和低通滤波器设计。

本文所用的系统时钟为50 MHz,相位累加器为32位。由于采用12位的DAC,所以存储波形的ROM具有12 bit的输出。将FPGA 输出的数字信号转换为模拟信号,输出信号频率范围为1 Hz~100 kHz,幅值范围为0~5 V,波形可设为正弦波、三角波、方波。

3 系统重要模块设计

3.1 程序固化

当DDFS应用于某些领域如引信领域时,要求脱离上位机。这就要求存储于SDRAM中的程序可以掉电不丢失。但是SDRAM不具有记忆功能,所以先将程序存入所用开发板的EPCS flash存储器中。该存储器原本存放FPGA的配置文件,其内存为16 Mbit,足够存放编写的程序,且其掉电后不会丢失程序。FPGA上电后,再从EPCS flash中读取程序并保存到SDRAM中,从而保证掉电不丢失程序。

3.2 相位累加器

相位累加器由32位的加法器和32位的寄存器组成。在系统时钟的作用下,对频率控制字K进行线性累加。当累加32次后就会产生一次溢出,每溢出一次即为DDFS的一个周期[8]。相位累加器的实质是一个计数器,它累计的是每个时钟脉冲下的频率控制字K[9]。

3.3 波形存储器

波形存储器,又叫ROM查找表。由式(1)可知,当增大相位累加器的位数N时,就可以提高DDFS最小分辨率[10]。同时,为了解决ROM空间资源占用过大的问题,可以采用相位截断的方法取相位累加器输出的高M位作为波形存储器的地址位[11]。本文采用这种方法,将相位累加器输出的高12位作为波形ROM的取样地址。

在本文中,使用Matlab编写波形信号,然后将其写入生成的.mif文件中。通过按键循环切换正弦波、方波、三角波,ROM查找表的地址线为14位、数据线为12位;存有正弦波、方波和三角波的数字波形信号,每种波形有4 096个字节,波形在ROM中存储的基地址为0000H。其中:RAM地址的0000H~0FFFH为正弦波的数据;1000H~1FFFH为三角波的数据;2000H~2FFFH为方波的数据。各个波形的数据存储地址偏移量为1000H。通过功能按键,获取需要输出的波形类型。如果输入为0,则偏移地址0000H,选择正弦波。同理,如输入为1和2的偏移地址分别为1000H和2000H,则分别选择三角波和方波。波形选择的Verilog HDL语言如下。

case(F_Change)

0:Offset_add=12′h0000

1:Offset_add=12′h1000

2:Offset_add=12′h2000

default:Offset_add=0

endcase

3.4 按键设计

信号发生器使用4×4键盘。键盘主要按键功能如下。

①“0~9”:数字键,设定频率字和相位字。

②“确定”:用于确认设置的波形信号,只有按下此键,波形信号才有效。

③“删除”:删除最近一位输入的信号数字。

④“F”:控制输出波形的切换。

⑤“←”:步进增大控制。

⑥“→”:步进减小控制。

⑦“+” :控制输入频率字和相位字递增。

3.5 LCD显示设计

人机交互界面使用的是LCD1602A液晶显示器。

FPGA控制LCD显示数据主要过程为:初始化显示屏→配置显示屏→写显示数据或指令。初始化过程为:延时15 ms→写指令38H→延时5 ms。其中,指令38H为不检测忙信号。配置显示屏过程为:写指令38H→写指令08H→写指令01H→写指令06H→写指令0CH。

指令38H:显示模式设置。

指令08H:显示关闭。

指令01H:显示清屏。

指令06H:显示光标移动设置。

指令0CH:显示开及光标设置。

写显示数据或指令:通过按键读取并判断本次输入为指令还是数据。如果是指令,则控制LCD的RS引脚为低,反之为高。

4 输出信号测试分析

4.1 DDFS信号发生器的仿真验证

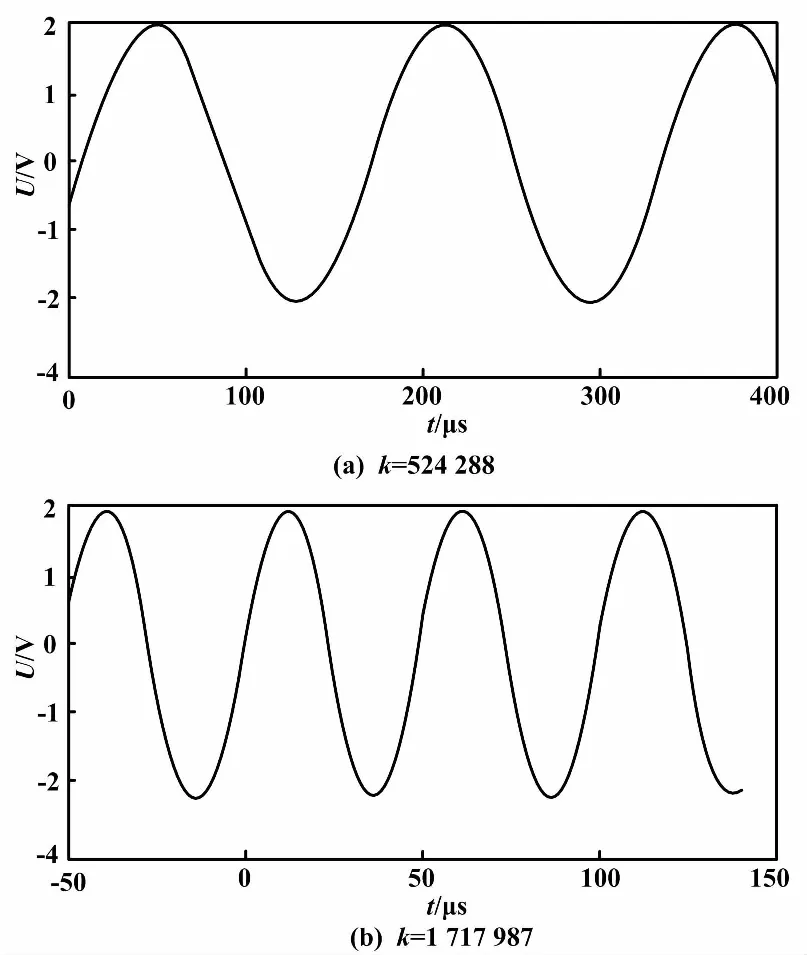

在Quartus II 13.0平台下,将程序编译成功后,调用Modelsim进行仿真,输入的频率控制字分别为542 488和1 717 987,波形类型为0,选择为正弦波。

由式(1)可以计算得:当频率控制字K=542 488时,fo=6.06 kHz;当频率控制字K=1 717 987时,fo=20 kHz。

通过仿真测得的频率分别为6.06 kHz和20 kHz,与由公式计算得到的结果相吻合。由此可知:①信号源输出信号波形光滑,频率稳定度高,且仿真测试所得频率与理论计算值的误差较小;②正弦波在两个不同频率间波形切换自然,频率转换速度较快,满足设计要求。

4.2 信号发生器的试验验证

信号发生器仿真验证后,将项目编译生成的编程文件下载到CYCLONE器件中,对其进行试验验证。示波器输出波形如图3所示。

图3 示波器输出波形图

由图3可知,按键输入的频率控制字依然为524 288和1 717 987,波形类型为0,选择正弦波,便于对比仿真结果。示波器输出的波形形状光滑、连续、无明显失真,且输出波形的频率与理论计算值及仿真测试值较为接近,输出波形质量好,误差小,准确率高。

5 结束语

随着电子通信技术的迅速发展,对信号发生器的要求(如信号频率范围、带宽和频率分辨率)也越来越高。除此之外,对信号波型的选择及调制特性要求也在提高[12]。本文基于FPGA设计的DDFS信号发生器,可以输出正弦波、方波、三角波,并可灵活改变波形、

频率、相位,具有转换时间短、精度高、相位变化连续等优点。只要改变频率控制字K的值,就可以改变输出频率的大小。该系统可脱离计算机独立工作,具有相当大的灵活性;加入按键与LCD显示,使得信号发生器工作更加简单方便。该信号发生器幅值范围为0~5 V,频率范围为1 Hz~100 kHz。由于硬件资源有限,频率范围较小,但是只要更换输出频率较高的DAC(即高速DAC),即可输出频率更大的波形。