基于FPGA的高速冗余I/O总线设计与实现

刘 鎏,臧 峰,牛洪海

(南京南瑞继保电气有限公司,江苏 南京 211102)

0 引言

控制系统,如分布式控制系统(distributed control system,DCS)、可编程逻辑控制器(programmable logic controller,PLC)等,是计算机技术不断发展与自动化控制技术相结合的产物,在电力、石化、冶金、化工等大型工业中有着广泛的应用[1]。与蓬勃发展的现场总线(如Profibus、FF、CAN、LonWorks等[2-3])相比,控制系统本地总线的发展显得相对缓慢。究其原因,主要是控制系统与本地输入/输出(input/output,I/O)模块通信相对比较封闭,涉及到控制系统架构和所有I/O模块,因此各个厂家都对协议保密,令其他厂家无法获取其通信信息。文献[4]提出了一种基于面向通用对象的变电站事件(general object oriented substatI/on event,GOOSE)的控制器与I/O之间的通信协议,但由于其使用网络通信,限制了其使用范围。文献[5]提出了一种基于PCI Express的通信线,但由于计算机串行总线(如PCI Express、USB、IEEE 1394)兼容性、可靠性和可扩展性等方面的原因,无法很好地满足控制系统应用的需求[6-9]。

针对上述总线所存在的问题,本文提出了一种基于现场可编程门阵列(field programmable gate array,FPGA)的高速、可靠的冗余I/O通信总线。物理层采用多点低压差分信号[10](multi-point-low-voltage differential signaling,M-LVDS)标准,实现了数据链路层实时数据的传输和通道链路状态的监视,保证了数据传输的可靠性和实时性。I/O模块采用直接内存存取(direct memory access,DMA)的方式进行通用异步收发器(universal asynchronous receiver transmitter,UART)的通信报文解析,详细设计参考文献[10]。

1 系统总体方案

系统结构如图1所示。

图1 系统结构图

目前,主流控制系统的体系架构一般可分为4个层次:企业管理层、工厂(车间)层、控制装置单元层和现场仪表层[11]。其中,控制单元层包括控制器和I/O模块。控制器与I/O模块的互联互通是整个系统数据传输的枢纽,在实时性、可靠性和可扩展性等方面有着非常高的要求,总线的通信效率直接影响了整个控制系统的性能[1]。本文设计的控制器采用主备冗余的方案,I/O单元采用A/B冗余I/O总线方案。主备控制器通A/B冗余总线与I/O模块进行通信,但仅主控制器通过A/B冗余总线交替对I/O模块发送查询数据和控制报文,备控制器通过A/B冗余总线监听I/O模块的响应数据以判断链路的通断。当备控制器升级为主控制器后,原主控制器不再发送查询数据和控制报文,而新晋控制器主要发送查询数据和控制报文。

其中,I/O模块可以是模拟量输入(analog input,AI)、模拟量输出(analog output,AO)、开关量输入(digital input, DI)、开关量输出(digital output,DO)或其他一些特殊的I/O模块。一对控制器下可以带6条冗余I/O总线,每条I/O冗余总线可以挂载10个I/O模块。因此,本文设计的控制器一共可以挂载60个本地I/O模块。

2 协议设计与实现

控制器与I/O模块之间通信的实时性和可靠性,主要取决于物理层通信速率和数据链路层调度策略。本文设计的通信协议规定了控制器与I/O模块之间的信息交换模式。此协议遵守开发系统互连参考模型(open system interconnect / on reference model,OSI/RM),使用了应用层、数据链路层和物理层。应用层实现了I/O模块实时数据或非实时数据的解析,数据链路层实现了数据的循环冗余校验(cyclic redundant check,CRC),物理层实现了串口数据的编解码功能。

本文设计的每个I/O模块均具有相同的通信接口和帧结构。I/O模块包括一个微控制器(micro control unit,MCU),通过DMA实现了数据的采集和分析,详细设计参考文献[11]。控制器使用了Xilinx公司的Zynq芯片。此芯片具有2个ARM芯片和1个FPGA。ARM芯片运行QNX实时操作系统,并通过FPGA扩展6路冗余I/O总线。每路总线实现了5 Mbit/s的高速串口通信,主要包括M-LVDS发送/接收模块、10 bit编解码模块、CRC校验模块。QNX实时操作系统通过配置寄存器和DMA实现与FPGA的数据交互。

2.1 物理层协议

物理层规定了控制器与I/O模块之间通信的机械、电气、功能和过程方面的特性。此通信协议采用M-LVDS标准,实现了一主多从的通信模式。M-LVDS具有高速传输、低电压摆幅、抗干扰、低功耗、多点通信和故障安全隔离等特点[1]。由于M-LVDS具有上述特点,I/O模块可以实现在线热插拔以实时建立或断开与控制器的通信,而不会干扰I/O总线上其他I/O模块的通信功能。总线的热插拔功能提高了整个系统的可靠性和可扩展性。

2.2 数据链路层协议

数据链路层负责在链路上进行控制器与I/O模块之间链路层协议数据单元(protocol data unit,PDU)的交互。数据链路层详细定义了协议数据单元,如表1所示。其中:启动字符0x7e7e的帧格式按照帧头帧尾判断,帧长度是从启动字符1到结束字符的长度。

表1 协议数据单元

2.3 应用层协议

应用层协议主要包括3个部分:①控制器根据I/O模块的配置文件,对下发给I/O模块的查询或控制报文进行组包;②解析I/O模块上送的实时数据,并把数据填入I/O接收缓冲区;③对非实时报文进行组包或解析。

由于QNX实时操作系统通过DMA把下发给I/O模块的报文传输给FPGA,因此需要对下发的报文格式进行设计,以保证FPGA接收数据的正确性。定义ARM传输给FPGA的数据格式如表2所示。

表2 ARM传输给FPGA的数据格式

Tab.2 Data format of ARM to FPGA

info字段使用6 bit作为掩码,每个bit位代表6条总线的各个分支,如0x1表示在第一条总线上发送,0x10代表在第五条总线上发送,0x3f代表六个分支都发送。len_byte代表这帧数据报文的总长度,content即数据链路层协议数据单元PDU,但没有CRC校验和帧尾标志。这2项内容FPGA会自动加入,以减轻ARM芯片的负载。

由于采用DMA发送数据会产生DMA中断,因此在FPGA接收到数据后,并不是通过DMA的方式把数据传输给QNX实时操作系统,而是通过循环缓冲区的方式把数据存储在全局数据区。此设计有两方面的优势:①减少DMA中断产生的次数,QNX实时操作系统不需要在FPGA接收到每个I/O模块数据后都产生一次中断去处理数据;②6条总线下的I/O模块可以统一处理,I/O模块的数据可以形成一个断面,有利于算法页处理。

3 软件设计

软件程序主要包括:①I/O模块配置文件解析;②串口寄存器配置;③串口驱动配置;④FPGA寄存器配置;⑤实时报文传输;⑥非实时报文传输。控制器开机后,首先进行参数配置设置。设置完后,FPGA定周期产生5 ms脉冲信号,QNX实时操作系统捕获此脉冲信号后,进行实时报文和非实时报文的组包和解析。

3.1 实时报文传输

实时传输流程如图2所示。

图2 实时传输流程图

当QNX实时操作系统捕获FPGA产生的定时中断后,首先,FPGA通过循环缓冲区传输给应用层的报文解析,根据解析结果把I/O模块的实时采集数填入I/O模块的内存区;然后控制器根据I/O模块配置信息,对下发给I/O模块的控制或查询报文进行组包;最后,当扫描完60个I/O模块后,把形成的下发报文通过DMA传输给FPGA。FPGA接收到报文后,通过表2格式进行解析,并在链路协议数据单元PDU的末尾填入CRC校验和帧尾标志。

3.2 非实时报文传输

由于FPGA定周期产生5 ms的脉冲信号进行实时报文的接收和下发,因此需要考虑在实时报文中加入非实时报文,以适应一些非周期性数据的请求。本文的设计方案是:如果分支有非实时数据,那么在此分支实时报文传输周期的最末加了一帧非实时报文;如果没有,则忽略此分支的非实时时隙。利用这种方案,可以有效解决实时报文传输和非实时报文传输的冲突。

3.3 性能分析

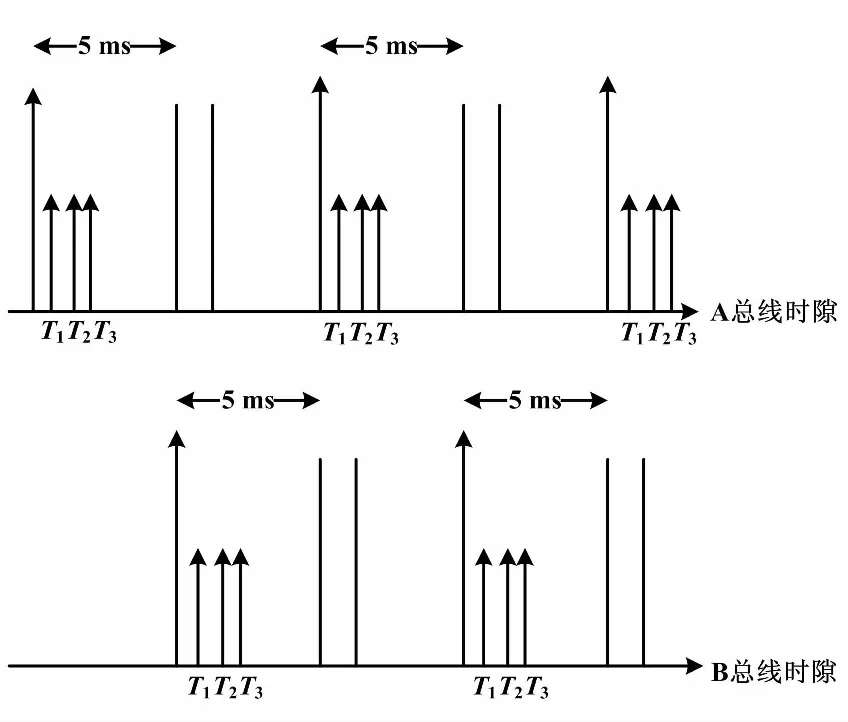

通过如图3所示的总线时隙图,可以更好地理解控制器与I/O模块如何通过A/B冗余总线进行通信。

图3 总线时隙图

图3中:T1为QNX实时操作系统解析I/O模块上送数据的时间,T2为QNX实时操作系统根据I/O模块配置文件进行下发查询或控制报文的组包时间,T3为通过DMA把数据从ARM芯片传输给FPGA的时间。经过实测,T1、T2、T3的处理时间量级都在ms级。

当达到T3后,FPGA根据表2格式进行下发数据报文解析,并自动加入CRC校验和帧尾标志下发查询或控制报文。理论上,因为T1、T2、T3并不占用总线带宽时间,通信时间可以达到5 ms。如果此周期是A总线下发报文,那么下个周期切换到B总线下发报文。

这样切换发送既可以减轻I/O模块的通信负载,也可以监视A/B总线的通信链路状态。但是这样操作的缺陷就是处理I/O模块反馈的数据,需等待2个查询周期,即10 ms的时间。如果A总线或B总线通信链路断开,那么会导致整个分支查询周期扩大一倍。但是控制器和I/O模块在一个屏柜组屏,而且通信链路断开控制器会报警,因此可以很好地避免这种情况的发生。

4 结束语

本文设计并实现了一种基于FPGA的高速冗余I/O总线。系统很好地结合了嵌入式ARM芯片与FPGA的优点,实现了FPGA与ARM芯片相结合的嵌入式平台开发,提高了系统的实时性、可靠性和稳定性。该设计可以保证6路I/O模块总线实时并发处理,而且不占用ARM芯片的处理时间,因此具有很高的使用价值和推广意义。