基于FPGA的扩频OFDM信号半物理仿真技术研究

乔永明,邹德财,卢晓春

(1.中国科学院 国家授时中心,西安 710600;2.中国科学院 精密导航定位与定时技术重点实验室,西安 710600;3.中国科学院大学,北京 100049;4.中国科学院大学 天文与空间科学学院,北京 101048)

0 引言

目前,以美国GPS(Global Positioning System)为代表的全球导航卫星系统(Global Navigation Satellite Systems,GNSS)已经成为信息时代一个国家或地区重要的基础设施之一,在军用、民用各行业领域得到了广泛应用。GNSS服务领域的不断拓展也带动了GNSS技术的不断进步和持续发展。

信号体制是GNSS最重要的技术要素之一,也是联系GNSS三大组成部分(空间段、地面段和用户段)的桥梁和纽带,对GNSS导航、定位、测速、授时等服务功能的实现和服务性能的提升具有重要意义。

因此,无论在Galileo信号体制设计还是在GPS,GLONASS现代化过程中,信号体制一直都是被关注的重点和研究的热点。纵观Galileo信号体制设计和GPS,GLONASS信号体制现代化的过程[1-4],一些新的思想不断呈现。在信号波形设计方面,从最初的BPSK(binary phase shift key)调制到BOC(binary offset carrier)调制,再发展到后来的MBOC(multiplexed BOC)、Alt BOC(alternate BOC)、TD-AltBOC(time division AltBOC)等调制,在频谱资源有效利用、改善兼容性等方面发挥了重要作用;在扩频码生成方面,从早期的m序列、Gold序列到后来的Weil码,扩频码的自相关和互相关性能逐步提高;在信道编码方面,卷积编码、LDPC(low density parity check)码等前向纠错编码以及导频通道的引入都大幅地提高了信号的健壮性。

随着GPS和GLONASS现代化、北斗和Galileo系统建设工程化实施的不断推进和加快,尽早开展下一代新型GNSS信号体制的设计、论证和试验研究,有利于增强GNSS系统的服务性能和自身优势,提高国际竞争力。

近几年,正交频分复用(orthogonal frequency division multiplexing,OFDM)调制技术在数字电视、移动通信等领域得到了较为广泛的应用和发展。OFDM调制技术的核心思想是将信道分成若干正交子信道,将高速数据信号转换成并行的低速子数据流,调制到每个子信道上进行传输。正交信号可以通过在接收端采用相关技术来分开,这样可以减少子信道之间的相互干扰(ICI)。每个子信道上的信号带宽小于信道的相关带宽,因此每个子信道可以看成平坦性衰落信道[5]。

作者正是基于GNSS扩频思想,将OFDM调制技术用于新型GNSS导航信号体制,设计了一种具有抗多径性能的新型扩频OFDM调制的导航信号。文中给出了新型导航信号的生成机理以及关键模块的FPGA(field-programmable gate array)实现。同时,利用Xilinx公司的Virtex-7芯片进行了软件仿真,最后给出了仿真结果,证明设计的新型扩频OFDM调制的导航信号具备一定的工程实现性。

1 扩频OFDM信号生成机理

扩频OFDM信号主要实现扩频码与OFDM信号的结合,本节通过结合OFDM信号的优势与扩频码的优势,设计出了一种保留了OFDM信号子载波正交性与扩频码良好自相关性、互相关性的扩频OFDM信号。扩频OFDM信号的生成包括映射、OFDM调制、循环前缀、扩频码的生成和扩频OFDM调制模块。对输入的信息流进行映射、OFDM调制与添加循环前缀,生成OFDM信号;再将OFDM信号与已生成的扩频码进行扩频调制,生成扩频OFDM信号。

①映射

对于输入的导航电文信息,采用BPSK的调制方式。BPSK是一种矢量调制,它将输入的比特映射到一个复数平面上,形成复数调制符号。因此在BPSK映射平面上,有两个点,共表示两种矢量状态[6]。

BPSK调制可表示为

(1)

导航电文经过映射调制可以满足信息速率的要求,且具有抗噪声能力等优点。

②OFDM调制

对输入的映射调制符号进行串并转换,将并行的符号数据流再调制到不同的子载波上。一个OFDM符号包括N个子载波,其输出OFDM信号可以表示为:

(2)

式(2)中,T表示一个OFDM符号的持续时间,di(i=0,1,…,N-1)表示分配给每个子信道的数据符号矩形窗函数rect(t)=1,|t|≤T/2。令式中ts=0,忽略矩形函数,并对信号s(t)以T/N的速率进行采样,即令t=kT/N(k=0,1,…,N-1),可得

(3)

式(3)中,与离散傅里叶逆变换(inverse discrete Fourier transform,OFDM)运算的表达式一致,说明sk可通过di的IDFT得到[7]。那么接收端解调可通过离散傅里叶变换(DFT)恢复出发送的数据。

③循环前缀

循环前缀(CP)在OFDM系统有着很重要的作用,它可以有效地对抗多径时延扩展[8]。一般情况下,为了消除由于多径造成的子信道间干扰(ICI),可以在OFDM符号之间插入循环前缀信号,即将每个OFDM符号的后Tg时间内的样值复制到OFDM符号的最前面,其中Tg为循环前缀的长度。这样的话,如果时延扩展小于循环前缀的长度,符号间干扰(ISI)只会对接收信号循环前缀内的前Tg时间内的取样值形成干扰,只要将其去掉,就可以完全消除ISI的影响,那么多径就不会对下一个OFDM符号造成干扰。

④扩频码的生成

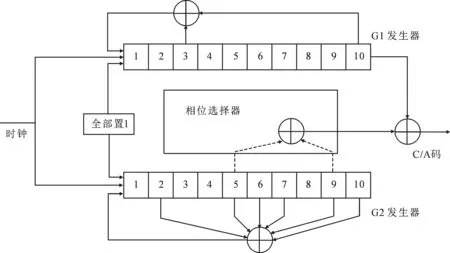

在GNSS导航系统中,扩频码为平衡Gold码,利用Gold码具有良好的自相关和互相关特性以提高检测能力并防止多址干扰。平衡Gold码是由两个m序列复合而成,每改变两个m序列相对应的位置可产生一个新的Gold序列[9]。使用的扩频码是基于Gold码而来的,设计使用一种周期为1 023(即210-1)码片的Gold码,是由两个10级最长线性反馈移位寄存器序列产生,Gold码发生器如图1所示。

图1 Gold码发生器

两个m序列的特征多项式分别为:

G1(x)=1+x3+x10,

(4)

G2(x)=1+x2+x5+x6+x7+x9+x10,

(5)

式(4)和(5)中,G1和G2为10级优选对,G1和G2的初始相位固定值为0X3FF,文中所用的扩频码与Gold码产生方式一样,在生成的Gold码基础上截取了前1 000个码片,扩频码的码速率为0.1 MHz,由于码长为1 000,故码周期为10 ms。

⑤扩频OFDM调制

目前,OFDM与扩频码的结合方式主要有3种方案:多载波码分多址(MC-CDMA),多载波直接序列码分多址(MC-DS-CDMA)和多音频码分多址(MT-CDMA)。

3种系统的调制方式有所区别,在MC-CDMA系统中,不同的子载波上发送同一个符号,OFDM中不同的子载波携带不同的信息符号。在MC-DS-CDMA系统中,输入的信息符号先进行串并转换,对并行的数据用相同的扩频码进行扩频,再调制到不同的子载波上。在MT-CDMA系统中,对输入的信息符号进行OFDM调制,然后再经过较长的扩频码进行扩频[10]。

MC-CDMA系统方案有频率分集的效果,可提高频谱效率以及在抗频率选择性衰落方面有较好的性能。MC-DS-CDMA系统每个子载波上传输不同扩频码的同一个信息符号。MT-CDMA系统有较大的扩频增益,系统也可以容纳更大的用户容量。但因为在OFDM调制后扩频,破坏了OFDM子载波的正交性,因此系统的抗干扰能力较低[11]。

现有扩频系统使用的扩频码具有非常优秀的自相关与互相关特性。同时OFDM由于子载波的存在和循环前缀的添加具有优秀的抗多径能力。目前普遍使用的结合方式是在OFDM调制之前,对数据使用扩频码进行扩频。这种情况下需要考虑到:与OFDM数据进行扩频之后,再经过OFDM调制,扩频码的自相关特性和互相关特性会受到一定程度的影响,对最终系统的时延估计精度造成影响;同时,经过扩频之后,对原有的OFDM系统性能也会造成影响。而上面这3种结合方式虽然有所不同,但都是扩频码和OFDM符号扩频之后再进行OFDM调制。这样的结合方式会使扩频码的自相关性和互相关性受到破坏以及破坏了OFDM子载波的正交性,同时会对OFDM系统抗多径造成影响。

考虑以上不足,我们提出一种新的结合方式,扩频码与OFDM符号相结合的扩频OFDM信号发射框图如图2所示。

图2 扩频OFDM信号发射框图

扩频调制原理:输入的信息数据流先串并转换后,进行OFDM技术的多载波调制,对生成的OFDM符号添加循环前缀,再经过串并转换,并行符号数据流用相同的扩频码进行扩频,最后进行并串转换生成新的扩频OFDM符号。

该组合方式的优点是:扩频码不经过OFDM调制,而且和OFDM数据分开,使扩频码的自相关特性和互相关特性最大限度地得到保留,又不破坏OFDM子载波的正交性。同时使用OFDM可以提高电文数据传输速率以及利用OFDM的抗多径特性来减小时延对系统的影响。而且这样设计的调制方式相比于MC-CDMA,MC-DS-CDMA和MT-CDMA更加易于实现,系统复杂度更低。

2 基于FPGA的扩频OFDM信号模块化设计

本节通过时钟高精度模块、BPSK映射、OFDM调制设计、循环前缀模块与扩频OFDM产生模块的设计,在硬件层次上实现了扩频OFDM信号的模块化设计,完成了基于FPGA的扩频OFDM信号模块化的设计。

2.1 时钟信号产生与高精度同步模块

由于导航信号的设计采用扩频调制,好质量的信号对接收机的载波、伪码跟踪有着非常关键的作用,伪码测距是通过比较本地码与接收码之间的相位差来测得,因此伪距测量精度与时钟同步精度之间有着密切的关系。

硬件研发平台提供的外部时钟为200 MHz,它作为时钟信号产生模块的初始时钟,生成系统所需要的各种工作频率。按照系统设计,扩频码的周期为10 ms,码长为1 000,码速率为0.1 MHz,OFDM调制为64个子载波,循环前缀为OFDM符号的1/4。一个OFDM码片包含2个周期的扩频码,因此扩频前的数据速率为50 Hz。由于扩频之后需要串并转换,因此输出的扩频OFDM符号速率为0.1×80=8 MHz。这里对OFDM符号扩频采用了单比特扩频方式,即把8位的OFDM符号转变为1位的数据流进行扩频,因此OFDM符号串并转换后的速率为50/8=6.25 Hz,OFDM符号速率为50/8×80=500 Hz。另外还有一个1 PPS信号,1 PPS信号作为时钟模块的输入信号,同步工作时钟。

FPGA所提供的PLL(phase locked loop)模块,可以用来进行时钟延时消除、频率倍频分频、时钟相位调整等功能。它由鉴相器、环路滤波器和压控振荡器3部分组成,PLL利用外部输入的参考信号控制环路内部振荡信号的频率和相位,可以实现输出信号频率对输入信号频率的自动跟踪。由片外晶振提供的200 MHz时钟通过PLL与分频、倍频得到系统所需的所有时钟信号。首先通过PLL,产生一个32 MHz的中频时钟信号和8 MHz扩频OFDM符号时钟信号,0.1 MHz,500 Hz,50 Hz,6.25 Hz时钟信号用8 MHz的时钟信号分别通过计数器进行80,16 000,160 000,1 280 000分频产生。由于32 MHz的中频时钟信号与8 MHz的扩频OFDM符号时钟信号通过PLL产生,因此这两个时钟之间具有比较高的同步性。对于0.1 MHz,500 Hz,50 Hz,6.25 Hz时钟信号,用1 PPS秒脉冲信号进行同步,每当检测1 PPS秒脉冲信号上升沿到来的时候,对计数器重新置0以及对产生的时钟信号重新置1,以此保证产生的时钟信号不会因时间的问题而出现较大的延迟,达到高精度同步的要求。

2.2 BPSK映射

Matlab产生的导航电文存储在.coe文件,在FPGA中导入.coe文件,即可把导航电文存储在FPGA的ROM中,用查找表的方式,寻址将导航电文以500 Hz的时钟读出。根据BPSK调制原理,在FPGA设计中,采用直接映射的方式,即输入数据如果为1,则映射后的数据实部为0X40;输入数据如果为0,则映射后的数据实部为0X60,映射后的数据虚部均为0X00。映射后的数据格式为8位:1位符号位,1位整数位,6位小数位,负数用补码表示。

2.3 OFDM调制快速傅里叶逆变换(IFFT)设计

根据使用要求,对快速傅里叶逆变换(FFT)核的参数进行相应的设置。IFFT(inverse fast Fourier transform)的运算模块设计选用Xilinx公司的ISE平台v7.1的IP核,因需要对输入数据进行连续性处理,采用流水线结构(Pipelined Streaming I/O)对数据进行连续性处理,比突发式(Radix-4 Burst I/O)模式节省更多的资源,Block RAMs减少了6个,Slice减少了2个。IFFT变换长度配置为64,处理数据采用定点类型的数据,可以提高运算的精度。输入输出数据位宽设置为16 bits,输出顺序为自然顺序(nature order)。

2.4 循环前缀模块

循环前缀模块的实现主要使用两个地址空间为64的RAM存储IFFT模块输出的数据,地址信号由上一级IFFT模块输出数据的下标INDEX信号提供,循环前缀添加就是上一级的OFDM符号的后16个数据复制到前16个数据当中,最终每个OFDM符号形成80个数据。硬件实现框图如图3所示。

图3 循环前缀硬件原理图

循环前缀添加具体实现:将输入数据CP_IN的前48个数据存入到RAM中,从第49个数据开始输出数据CP_OUT,地址信号INDEX为输入数据CP_IN的下标,同时将输入数据CP_IN继续存入到RAM中,到第64个数据输出后,再将RAM中的64个数据按顺序读出。

2.5 扩频码产生模块

在Xilinx公司的ISE平台上,根据原理图的输入方式产生扩频码。在该模块中,输入端口clk,rsta,ena分别为扩频码时钟,给移位寄存器初始值数据重置信号,产生扩频码的使能信号。移位寄存器G1与G2的反馈系数分别取0X409和0X6E5,由于第0位不参加反馈,所以G1中把反馈系数为“1”的第3和10位进行模2相加,得到的结果反馈到移位寄存器1中[12];G2中把反馈系数为“1”的第2,5,6,7,9和10位进行模2相加,得到的结果反馈到移位寄存器1中。移位寄存器G2的第5和9位进行模2相加的值与移位寄存器G1的第10位再模二相加,生成的值即为Gold序列值。

通过rsta信号可重置移位寄存器的初始值。在ena信号使能时,通过移位寄存器G1与G2的反馈,产生扩频码。设计的扩频码前10位0X3E7。

2.6 扩频OFDM产生模块

扩频调制对OFDM调制后进行扩频,即对OFDM符号进行扩频。本设计实现的是对OFDM调制的每个子载波进行扩频,设计实现思路如图4所示。

图4 扩频OFDM原理图

设计中OFDM符号包含80个子载波,符号速率为500 Hz,扩频码码率为0.1 MHz,扩频OFDM符号速率为8 MHz。由于OFDM符号为8 bit的数据,而扩频码为1 bit,要实现对OFDM符号的扩频,本文提出了按位扩频,即对OFDM符号进行按位读取,将8位的OFDM符号的数据流转变为1位的数据流,再与扩频码异或相加完成对数据的扩频。

①串并转换的硬件实现,其中DATA为输入数据,DATA_Enable为输入数据有效信号,DATA_OUT为80路输出数据。DATA_Enable使能时,将高速率的输入数据DATA存到先进先出(FIFO)存储器中,如果输出的低速率并行时钟到来,一个模80的计数器开始计数,开始缓存输出80路并行数据,当计数器为79时,并行输出DATA_OUT。串并转换的硬件原理图如图5所示。

图5 串并转换硬件实现框图

②按位读取:将并行的符号速率子载波数据,用比特速率时钟来输出,变为比特速率数据流,在读取时,先读低位,后读高位。由于符号数据为8位,因此在FPGA设计中,比特速率为符号速率的8倍,需要一个以比特速率为时钟的模8计数器来进行计数比特数据输出。

③扩频的实质就是对信息码与扩频码的异或相加,对于80个并行支路,采用相同的扩频码进行扩频。因此在FPGA设计时,当信息码到来时,直接对信息码与生成的扩频码进行相加输出。80个支路的扩频方式与扩频码完全相同,因此在实现时可对扩频模块复用。

④并串转换的硬件实现原理与串并转换类似,只不过不用FIFO,当并行数据有效时,以串行数据速率为时钟的模80计数器开始计数,同时,串行数据开始输出。

3 基于FPGA的扩频OFDM信号半物理实现与仿真

各个子模块构建完成后,对整个扩频OFDM信号进行了构建,在顶层模块对各个底层子模块进行了例化,并进行了联合仿真,整个信号系统构架如图6所示。

图6 系统框图

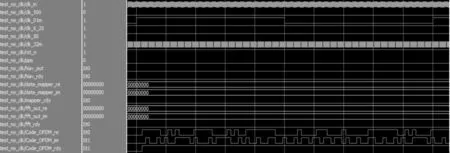

采用Xilinx公司的Virtex-7系列的VC7VX485T芯片对扩频OFDM信号进行了半物理实现与仿真。经过Xilinx XST综合器综合后,芯片内部资源占用情况,如图7所示。

图7 扩频OFDM信号资源占用情况

从系统资源占用情况可以看出,扩频OFDM信号的设计占用了14.7%的总资源。OFDM信号与扩频码结合的新型导航信号占用较少的资源,可以满足进一步研究的需求。

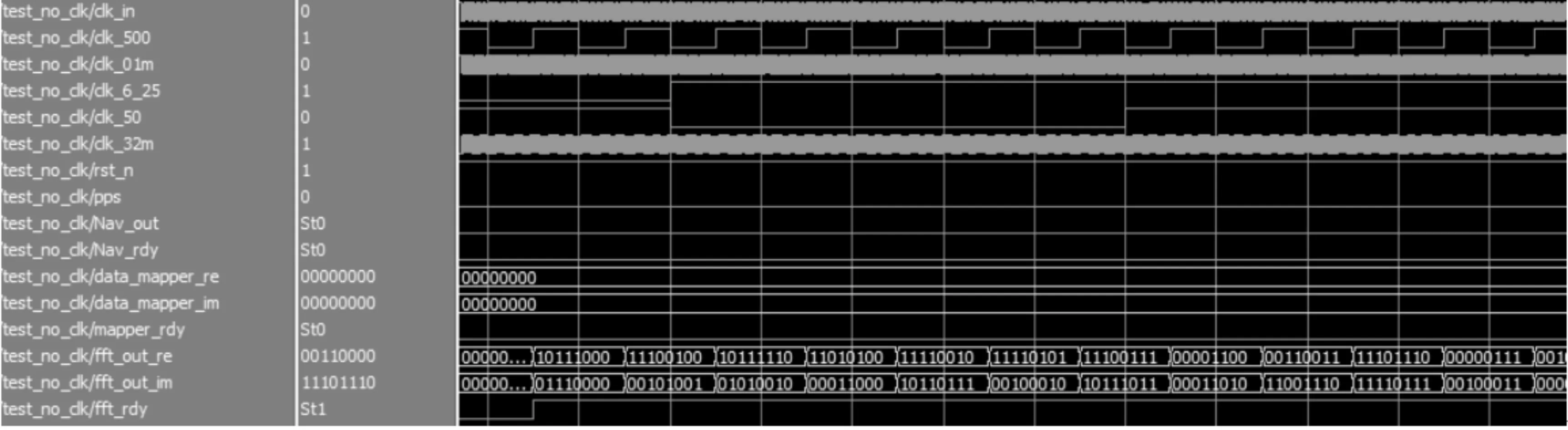

在对整个系统经过布局布线后,利用Modelsim软件进行了仿真。

①时钟信号产生

图8和图9为时钟模块仿真图。由仿真结果图8可以看出,当有PPS信号到来时,所有信号均为上升沿,信号同步一致。图9为时钟模块仿真结果的放大图,由图中可以看出,各信号之间是有些许不同步的,其中8 MHz与500 Hz时钟信号之间的时延最大,为1 209 ps,系统中使用的最高时钟频率为32 MHz,周期为31.25 ns,最大时延在系统时钟可以承受的范围内。

图8 时钟模块仿真图

图9 时钟模块仿真图

②扩频码产生

图10为扩频码设计的仿真波形,可以看出,在0.1 MHz的时钟脉冲控制下,当反馈寄存器G1,G2分别设置为0X409,0X6e5时,扩频码的前10位仿真波形,其扩频码的前10位为:1111100111,与设计的扩频码前10位0X3E7符合,该设计结果符合要求。

图10 扩频码生成仿真图

③扩频OFDM信号

图11为生成的OFDM符号,由图中可以看出前10个OFDM符号实部与虚部的最后一位分别为0000011010,0100101001,扩频码的前10位为1111100111,根据扩频OFDM的设计,OFDM符号的实部的每一位与扩频码异或相加进行扩频,虚部不进行扩频,其中OFDM符号的每一位包含两个周期的扩频码,再经过并串转换,输出扩频OFDM信号。因此,前10个OFDM符号实部与虚部和扩频码的第一位异或后,得到的扩频OFDM信号应为1111100101,0100101001。

图11 OFDM信号仿真图

图12为扩频OFDM符号输出,从仿真结果可以看出,扩频OFDM符号实部与虚部的前10位分别为1111100101,0100101001,仿真结果输出与预计值一致,扩频OFDM信号在FPGA上得到了正确的实现。

图12 扩频OFDM信号仿真图

4 结语

基于FPGA对扩频OFDM信号的设计,为后续扩频OFDM信号的工程化提供了可靠的技术支持。本文详细叙述了扩频OFDM信号的生成机理,通过FPGA的模块化设计,最后在硬件上实现了半物理仿真。仿真结果表明,文中提出的OFDM与扩频码的结合方式,占用较少的资源,实现复杂度低,具有一定的工程可实现性,为扩频OFDM基带的开发与研制奠定了技术基础。