基于低功耗SoC的微型图像采集系统设计

胡锦 谢立红 邹望辉 张磊 胡啸东

摘 要:针对低成本和低功耗的物联网SoC芯片发展要求,基于SMIC 55 nm CMOS工艺,以低功耗开源处理器RI5CY的SoC芯片为平台,结合片内含有DSP与A/D转换功能的低电压CMOS图像傳感器OV7725,设计并实现了一款基于开源 RISC_V指令集架构 SoC 芯片的图像采集控制系统.文中介绍了图像采集控制系统的结构,并详细阐述基于AHB总线的图像采集控制器的设计.控制器采用一种改进的异步FIFO来实现不同时钟域的同步设计,具有小面积和低功耗的特点.通过Modelsim仿真、DC综合以及 FPGA 验证,结果表明:该系统实现了视频图像数据的采集和传输,操作流程简单,易于软件调试,支持应用最高带宽可达37 MB/s. SoC芯片系统的时钟主频为200 MHz,芯片总面积为3 250 × 3 648 μm2,总功耗仅为24.419 mW.

关键词:图像采集;SoC;RISC_V;异步FIFO

中图分类号:TP368 文献标志码:A

Design of Miniature Image Acquisition System

Based on Low Power System on Chip

HU Jin1,XIE Lihong1,ZOU Wanghui1,ZHANG Lei2,HU Xiaodong3

(1. School of Physics and Electronics,Hunan University,Changsha 410082,China;

2. Institute of Computing Technology of Chinese Academy of Sciences,Beijing 100080,China;

3. Netforward Shenzhen,Shenzhen 518057,China)

Abstract: Based on the development requirements of low-cost and low-power Internet SoC chip, an image acquisition and control system is designed and implemented based on open source RISC_V instruction set architecture SoC chip and SMIC 55nm CMOS process, which uses the low-power open source processor RI5CY SoC chip as a platform and combined with the Low-Voltage CMOS Image Sensor OV7725 with the integrated DSP and A/D conversion chip inside. This paper introduces the block diagram of the image acquisition and control system, and describes a design of image acquisition controller based on AHB bus in detail. An improved asynchronous FIFO with low power and small area is used to realize the synchronous design of different clock domains. According to the results of Modelsim simulation, DC synthesis and FPGA verification shows that the system realizes the video image data acquisition and transmission,which operation flow is simple and easy to debug, and the maximum of the data transmission bandwidth come up to 37MB/s. The chip total area is 3250 μm x 3648 μm and power consumption is only 24.419 mW.

Key words: image acquisition;Soc;RISC_V;asynchronous FIFO

随着互联网技术、信息处理技术以及物联网技术的发展,以微处理器为核心的片上系统 (SoC),由于成本低、体积小、集成度高、功耗低等[1]优点,逐渐成为当今集成电路的主流,为集成电路产业提供了广阔市场和发展机遇[2].目前常见的图像采集系统大多基于PC机的图像视频采集卡,虽然性能上清晰度高、运算精度大,但成本较高、体积和功耗都较大,不适合应用在便携式电子产品中.嵌入式技术发展给图像采集提供了新平台,但单纯应用ARM或DSP等嵌入式平台由于其存储容量有限、处理速度低、扩展性较差的特点,不能满足当前图像采集系统的带宽需求.SoC系统芯片结合了这些优势,为需要实时性强和处理速度快的数据信息系统实现提供了较好的解决方案.

文献[3]利用单片机控制和USB数据采集技术等实现了视频数据的采集和传输,但数据传输速率为8~10 Mbps,难以完整采样和存储30 fps、640×480像素大小的视频图像.

文献[4]采用FPGA作为图像采集主控芯片,能較好实现图像数据的采样和传输,但操作流程繁琐,系统较为复杂,对于软件人员来说难以设计和调试,其功耗也相对较高.本文针对微型电子设备的应用场合,基于RISC_V指令集架构的开源处理器PULPino[5],设计了一款低功耗的图像采集控制系统,实现了CMOS图像传感器图像数据的输出、采集、存储.图像数据输入至神经网络ANN (Artificial Neural Networks)加速器中进行智能识别、图像处理或通过图像显示器进行显示,该图像采集系统操作流程简单,易于软件调试.

1 系统设计方案

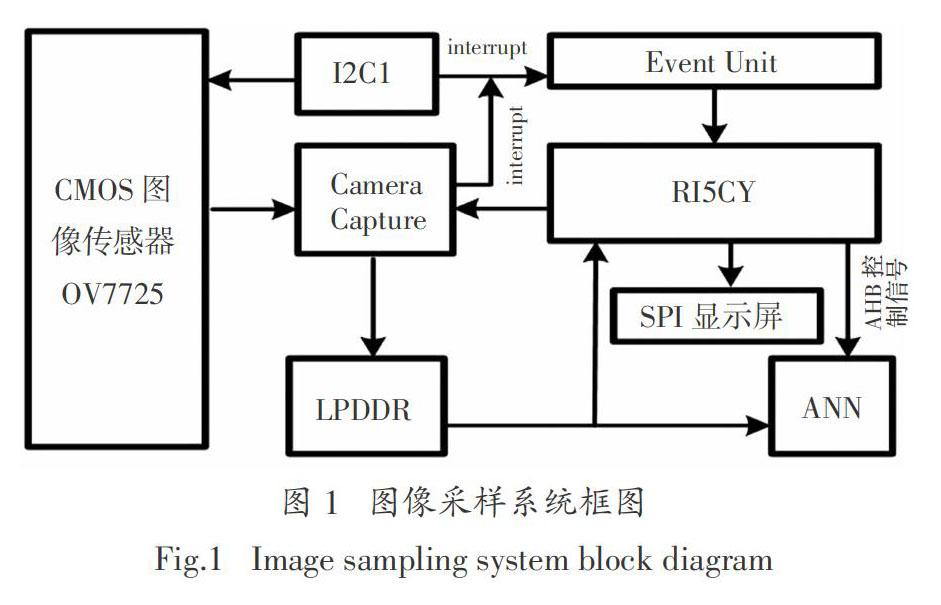

本设计选用OmniVision公司小型CMOS图像传感器OV7725为SoC芯片提供数字视频信号,针对当前物联网智能芯片的图像采集与处理需求,设计方案如下:

1)基于低功耗RISC_V的开源处理器PULPino(Parallel Ultra Lower Power)平台.

2)利用挂载在SOC系统APB总线上的I2C控制器与CMOS图像传感器OV7725进行信息交互,对图像传感器编程配置.

3)根据图像采集系统的应用场景,设计SoC系统图像采集控制器,实现在控制信号的控制下正确采集图像数据,并将图像数据通过AHB总线存储至LPDDR(Low Power Double Date Rate SDRAM).

4)基于LATCH 的异步FIFO实现图像采集时

钟域与系统时钟域的同步,能高效率利用总线和缓解控制器长期占用总线,提高整个SoC的工作效率.

5)图像传感器[6]输出图像的最大分辨率为640 × 480 (VGA),最大刷新率为60 fps.若图像输出格式为RGB/YUV格式,则每个像素点为两个字节,因此实际最大带宽需求为(2 Byte × 640 × 480 × 60 ) /106 = 37 MB/s.而AHB总线带宽为主频×位宽,即200 MHz × 4 Byte = 800 MB/s,满足视频图像采集带宽需求.

1.1 SoC低功耗设计

SoC平台采用big-little core平台来实现能耗充分利用,大小核时钟频率分别为200 MHz和80 MHz,根据具体应用场景可利用软件算法动态切换大小核.基于RISC_V指令集的处理器核RI5CY采用哈佛存储器结构,具有4级流水线,同时扩展的硬件循环指令、乘累加、高级算术指令为并行超低功耗提供理论依据.除了指令实现低功耗外,RI5CY处理器核具有正常工作模式和睡眠模式,在睡眠功能使能后,处理器在空闲时进入睡眠模式,中断和事件均会唤醒处理器.但中断唤醒处理器后,处理器先处理中断服务处理程序,处理完毕后若处理器空闲将再次进入睡眠模式,只有事件才能将处理器核永久唤醒,故动态功耗较低.系统中各外设IP模块均具有独立的门控时钟控制,可通过关闭不必要的外设IP达到系统功耗最低.在本图像采集系统设计中,相比于基于register的FIFO设计,采用基于latch的设计也有效降低了功耗和面积.

1.2 图像采集系统总体结构

图像采集系统主要由图像传感器OV7725、camera capture 控制器、I2C控制器、ANN加速器以及连接在menctrl 控制器上的LPDDR组成,如图1所示.系统工作原理为:系统上电后,系统MCU利用I2C模块使用标准SCCB(Serial Camera Control Bus)协议对图像传感器寄存器进行配置,设置工作方式.打开图像采集控制器使能,系统图像采集控制器对图像数据信号进行采集,通过异步FIFO进行数据缓冲和同步两侧不同的数据传输速率,camera capture控制器以帧为单位将图像数据写至内存.写完一帧图像数据之后触发中断,随后CPU对中断进行处理.

1.3 图像采集控制器设计

图像采集控制器主要实现图像传感器输出数据的采集,并与系统进行通信和交互.图像采集控制器分为以下模块:总线接口模块(AHB MASTER模块和 AHB Slave (CSR模块))、采样与同步模块(Camera Capture )组成,结构如图2所示.CSR(Control Status Register)模块作为总线的Slave接口,接收系统控制配置.通过配置可在内存中设定三个数据区(ZONE1/2/3)用于存储采集的图像数据.图像采集模块 (Camera Capture)以帧为单位对图像传感器输出的原始图像数据进行采集,通过AHB MASTER模块将图像数据写入相应的存储区.每当完成一帧的数据采集并写入存储区后,CSR模块的状态寄存器会记录DATA_OK,并向CPU发中断请求.CPU对采集到数据进行消费后清除状态寄存器对应的DATA_OK标志.每个数据区大小为一帧,控制器按ZONE1到ZONE3的固定顺序查找可用数据区,若全部的数据区均不可写,则产生错误中断.

1.3.1 CSR (Control Status Register)模块

CSR模块主要为软硬件交互接口模块,用于CPU对图像采集控制器的访问和寄存器的配置.根据具体应用场景,设计了以下寄存器(部分略):

BASE_ADDR_ZONE1/2/3 : 内存中设置的三个数据区(ZONE1/2/3)基地址寄存器,AHB MASTER模块根据该基地址和低位偏移对存储器进行访问.

RQCNT:此寄存器用于记录接收缓冲异步FIFO中的有效条目数.

RQTH:用于设置接收缓冲满阈值,当接收缓冲中的有效条目数大于或等于该阈值时,则记录在状态寄存器并向CPU发中断请求.

IntEn:该寄存器用来设置各中断使能.

Ctrl:控制寄存器.包括数据采集使能信号、场、行同步信号电平配置等控制信号.

1.3.2 Camera Capture模块

Camera Capture模块主要包括图像传感器采集接口模块、异步控制信号同步模块以及接收数据缓存FIFO模块,其结构框图如图3所示.

寄存器的配置与图像控制信号及数据信号之间为异步事件,因此需要硬件保证在切换控制寄存器中的控制信号时以一帧数据为边界.Vsync、href有效电平极性的切换只有在数据采样使能无效时才能软件配置,故只需保证切换数据采样使能时以帧为边界.具体实现的电路图如图4所示.

数据采样使能开启前需要先配置场、行信号的有效极性,数据采样使能开启后,电路只在Vsync有效时对采样使能寄存器进行更新(图4中带使能的触发r_CaptureEnTrue).该信号同时作用于采樣数据接收使能信号(c_WrRcvData-En),硬件上保证正在接口传输的此帧图像数据被忽略,从下一帧图像数据开始采集.同理,电路保证了关闭数据采样使能信号时正在采集的这帧数据被采集完,下一帧图像数据开始被忽略.数据采样使能信号、行、场控制信号形成新一帧图像数据开始标志,并输出至AHB MASTER模块复位索引地址.此时,上一帧图像数据采集完毕并存储至相应的数据区中,新一帧图像数据采集开始.

基于Latch的跨时钟域异步FIFO模块是数据缓冲操作的核心.图像传感器的图像数据采集基于数据帧的突发操作,为提高总线利用率和传输速率,设计了8 × 128的接收数据缓冲FIFO.将像素图像数据拼凑齐16Byte后使FIFO写使能有效,以便总线产生(INCR4)突发请求.由于并不需要在像素时钟下拍拍连续写数据,故本设计中的FIFO采用Latch阵列实现,能有效减小芯片面积和功耗.设计中还采用N+1位格雷码计数器模块来产生空满标志,在减小亚稳态出现概率的同时避免算术运算,提高了FIFO的速度.

1.3.3 AHB MASTER模块

AHB MASTER 模块是AHB总线的master接口模块,该模块用于发起对存储器的访问.针对图像采集系统的应用场景,只需要发起对存储器的写操作.总线地址宽度和数据宽度均为32位,并支持总线提前中止传输(Early Burst Termination).模块采用状态机实现,状态流程图如图5所示.

IDLE状态:状态机的初始状态.在该状态下,若接收缓存FIFO不空而且没有协议错,则跳转至REQBUS状态;若接收缓存FIFO不空,但有协议错,读取FIFO的数据.若FIFO为空,不进行操作.

REQBUS状态:发起总线请求.该状态下总线请求信号mHBUSREQ信号有效,并等待仲裁器授权总线使用权.若总线申请成功,则跳转至REQESND状态.

REQSEND状态:命令和数据发送状态.该状态会维持至传输正常完成或传输提前中止.在图像采集模块中,设置四位Flitv发送指示,其中FIFO中的每32位对应Flitv中的一位.若某位为1,则表示该32位数据未发送.当状态机进入REQSEND状态时,若Flitv发送指示全为1,则总线的突发请求为INCR4;若突发操作被EBT(Early Burst Termination),MASTER会继续发起总线请求.此时若Flitv发送指示只有一个1表明EBT后剩余一个32位数据未发送,此时发起SINGLE总线突发请求.若Flitv发送指示包含多个1表明EBT后剩余多个32位数据未发送,此时发起INCR总线突发请求.

ENDDATA状态:最后数据发送状态.此状态中传输正常结束,读取FIFO中的数据.当mHREADY有效时,状态机返回至IDLE状态.

2 仿真与验证

图像采样控制器的设计使用Verilog HDL 语言实现.为验证其功能的正确性,分别进行了系统级的功能仿真验证和FPGA验证.在仿真验证中,编写了模拟CMOS传感器OV7725的行为功能模型(BFM),构建了软硬件验证平台,利用Modelsim SE-64 10.2环境进行功能仿真,并利用Synopsys综合工具DC (Design Compile)进行综合,最后利用FPGA进行板级验证.

图6所示的是图像采集模块的仿真图,可以看出,当图像采集系统使能后,当前帧数据被忽略,图像数据从新一帧开始采集.场信号有效后,行信号有效,图像采集模块在像素时钟信号pclk上升沿进行图像信号(data)的采集.

AHB Master总线写数据至存储器仿真图如图7所示.采集模块将采集的图像数据缓存于异步FIFO中,然后将第一帧图像数据存在CSR设置的在存储器LPDDR基址2202000的数据区.当写完一帧数据后,图像采样模块产生DATAOK_ZONE1(2/3)中断.

仿真结果表明,该视频图像采集系统能够很好地实现图像数据的采集和数据传输.

利用Synopsys公司的Design Compile工具,采用SMIC 55nm CMOS工艺库文件,在系统时钟为200 MHz时对整个SoC芯片进行综合.由综合结果得到芯片功耗报告如表1所示,其中芯片的总功耗仅为24.419 mW,动态功耗为23.804 mW.

为了减小芯片面积和功耗,本文采用了基于Latch的FIFO设计,并在相同工艺下分别对基于Register的FIFO和基于Latch的改进FIFO的SoC芯片系统进行综合,分别得到总功耗与含有FIFO的图像采集模块面积并进行比较,对比结果如表2所示.

FPGA验证环境[7]包括Xilinx公司的7系列ARTIX-7 FPGA核心板和带有LPDDR及FLASH的扩展板.其中ARTIX-7 FPGA核心板由FPGA芯片XC7A100T +128 Mb QSPI FLASH组成,扩展板包含FPGA IO扩展口、数据和控制信号接口、LPDDR、CMOS图像传感器OV7725以及FLASH芯片.

为验证图像采样模块的正确性,使用Xilinx的工具Vivado产生网表和bitstream文件,并用JTAG下载器下载至FPGA芯片XC7A100T中.利用连接在SoC系统中SPIMaster上的SPI显示屏进行图像显示.如图8所示的为FPGA图像采集验证结果.

FPGA时钟管理模块提供给SoC系统时钟为50 MHz,板级提供给图像传感器OV7725的系统输入时钟为30 MHz.在I2C模块配置图像传感器后,图像采集系统稳定采样并在较少CPU干预下实现数据存储至LPDDR,数据传输带宽为30 MB/s,满足图像视频的传输速率要求.由显示屏显示结果可以得到,图像采集系统采样正确并存储数据信息,图像显示效果较好且无失真.

3 結 语

本文针对物联网SOC芯片图像采集的特定应用,设计并实现了图像采集控制系统.该图像采集控制系统通过采集图像传感器的数据和控制信号,并通过改进的异步FIFO,实现了不同时钟域的数据传输.仿真和验证结果表明,该设计能很好地采样图像数据,并利用总线在较少CPU干预的情况下,以帧为单位将数据高效率传输至内存.由显示屏显示图像的验证结果可以得出,该采集系统采集的图像质量好,画面清晰,并具有操作过程简单、灵活、方便等优点,验证了该设计的可行性.

参考文献

[1] MITIC M,STOJCEV M,STAMENKOVIC A Z M. An overview of on-chip buses[J]. Facta universitatis - series: Electronics and Energetics,2006,19(3):405—428.

[2] DUTT N,JANTSCH A,SARMA S. Toward smart embedded systems: A self-aware system-on-chip(SoC) perspective[J]. ACM Transactions on Embedded Computing Systems,2016,15(2):1—27.

[3] 商婷婷. 基于MSP430的网络化视频监控系统的设计[J]. 电子设计应用,2007(9):110—111.

SHANG T T. Design of networked video surveillance system based on MSP430[J]. Electronic Design Application,2007(9):110—111. (In Chinese)

[4] 周泉,马俊,董亚男,等. 基于低功耗微控制器的图像采集系统设计[J]. 电子测量技术,2014,37(3):77—81.

ZHOU Q,MA J,DONG Y N,et al. Design of image acquisition system based on low power microcontroller[J]. Electronic Measurement Technology,2014,37(3): 77—81. (In Chinese)

[5] ZIMMER M,BROMAN D,SHAVER C,et al. FlexPRET: A processor platform for mixed-criticality systems[C]// IEEE Real-time & Embedded Technology & Applications Symposium. IEEE,2014:101—110.

[6] OmniVision Technologies Inc.OV7725 color CMOS VGA (640×480) CAMERACHIPTM sensor omni Vision ■ with OmniPixel2TM technology,advanced information datasheet[R]. California: ALLDATASHEET,2007,Version 1.4. https://www.alldatasheet.net/view.jsp?Searchword=OV7725.

[7] 李列文,桂卫华,胡小龙. 一种基于FPGA的低功耗、容错状态机设计方法[J]. 湖南大学学报(自然科学版),2010,37(6):77—82.

LI L W,GUI W H,HU X L. Low power consumption based on FPGA design method of fault tolerant state machine[J]. Journal of Hunan University(Natural Sciences),2010,37(6): 77—82.(In Chinese)