基于PicoRV32开源处理器的SOC平台搭建

摘" 要: 由于现有的处理器架构及IP核存在授权费用高、兼容性差等问题,近两年出现的新型RISC⁃V架构有着开源、免费等优势,文中基于RISC⁃V指令集的PicoRV32开源处理器,搭建一个精简SOC硬件平台。通过运行呼吸灯测试程序,验证了该平台的正确性。在Xilinx XCVU440的FPGA开发板下资源显示最高频率为381.2 MHz,LUTs为1 137。可见PicoRV32开源微处理器具有逻辑门数少、跑频高的优点,可被用作FPGA设计和ASIC设计的辅助处理器,具有较高的研究价值和应用前景,并且所设计的平台可适用于其他处理器的SOC搭建及FPGA综合验证。

关键词: 开源处理器; RISC⁃V; Verilog HDL; 呼吸灯; SOC硬件平台; 平台验证

中图分类号: TN43⁃34" " " " " " " " " " " " " 文献标识码: A" " " " " " " " " " " " " "文章编号: 1004⁃373X(2019)21⁃0090⁃04

Abstract: Because the now available processor architecture and IP kernel has high licensing fee, poor compatibility and many other historical burdens, the new RISC⁃V architecture emerging in the last two years has the advantages such as open source and charge free. Therefore, a streamlined SOC hardware platform has been built on the basis of PicoRV32 open source processor with RISC⁃V instruction set. The correctness of the platform was verified by running the breathing light test program. Resources on the FPGA development board of Xilinx XCVU440 show: the highest frequency is 381.2 MHz and the LUTs are 1 137. It can be seen that the PicoRV32 open source microprocessor has the advantages of fewer logic gates and higher running frequency, which can be used as an auxiliary processor for FPGA design and ASIC design, and has high research value and application prospect. The designed platform is applied to SOC setup of other processors and FPGA comprehensive verification.

Keywords: open source processor; RISC⁃V; Verilog HDL; breathing light; SOC hardware platform; platform verification

0" 引" 言

当今芯片发展对SOC设计的高要求,迫使采用集成面积小、性能高、结构简单的CPU。有两个重要的因素制约了对新结构的探索,即已有的软硬件生态系统和开发成本[1]。目前,各大公司研发推出自己的软核处理器,其中ARM处理器和Power PC处理器不提供开源代码,使用时需要较高的授权费;Altera公司的Nios Ⅱ处理器和Xilinx公司的MicroBlaze处理器虽然提供免费的开发平台,但是不提供HDL源代码,在IP配置时受限制,并且这些处理器只兼容他们公司自己的相应器件,具有一定的局限性;OpenCore组织开源公布的Open RISC系列OR1200处理器的软件开发包中没有图形化配置界面[2],配置分析相对麻烦、不灵活,并且这些IP的内核和工具生态系统十分封闭,开发人员也无法或仅有极少开发空间来把软件移植到其他架构中[3]。这样的现状在一定程度上限制了研究者对微处理器的深入研究,进而减缓了对微处理器的研发设计和商业化应用进程。所以。在摩尔定律预言濒临终结、计算微体系结构日趋成熟,新的开源指令架构RISC⁃V系统架构萌芽发展,为开源处理器的多样化设计开辟了新的前景。本文所研究的PicoRV32微处理器就是一款基于RISC⁃V指令集架构的开源微处理器,通过设计和搭建硬件平台,编译软件测试程序进行验证,在一定程度上展示了PicoRV32处理器的研究应用价值。

1" RISC⁃V概述

1.1" RISC⁃V指令集

RISC⁃V是继RISC⁃I,RISC⁃Ⅱ,SOAR和SPUR之后推出的第五代精简指令架构,由加州大学伯克利分校(University of California at Berkeley)的研究者设计发布的一款免费开源指令集,最初被设计为面向计算机架构的研究和教育领域[4],可根据系统实际需求自由扩展硬件和软件架构,近一两年受到业界和学者的广泛关注和重视[5]。其中,基于该指令架构的Rocket开源处理器采用台积电公司40 nm工艺时的性能[6],与采用相同工艺的标量处理器ARM Cortex⁃A5的性能对比,其占用面积小、动态功耗低,整体性能等方面明显更优。相对于商用指令架构和开放指令架构,RISC⁃V指令架构可以提供更有利于研究和应用的设计优势,如支持用户级指令和特定用户的应用扩展,支持高度并行的同异构多核或众核实现技术开放,可免费应用于学术和商业等。值得一提的是,所有的RISC⁃V软件工具也是开源的,比如,Icarus Verilog(Iverilog),它是一个开源的Verilog仿真综合工具,在进行平台仿真验证时,可采用批处理的方法将代码编译、启动仿真工具、查看波形等过程统一为一个操作。像开源IP、软件工具都能在开源社区中找到,这样能更好地支持和维护处理器的硬件开发和学者研究。

针对RISC⁃V指令架构特点对存储器访问的研究发现:

1) RISC⁃V架构只支持小端模式,考虑到主流的应用大部分也是小端模式,这样可以简化硬件的实现;

2) 不同于其他RISC处理器,RISC⁃V架构的存储器的读写指令不支持地址自增自减模式,这也是RISC⁃V架构简化硬件的目标,在不支持地址的自增自减模式下,对处理器访问连续存储器地址区间具有一定的局限性,但是,可以很大程度上简化地址的生成逻辑,从而减小集成面积;

3) 在指令规划方面,虽然在传统的RISC处理器中,只需要执行“一次读多个数据”或“一次写多个数据”这样的一条命令就可以完成多步操作,但弊端是会让处理器的硬件设计增加难度,加大了硬件的开销,时序要求更难达到,无法提高主频,优化处理器性能。所以在RISC⁃V指令集中舍弃了这两条指令。

1.2" PicoRV32处理器

PicoRV32是由Clifford wolf 工程师设计的开源处理器。其采用RISC⁃V指令集架构,遵循作者设计的私有总线规则,可配AXI4⁃Lite总线协议和wishbone总线协议,采用Verilog语言编码、32位寻址空间,提供一个独立的IP核接口,该IP核可用于创建自定义核,方便设计者进行自主研发,PicoRV32微处理器的高频特性可以应用在大多数现有的SOC设计中。此外,PicoRV32微处理器也可配置协处理器接口(Pico Co⁃Processor Interface,PCPI),可以应用在CPU内核外,不需要分支命令的传输。外部协处理器内核可以进行译码、执行,结果值可以自由地写入相应的寄存器。为了实现更低的硬件开销,PicoRV32中配置的中断处理IRQ可以不遵循RISC⁃V所享有的ISA规范,而是通过一组自定义指令实现IRQ处理,这样的设计也是为了进一步减少硬件逻辑。

2" 基于PicoRV32的SOC平台搭建

本文设计和搭建的平台基于RISC⁃V指令架构中的基本配置指令集,即RV32I指令集,以PicoRV32处理器为核心,集成ROM,RAM,并行输入/输出(parallel in out,PIO),乘除法功能模块。其中,各个功能模块与PicoRV32微处理器之间以私有总线接口互连,按照PicoRV32微处理器开发人员定义的传输规则进行模块间的数据信息传输。搭建的SOC系统平台框图如图1所示。

图1a)设计的是通过PicoRV32的私有总线搭建的SOC平台,可在RISC⁃V系统架构下完成处理器的基本读写操作。在平台设计和搭建过程中,为了得到更小的SOC系统,针对模块的物理地址区分问题,采用MUX选择的方式,目的是使用尽可能少的逻辑门将PicoRV32所处理的数据信息传输到指定的功能模块中。图1b)是基于AMBA3 AXI⁃Lite标准总线设计的,在 AXI⁃Lite标准总线上挂载AXI标准接口的RAM,ROM 模块,经过AXI to APB转接桥集成GPIO外设,该AMBA标准总线下设计的SOC平台可以适用于其他处理器,由于PicoRV32开源微处理器为了尽可能减少不必需的硬件逻辑,所以没有调试功能这部分,在图1b)设计的SOC平台中,可以通过挂载其他可调试标准接口处理器对PicoRV32进行调试,从而解决PicoRV32无法调试的问题。

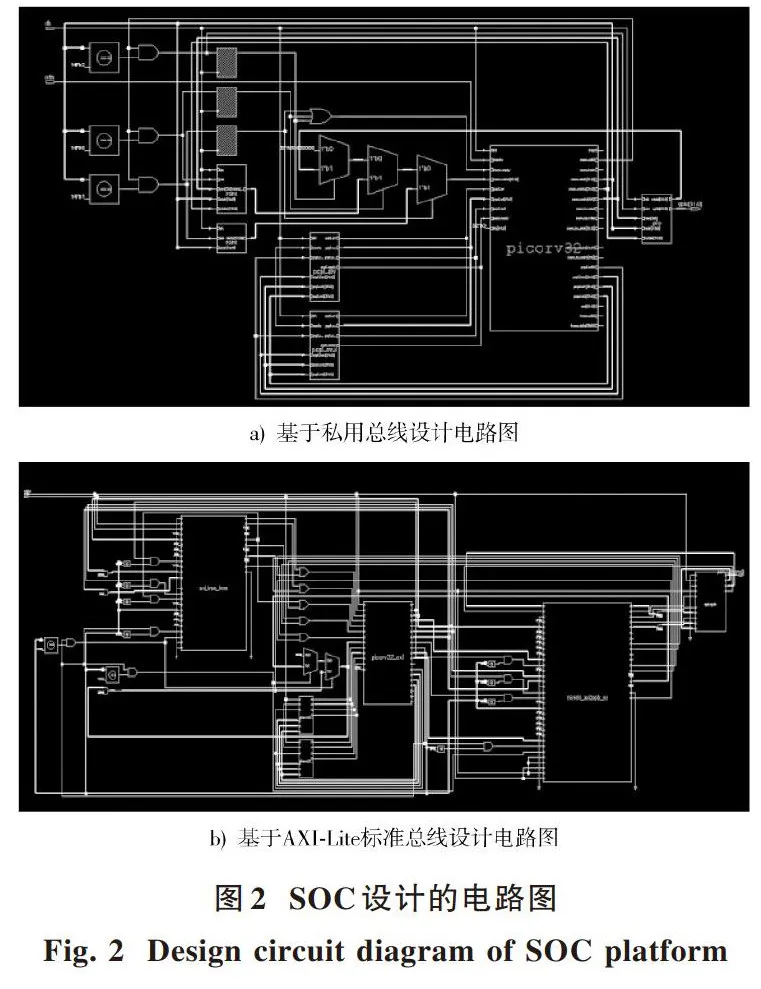

根据上述设计的两种结构,在Linux操作系统中进行搭建集成。其中,这两种不同的接口是通过宏定义配置选择,采用Verdi仿真工具查看由硬件代码模拟生成的电路图,如图2所示。经与所设计的SOC系统框图对比确认,所搭建的精简SOC平台与设计结构图一致。

搭建此平台可以兼容存储器接口的处理器,也适用于AXI标准协议接口的处理器,比如,R15CY,mRISC⁃V,ORCA,SCR1等RISC⁃V处理器IP核,在研究其他RISC⁃V处理器IP核时,可以在此平台进行仿真验证和综合验证,具有一定的通用性。

3" SOC平台测试验证

3.1" SOC平台验证环境

本次SOC平台采取软硬件协同验证[7],验证开发环境如下:

软件条件:在Win10系统上安装VMware Workstation虚拟机+Ubuntu系统。

硬件环境:首先,从github开源社区下载PicoRV32 IP核源代码,并在Linux操作系统中设计集成,生成可综合文件,使用synplify premier 综合工具对文件进行编译综合,输出综合报告。

3.2" 编写呼吸灯程序

实现呼吸灯的设计方法有多种,可采用脉冲宽度调制(PWM)驱动LED和定时器电路等方式。PWM方式具有易控制、功耗小并且相对直观的优点[8]。呼吸灯程序通过控制电路的开关时长实现脉冲宽度调制,采取PWM正调光,即PWM为高电平时LED发光,低电平时LED不发光。因此,当占空比为100%时,LED灯最亮;占空比为0%时,LED灯熄灭。

根据视觉暂留效应,频率大于100 Hz肉眼是无法分辨出闪烁的,因此,将PWM的脉冲周期设置为10 ms。LED灯在某个周期内的通断比例不同,会出现不同程度的亮度。采用PWM技术,通过调整占空比,调整LED灯的亮度,使LED灯实现从亮逐渐变暗,再从暗逐渐变亮的顺序循环,从而在实验观察中呈现出呼吸灯的效果。

3.3" SOC平台呼吸灯仿真

针对设计的SOC平台,采用riscv32i⁃unknown⁃elf⁃gcc编译工具编译[9]呼吸灯程序,生成elf文件和hex文件。在软硬件协同验证设计中,有两种针对处理器启动的方式:

1) 将hex文件固化进ROM模块中,通过ROM模块的只读功能在PicoRV32启动时直接从ROM中取指运行;

2) 通过task任务调用hex文件写入RAM模块中,在PicoRV32启动时从RAM模块中进行取指运行。实验系统中,采用将hex文件中的代码信息写入RAM模块,合理分配数据段和代码段,通过仿真工具进行编译生成vcd文件查看波形,以波形图与呼吸灯明暗变化的对应关系验证SOC平台设计的合理性。

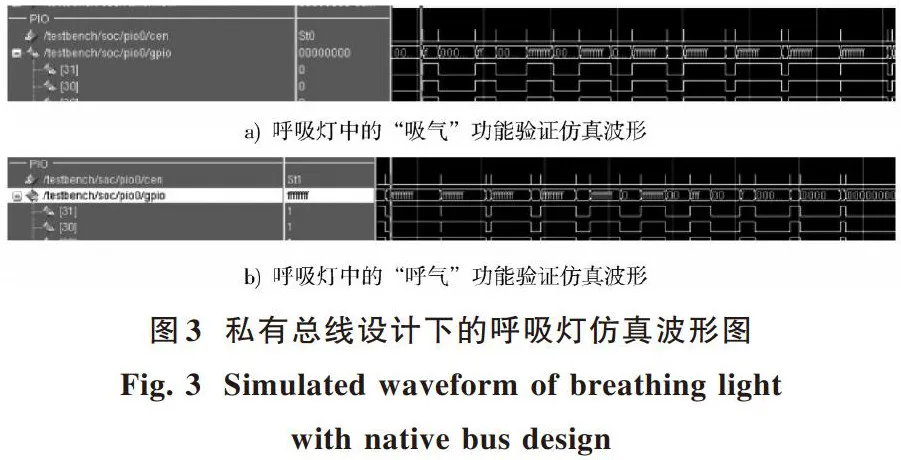

在Linux环境平台下针对所设计的两种不同端口的SOC搭建平台,加载编译呼吸灯软件程序,通过ModelSim软件仿真工具验证,如图3所示。

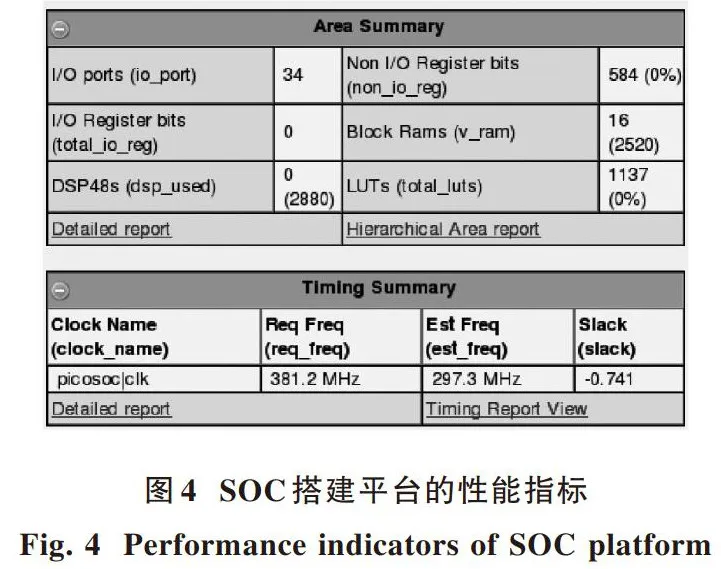

从图3a),图3b)中不难看出,将PIO模块的gpio端口输出相邻的全零(低电平)和全F(高电平)看作为一组,从仿真波形中不难看出,输出的每一组中的全零和全F比例为等差规律变化,根据视觉暂留效应,肉眼看到的光强应为每一组中全零和全F的叠加效果,从而模拟出LED灯如人呼吸一样的光感效果。从仿真波形上可以看出,PicoRV32将加载到RAM中的代码编译信息正确传输到PIO模块的gpio端口,在使能端控制下,驱动流水灯执行亮灭循环的变换,该仿真波形与软件测试程序一致,说明此SOC验证成功。该SOC硬件平台的SOC验证平台适用于其他任何处理器的验证。再通过synplify premier综合工具对该SOC平台进行性能分析,输出资源报告如图4所示。

从图4中可以看出,设计的SOC平台总LUTs为1 137,主频可以跑到380 MHz左右,性能指标在现有的开源处理器中有很大的优势。同理,在AXI⁃Lite标准总线下也进行了同样的验证,如图5所示,仿真波形与测试程序一致,说明所搭建的AXI⁃Lite接口SOC硬件平台验证成功。

4" 结" 论

本文搭建了基于PicoRV32软核开源处理器,采用RISC⁃V指令集的硬件设计平台,通过运行呼吸灯测试程序进行平台验证,得到的仿真波形与测试程序功能一致,验证了所设计平台系统的合理性。在Xilinx XCVU440的FPGA下编译综合[10],最高频率为381.2 MHz, LUTs为1 137,可以说明通过集成精简的SOC系统能够完成基本的读写数据操作和相应的功能实现,并且能为总线挂载带有调试功能的处理器,为解决PicoRV32微处理器的无调试问题提供平台搭建方案,从而更为容易和广泛地移植到其他的SOC系统中,同时在一定程度上说明了PicoRV32开源处理器的研究开发潜力和商用化前景。其中,在遵循AMBA标准总线协议下搭建的SOC硬件平台也可以适用于更换为其他处理器IP核的仿真验证和FPGA综合,也为研究不同处理器的性能分析比较评估带来方便。

参考文献

[1] 唐志敏.高端处理器芯片的技术趋势与可持续发展[J].电子产品世界,2017,24(4):27⁃29.

TANG Zhimin. The Technology trend and sustainable development of high⁃end MPU [J]. Electronic engineering amp; product world, 2017, 24(4): 27⁃29.

[2] 危必波.基于LEON3的SoC平台搭建及嵌入式Linux系统的移植研究[D].武汉:武汉工程大学,2014.

WEI Bibo. SoC platform build and research of embedded Linux system porting based on LEON3 [D]. Wuhan: Wuhan University of Engineering, 2014.

[3] MARENA T.RISC⁃V:改变SoC器件的开发[J].中国电子商情(基础电子),2017(12):34⁃35.

MARENA T. RISC⁃V: Changing the development of SoC devices [J]. China electronic business (Basic electronics), 2017(12): 34⁃35.

[4] GROSS H, JELINEK M, MANGARD S, et al. Concealing secrets in embedded processors designs [M]. Norwich: Springer International Publishing AG, 2017.

[5] 李佳师. RISC⁃V架构将是我国物联网芯片逆袭机会?[N].中国电子报,2018⁃08⁃28(007).

LI Jiashi. Will the RISC⁃V architecture be an opportunity for China′s Internet of Things chip counterattack? [N]. China electronics news, 2018⁃08⁃28 (007).

[6] 雷思磊.RISC⁃V架构的开源处理器及SoC研究综述[J].单片机与嵌入式系统应用,2017,17(2):56⁃60.

LEI Silei. Overview of open source processor and SoC research in RISC⁃V architecture [J]. Microcontrollers amp; embedded systems, 2017, 17(2): 56⁃60.

[7] 张明文.SOC技术在微电子芯片设计中的应用[J].信息与电脑(理论版),2016(13):66⁃67.

ZHANG Mingwen. Application of SOC technology in microelectronic chip design [J]. Information and computer (Theoretical edition), 2016(13): 66⁃67.

[8] 郭占苗,宋雪松.呼吸灯的设计与制作[J].自动化与仪器仪表,2017(1):32⁃34.

GUO Zhanmiao, SONG Xuesong. Design and production of breathing lamps [J]. Automation and instrumentation, 2017 (1): 32⁃34.

[9] 雷思磊,王军,张海燕.开源片上系统Freedom E310调试过程原理分析[J].单片机与嵌入式系统应用,2017,17(9):19⁃22.

LEI Silei, WANG Jun, ZHANG Haiyan. Debugging process principle analysis of open⁃source SoC freedom E310 [J]. Microcontrollers amp; embedded systems, 2017, 17(9): 19⁃22.

[10] FARHAT A, HOMMOS O, AL⁃ZAWQARI A, et al. Optical character recognition on heterogeneous SoC for HD automatic number plate recognition system [J]. EURASIP journal on image and video processing, 2018(1): 1⁃17.