分布式远程模拟量信号采集系统设计

崔永俊,张 祥,刘 坤,李康康,杨卫鹏,乔帅雅

(1.中北大学,电子测试技术国家重点实验室,仪器科学与动态测试教育部重点实验室,山西太原 030051;2.山西一建集团有限公司,山西太原 030000)

0 引言

在工业生产和航天航空领域,大型自动化设备普遍被使用,作业环境的恶劣,往往会危及到设备的运行和工作人员的人身安全,所以实时监测一些外界的物理量参数如电压、压力、温度、光强等是必不可少的。在某些测试环境中面临大面积采集、长距离传输及精度要求高的问题,传统的采集测试方案着重单一区域,其传输距离短,精度偏低,不足以适应大型远程高精度测试的需求,为解决这类问题,本设计提出了以RS485总线为主线,总分结构的方案,分布式的设计拓展了采集的节点数,适合大范围使用,其中一个节点采集通道数目的增多,也使单一区域数据采集面更详细均匀,高精度前端模数转换采集芯片ADS1258提高了采样精度,其自循环通道扫描功能省去了传统多通道的开关选通电路,简化了电路设计[1]。另外,系统通过阻抗匹配提升了总线数据长距离传输抗干扰能力,实现了远距离稳定传输。

1 整体方案设计

根据需求,设计的模拟信号输入量程范围为0~5 V,频率范围在1 kHz以内的交流信号及直流信号,采集精度要求大于16位;每个节点的通道数大于12路。所以选用了AD转换芯片ADS1258,其输入量程范围为0~5 V;精度24位;支持单节点16路通道;每通道采样频率23.7 kS/s满足设计要求且冗余[2]。总线要求节点数为12个;传输速率20 Mbps,传输距离500 m。所以选用基于RS485总线搭建有线数据采集网络,最远传输距离1 200 m,隔离式收发器ISO1176T芯片作为RS485总线芯片,传输速率可高达20 Mbps以上,能支持32个节点。整体结构框图如图1所示。

系统的工作流程:

(1)上位机通过W5300网口发送命令给背板,背板对命令进行解析与重组后发送给总节点;

(2)总节点接收到命令之后,将命令送至RS485总线上;

(3)12个分节点分别接收RS485总线上的命令并对其解析匹配;

(4)命令匹配成功的分节点配置数据转换寄存器,并开始采集与转换;

(5)采集转换完一次,分节点将转换结果打包成数据包发送至RS485总线上;

(6)总节点读取总线上的数据,再经SPI总线发至背板;

(7)背板将数据重新组合,通过W5300网口上传给上位机保存和显示。在发送过程中,上位机每次只发命令给一个分节点,在接收过程中,总节点一次只接收一个分节点的数据,其他节点保持静默,有效避免了RS485总线上的数据冲突的现象[3]。

2 硬件设计

2.1 模数转换模块设计

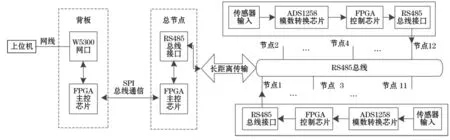

模数转换芯片选用高精度芯片ADS1258。该芯片具有较高的转换精度,快速的采样转换频率,而且转换通道多,采样频率可灵活配置。模数转换芯片的电路连接如图2所示。

将ADS1258模数转换芯片的CLKSEL时钟选择引脚接3.3 V拉高,引脚XTAL1与XTAL2间不接外部晶振,而是从引脚CLKIO输入FPGA控制芯片产生的16 MHz时钟信号。ADS1258的SPI引脚AD_SCLK、AD_DIN、AD_DOUT、AD_CS引脚,经22 Ω排阻后与FPGA控制芯片连接,用以配置其内部寄存器,引脚AD_START、AD_RESET、AD_/DRDY、AD_PWDN经22 Ω排阻与FPGA控制芯片连接,分别控制转换开闭、复位、数据转换完成及低功耗设置。在MUXOUTP、MUXOUTN与ADCINP、ADCINN间分别接运放365用以控制其内部转换器的延时时间,目的是保证中途切换到一个新通道而新的转换还没开始的间隔时间[4]。

另外,ADS1258芯片有3处供电:

(1)数字部分是与FPGA连接,DVDD接3.3 V,DGND接数字地;

(2)模拟部分AVDD采用0~5 V供电,供电电压与采集的模拟信号电压范围相关,AVSS接模拟地;

(3)参考电压:VREF=VREFP-VREFN,因为参考电压的稳定性关系到芯片采集精度,设计以高精度基准稳压芯片AD586产生5 V电压作为参考电压输入,精度达 2 mV,且具有较低的噪声漂移性[5]。

2.2 RS485总线抗干扰与失效保护设计

2.2.1 抗干扰设计

在长距离通信传输时,必须要采取避免信号反射的措施,否则信号抗干扰能力与可靠性会大大降低甚至无法通信。反射原因主要有2种:一种是阻抗不连续。电缆的阻抗突然变小甚至为0时,信号会反射,其反射原理跟光线从一种媒介到另一种媒介会引起反射是类似的;另一种是阻抗不匹配。主要分为源端阻抗不匹配和负载端阻抗不匹配。由负载端反射系数公式:ρL=(ZL-ZO)/(ZL+ZO),当负载端阻抗ZL大于传输线阻抗ZO,ρL>0,负载端不能全部吸收源端能量,多余能量将反射回源端,处于欠阻尼状态,此时易发生过冲甚至振铃,这样的电压波动可能跨越逻辑电平的阈值电压,致使接收端误判;负载端阻抗ZL小于传输线阻抗ZO,ρL<0,负载会消耗比源端传输的能量更多,故通过反射向源端寻求更多能量,处于过阻尼状态,会引起环绕振荡,造成时序冲突,使得传输链的数据发生紊乱。源端的阻抗分析同上。

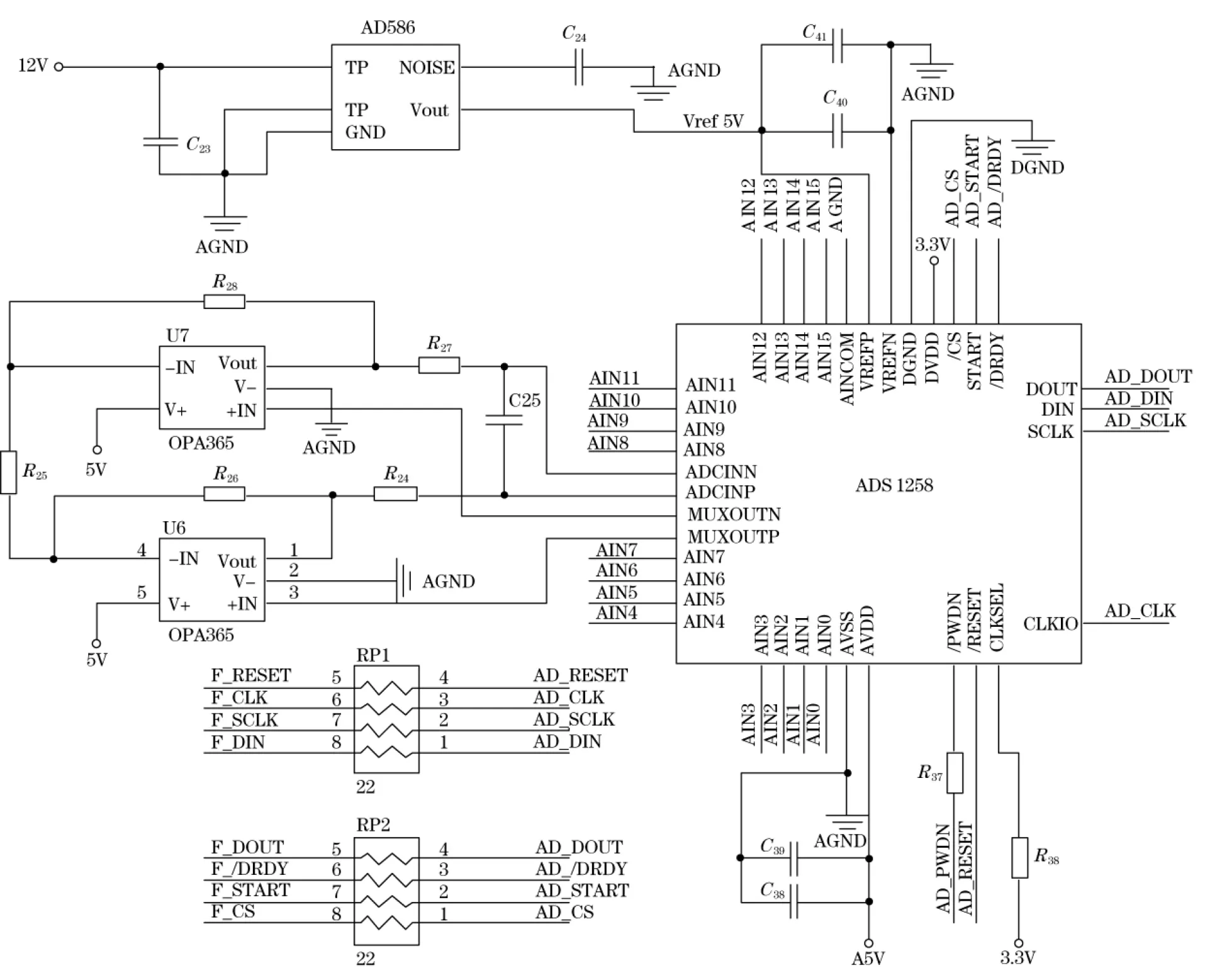

为尽量减小信号反射,本设计提出了合理的解决方法,因本设计各个分节点的输入阻抗都很大,故采取并联电阻法,即在总节点与分节点的AB线间并联阻抗匹配电阻,经试验表明,当负载阻抗与匹配电阻的阻抗之和等于传输线阻抗时,信号反射最小[6]。因RS485总线的通信介质是双绞线,其特性阻抗大约是120 Ω,而且由于通信传输的双向特性,总节点端和各分节点输入端分别并联一个120 Ω的匹配电阻,连接示意图如下图3所示。

2.2.2 失效保护设计

RS485总线标准设置接收器门限为 200 mV,这个值能提供比较良好的噪声抑制能力,当A比B高200 mV输出正逻辑,当B比A高为负逻辑[7]。但若总线空闲即没有任何信号驱动总线时,A与B之间压差介于-200~200 mV,这种状况会导致接收器输出状态不确定,分节点会认为是一个新的启动位,并开始读取后续的字节,因为向后不会有停止位,所以会产生一个帧的错误结果,设备不再请求总线,通信网络将进入瘫痪状态。除了AB两线压差低于200 mV情况外,开路或短路也会导致这种故障[8]。

为避免这种不确定状态,解决方法是将总线偏置在一个确定状态,即AB两线的压差大于-200 mV,将A接偏置电阻到地,B接偏置电阻到5 V,阻值选1 kΩ。具体见图3。

3 软件设计

3.1 数据采集转换模块的软件设计

上位机下发命令后,12个分节点分别接收总节点送至RS485总线的命令包,然后各自对命令包进行解析,解析分节点地址,当地址匹配不成功,则丢弃该命令,准备下一条命令的接收;当地址匹配成功,校验有效数据位和CRC码(循环冗余校验码),校验不成功,只上传一组固定数“AAH”,发送204800次,之后继续等待命令状态;校验成功,则复位转换模块内部的SPI接口,将SPI接口中的/CS引脚拉高或SCLK引脚保持不变约4096个总时钟。配置寄存器时,先发命令字,再配置寄存器,由上位机下发寄存器配置参数。配置过程由SPI接口串行输入实现,先发最高位,在/CS为低电平和SCLK为上升沿条件下,SPI的DIN引脚会将命令字与寄存器配置参数逐个送至ADS1258中,输入过程中,DOUT引脚上会输出无效的数据,不作处理。因本设计使用单端输入和自动扫描模式进行数据采集,所以仅需对ADS1258的CONFIG1、MUXSG0和MUXSG1这3个内部寄存器进行配置,其它寄存器保持默认值。其中CONFIG1寄存器用以配置数据采集系统的采样频率,最高采样频率23.739 kHz。配置MUXSG0、MUXSG1这两个寄存器时,控制字均是8位,每一位代表一个通道,16通道共16位控制字。高电平表示选中,芯片工作时就会采集转换该通道,低电平则跳过。

寄存器配置好后,将START引脚拉高,开始模数转换工作,接着判断/DRDY信号是否变为低电平,若是则表示某通道数据已转换完成,等待被读取。此时将SPI总线的/CS引脚拉低,DIN数据线上的输入输出的前3位不变,即000或者111时,以直接读取通道数据的方式取走转换好的数据。一次转换完成的数据有效位为32位,其中第一个是8位状态位,后是24位数据位,数据位的最高位代表采集量是否为正值,本设计采集的是0~5 V电压量,故最高位始终为1。转换次数达204 800次后,一次命令执行完毕,停止转换工作。芯片的16通道循环扫描周期小于700us,单通道以23.7 Ks/s的采样率工作700 μs16×23.7 Ks/s≈1次。分节点执行一次命令工作时间为204 80016×700 μs=8.96 s左右。数据采集转换模块的软件设计流程如图4所示。

3.2 通信协议设计

本系统中的通信协议分为2部分:系统通信协议;RS485总线通信协议。其中系统通信协议是下位机采集系统与上位机之间的通信约定,总线通信协议是指总分节点之间在总线上通信进行的约定。

3.2.1 系统通信协议

系统通信过程包含发送与接收2个动作。发送:开启分节点的数据采集工作;接收:命令背板,给上位机上传数据。

背板接收到下发的命令后,将命令进行解析与重新组合,若命令有效标志为“25”,背板继续识别命令要求是否为“A”,若是则下发命令到总节点直至总线上供各分节点读取。ADD的低5位为分节点的地址位,最多可设置地址为32个,但本设计只用到12个节点地址,采样频率RATE和采样通道AIN_0、AIN_1这3个字节的数据下发至指定分节点后,用以配置ADS1258模数转换芯片的CONFIG1寄存器、MUXSG0寄存器和MUXSG1寄存器。若命令有效标志为“25”且命令要求是“5”,此时背板转为接收状态,等待接收分节点发给总节点再到背板的数据包,重组后上传给上位机。系统通信协议结构如表1所示。

3.2.2 RS485总线通信协议

总节点与分节点之间用RS485总线通信,传输速率20Mb/s。因为下发的命令包与上传的数据包大小不同,所以其协议也不一样。总节点给分节点发送的命令共传输40位,命令格式中有32位有效数据位,1位起始位,4位CRC检验码及3位停止位。分节点回传的模数转换数据要求204 800组,每组数据有52位,含1位起始位、32位有效数据(8位状态位,24位数据位)、16位帧计数及3位停止位,总节点接收到数据后,通过系统协议上传到上位机,传送204 800次后,将总线置于发送状态,准备发送下一条命令。在此协议的规定下,一个节点的16个通道以23.7 Ks/s采样速率循环采样需总线速率为1 s700 μs×16×52 b=1.13 Mb/s,所以20 Mb/s传输率完全符合要求。具体总线通信协议如表2所示。

4 测试结果与分析

4.1 转换精度分析

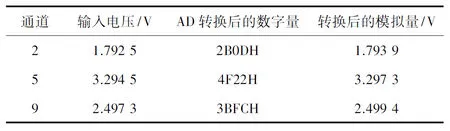

从众多通道中选取分节点8的2通道、5通道和9通道进行ADS1258转换精度分析,3个通道分别对3路直流模拟电压进行转换。

利用式(1)得出输出模拟电压值

Vo=D2n·Vref

式中:D为转换后的数字量;n为精度位数;Vref为参考电压。

由芯片24位精度可知,分母应取=8M,根据转换芯片手册建议取值为7 864 320,是因为校准后最小识别电压为1LSB=Vref/780000H=Vref/7864320。分子取值因环境干扰等因素会对数据转换精度产生一定影响,故忽略转换数字量的低8位。每路从采集结果选10个数据取平均数代入计算,分子D取平均数的高16位,因最高位是符号位,取后15位计算。参考电压为5 V。以通道2为例,去除最高位符号位与后8位得2B0DH,转成十进制为2821560,则转化成模拟输出电压为Vo= 2 821 5607 864 320 ×5≈1.793 9。各通道转换结果如表3所示。

由计算式:精度=(输出值-输入值)/输入值。

2通道采样精度:(1.793 9-1.792 5)/1.792 5=0.078%;

5通道采样精度:(3.297 3-3.294 5)/3.294 5=0.085%;

9通道采样精度:(2.499 4-2.497 3)/2.497 3=0.088%;

结果表明,各通道精度均达到了0.1%的设计精度需求。

4.2 阻抗匹配验证

在500 m传输距离条件下,输入4 V高速信号来验证分节点匹配电阻的效果。从图5中看出同一输入信号,不同匹配阻值有着不同的输出情况。负载并联60 Ω匹配电阻时,曲线有明显的滞后现象,这是因信号到末端遇阻抗突然变小,末端要消耗更多能量引发回波反射所导致;负载并联180 Ω匹配电阻,曲线有下冲现象,这是因输出信号遇阻抗突然变大,能量不能完全被吸收反射回去所导致;匹配120 Ω电阻情况下,经485总线传输后的输出与输入变化基本一致。从而验证了只有匹配电阻与负载的阻抗之和等于传输线阻抗时,即匹配120 Ω并联几MΩ负载的输入端阻抗后合并阻抗约120 Ω,恰好接近传输线120 Ω的阻抗,此时反射现象最小,信号传输效果最好[9]。

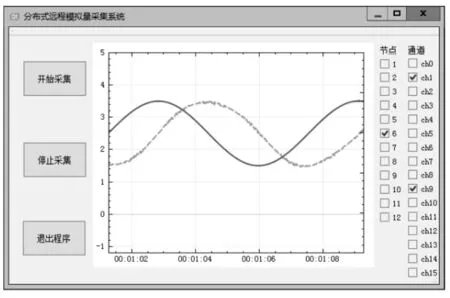

4.3 上位机读取与显示

用2.5 V中心电压、振幅为1 V的正弦波测试本设计的整体性能,此处选分节点6的通道1与通道9进行测验,在图6所示的上位机界面上,选中节点6与对应通道1、9之后,按下开始采集按钮,上位机读取采集的数据并显示出波形,从结果可以看出采集到的正弦信号波形经恢复后很光滑,没有杂波成分与畸变形态出现,说明系统在长距离传输后很平稳,有效避免了可能的外界干扰与内部阻抗因素引起的信号反射,满足分布式远程多点采集平稳传输的要求[10]。

5 结束语

本设计利用分布式总分结构思想,以FPGA,RS485总线,ADS1258为主要芯片设计出下位机,以上位机完成实时控制、存储、显示功能,可以采集大区域里的多个频率范围在1 kHz以内的交流或直流模拟信号,远距离传输具备很强的抗干扰性。设计工作弥补了目前数据采集领域的不足,在高速发展的工业领域有实用。